|        | Lecture #37                                                                                                                                                                                                                                                                                                        |            |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

|        | ANNOUNCEMENTS                                                                                                                                                                                                                                                                                                      |            |  |

| •      | Prof. King's Office Hour on Wed 11/26 changed to 3-4                                                                                                                                                                                                                                                               | 1PM        |  |

|        | <ul> <li>In order to receive extra credit for your Tutebot project, you must endow it with added functionality.</li> <li>Examples: reaction to light, heat, sound; edge avoidance; capability to "learn" where objects are (memory)</li> <li>Simply adding LEDs is not sufficient to earn extra credit!</li> </ul> |            |  |

|        | OUTLINE                                                                                                                                                                                                                                                                                                            |            |  |

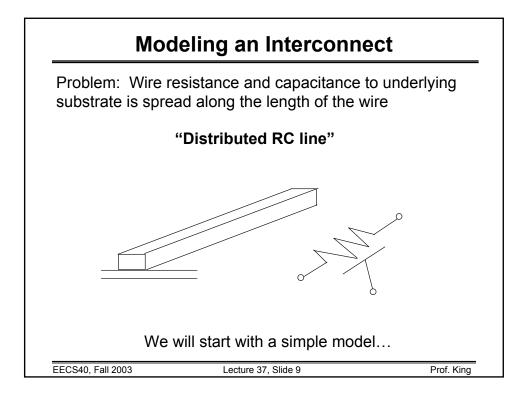

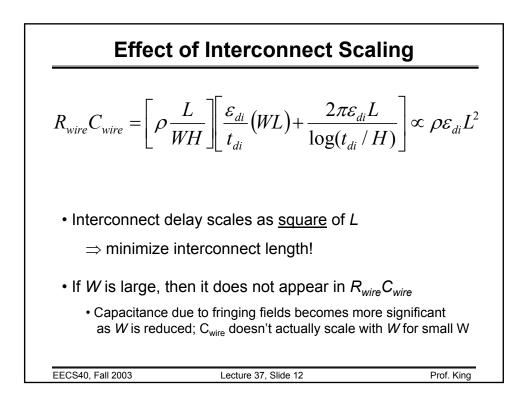

|        | » Interconnect parameters                                                                                                                                                                                                                                                                                          |            |  |

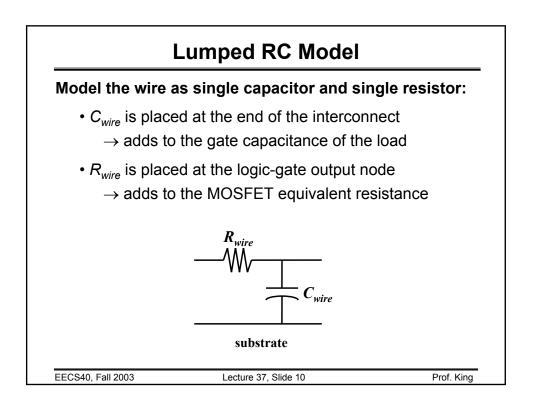

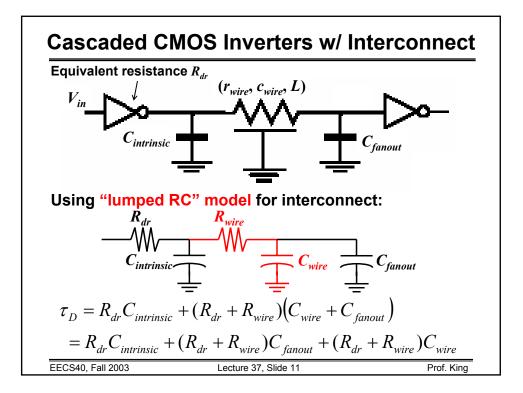

|        | » Interconnect modeling                                                                                                                                                                                                                                                                                            |            |  |

|        | <b><u>Reading</u></b> (Rabaey <i>et al</i> .)<br>Chapter 4: pp. 104-127                                                                                                                                                                                                                                            |            |  |

|        | Chapter 5: pp. 172-173                                                                                                                                                                                                                                                                                             |            |  |

| EECS40 | ), Fall 2003 Lecture 37, Slide 1                                                                                                                                                                                                                                                                                   | Prof. King |  |

|                                 | Interconnects                                                                                          |              |

|---------------------------------|--------------------------------------------------------------------------------------------------------|--------------|

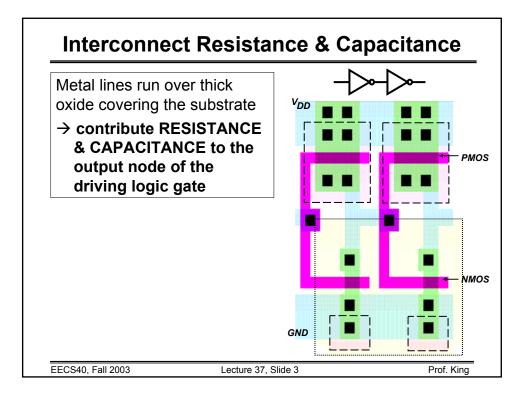

|                                 | <i>nnect</i> is a thin-film wire that ele<br>or more components in an inte                             | 5            |

| component<br>These " <b>paı</b> | cts can introduce parasitic (unw<br>s of capacitance, resistance, an<br>rasitics" detrimentally affect | ,            |

| •                               | ance ( <i>e.g.</i> propagation delay)<br>onsumption<br>/                                               |              |

|                                 | ors are scaled down in size and<br>g layers increases, the impact on<br>ncreases.                      |              |

| $\rightarrow$ Need to           | model interconnects, to evaluate                                                                       | their impact |

| EECS40, Fall 2003               | Lecture 37, Slide 2                                                                                    | Prof. King   |

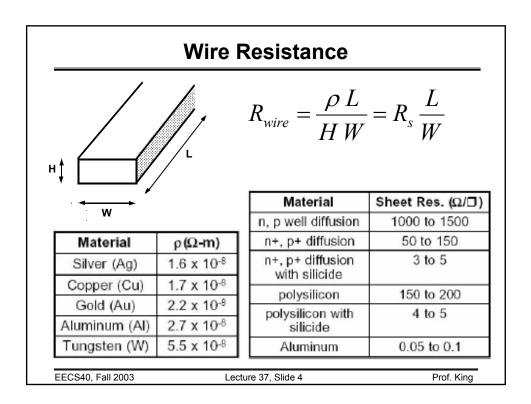

## **Interconnect Resistance Example** Typical values of $R_n$ and $R_p$ are ~10 k $\Omega$ , for W/L = 1

... but  $R_n$ ,  $R_p$  are much lower for large transistors (used to drive long interconnects with reasonable  $t_p$ )

Compare with the resistance of a  $0.5\mu$ m-thick AI wire:

R =  $\rho$  / H = (2.7  $\mu\Omega$ -cm) / (0.5  $\mu$ m) = 5.4 x 10<sup>-2</sup>  $\Omega$  /  $\Box$

<u>Example</u>:  $L = 1000 \ \mu m$ ,  $W = 1 \ \mu m$

$\rightarrow R_{wire} = R_{\Box} (L / W)$

=  $(5.4 \times 10^{-2} \Omega / )(1000/1) = 54 \Omega$

EECS40, Fall 2003

Lecture 37, Slide 5

Prof. King