#### Lecture #17 (cont'd from #16)

#### <u>OUTLINE</u>

- MOSFET I<sub>D</sub> vs. V<sub>GS</sub> characteristic

- Circuit models for the MOSFET

- resistive switch model

- small-signal model

#### Reading

- Rabaey et al.: Chapter 3.3.2

- Hambley: Chapter 12 (through 12.5)

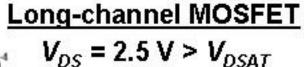

# MOSFET $I_D$ vs. $V_{GS}$ Characteristic

• Typically,  $V_{DS}$  is fixed when  $I_D$  is plotted as a function of  $V_{GS}$

# x 10<sup>4</sup> quadratic 2 0.5 1.5 $V_{GS}(V)$

#### Short-channel MOSFET

EECS40, Spring 2004

Lecture 17, Slide 2

Prof. Sanders

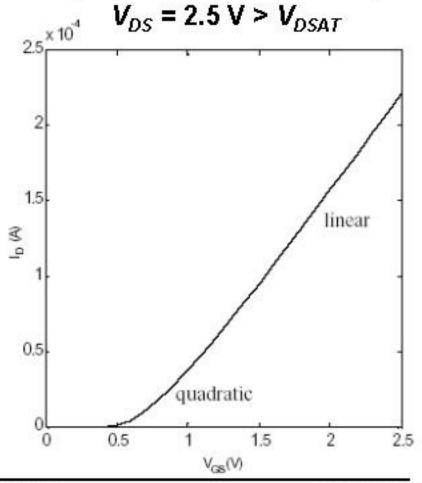

# MOSFET $V_{\tau}$ Measurement

V<sub>T</sub> can be determined by plotting I<sub>D</sub> vs. V<sub>GS</sub>, using a low value of V<sub>DS</sub>:

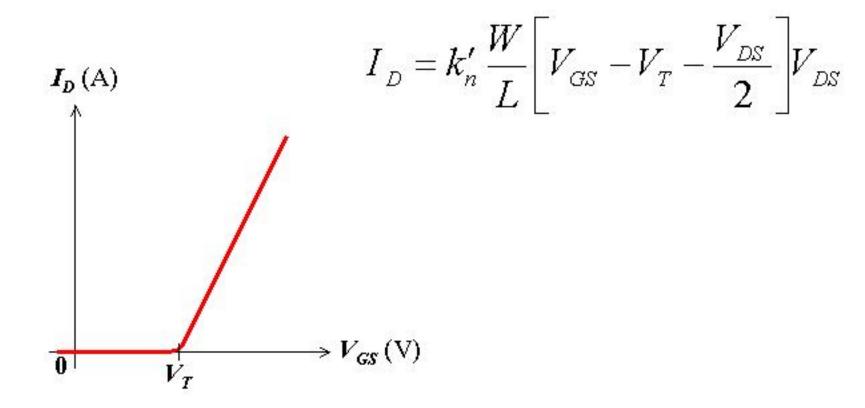

## Subthreshold Conduction (Leakage Current)

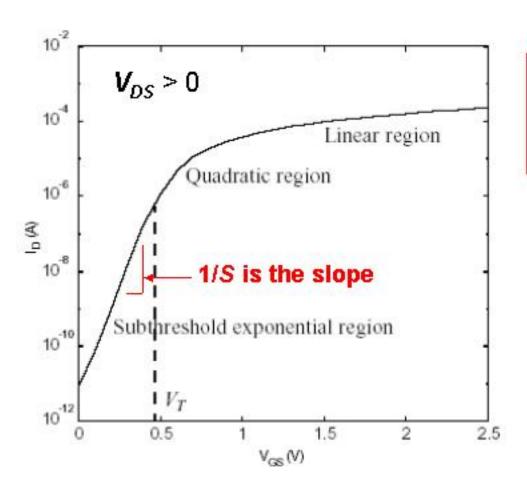

- The transition from the ON state to the OFF state is gradual. This can be seen more clearly when I<sub>D</sub> is plotted on a logarithmic scale:

- In the subthreshold (V<sub>GS</sub> < V<sub>T</sub>) region,

$$I_D \propto \exp\left(\frac{qV_{GS}}{nkT}\right)$$

This is essentially the channelsource pn junction current. (Some electrons diffuse from the source into the channel, if this pn junction is forward biased.)

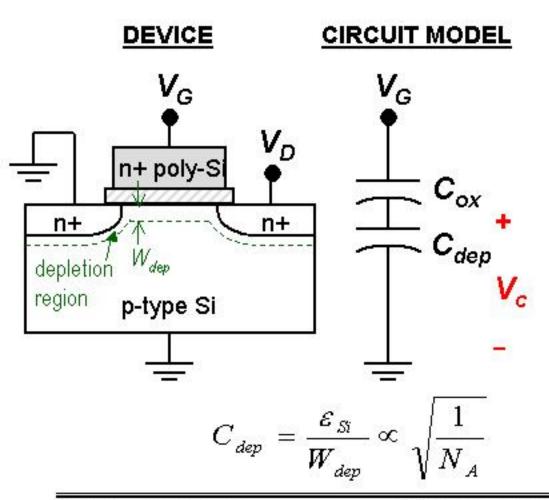

#### Qualitative Explanation for Subthreshold Leakage

The channel V<sub>c</sub> (at the Si surface) is capacitively coupled to the gate voltage V<sub>c</sub>:

Using the capacitive voltage divider formula:

$$\Delta V_c = \frac{C_{ox}}{C_{ox} + C_{dep}} \Delta V_G$$

The forward bias on the channel-source pn junction increases with  $V_G$  scaled by the factor  $C_{ox} / (C_{ox} + C_{dep})$

$$\Rightarrow n = \frac{C_{ox} + C_{dep}}{C_{ox}} = 1 + \frac{C_{dep}}{C_{ox}}$$

# Slope Factor (or Subthreshold Swing) S

S is defined to be the inverse slope of the log (I<sub>D</sub>)

vs. V<sub>GS</sub> characteristic in the subthreshold region:

$$S = n \left(\frac{kT}{q}\right) \ln(10)$$

**Units**: Volts per decade

Note that S ≥ 60 mV/dec at room temperature:

$$\left(\frac{kT}{q}\right)\ln(10) = 60 \,\mathrm{mV}$$

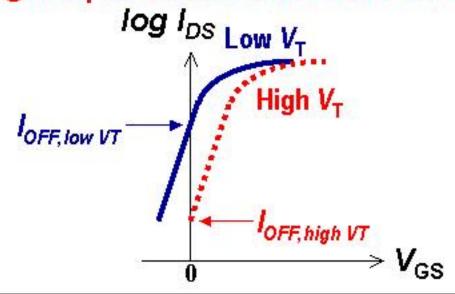

## $V_{\tau}$ Design Trade-Off

(Important consideration for digital-circuit applications)

Low V<sub>T</sub> is desirable for high ON current

$$I_{DSAT} \propto (V_{DD} - V_T)^{\eta}$$

1 <  $\eta$  < 2

where  $V_{DD}$  is the power-supply voltage

... but high  $V_T$  is needed for low OFF current

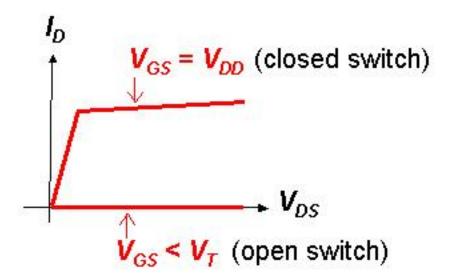

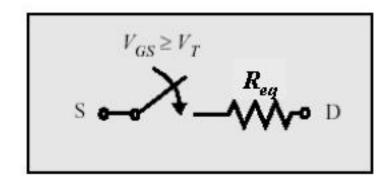

#### The MOSFET as a Resistive Switch

- For digital circuit applications, the MOSFET is either OFF (V<sub>GS</sub> < V<sub>T</sub>) or ON (V<sub>GS</sub> = V<sub>DD</sub>). Thus, we only need to consider two I<sub>D</sub> vs. V<sub>DS</sub> curves:

- the curve for V<sub>GS</sub> < V<sub>T</sub>

- 2. the curve for  $V_{GS} = V_{DD}$

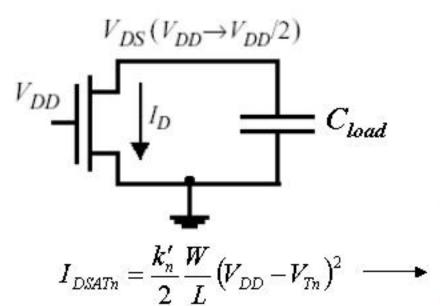

# Equivalent Resistance R<sub>eq</sub>

- In a digital circuit, an n-channel MOSFET in the ON state is typically used to discharge a capacitor connected to its drain terminal:

- gate voltage V<sub>G</sub> = V<sub>DD</sub>

- source voltage V<sub>s</sub> = 0 V

- drain voltage V<sub>D</sub> initially at V<sub>DD</sub>, discharging toward 0 V

The value of  $R_{eq}$  should be set to the value which gives the correct propagation delay (time required for output to fall to  $\frac{1}{2}V_{\square\square}$ ):

$$R_{eq} \cong \frac{3}{4} \frac{V_{DD}}{I_{DSATn}} \left( 1 - \frac{5}{6} \lambda_n V_{DD} \right)$$

#### Typical MOSFET Parameter Values

- For a given MOSFET fabrication process technology, the following parameters are known:

- $V_T (\sim 0.5 \text{ V})$

- $C_{ox}$  and k' (<0.001 A/V<sup>2</sup>)

- $V_{DSAT} (\leq 1 \text{ V})$

- $-\lambda (\leq 0.1 \text{ V}^{-1})$

Example  $R_{eq}$  values for 0.25  $\mu$ m technology (W = L):

| $V_{DD}(V)$ | 1   | 1.5 | 2  | 2.5 |

|-------------|-----|-----|----|-----|

| NMOS (kΩ)   | 35  | 19  | 15 | 13  |

| PMOS (kΩ)   | 115 | 55  | 38 | 31  |

How can Reg be decreased?

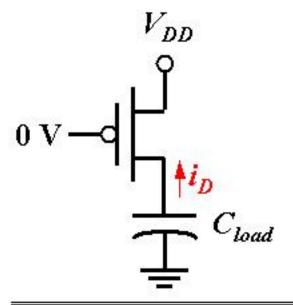

#### P-Channel MOSFET Example

- In a digital circuit, a p-channel MOSFET in the ON state is typically used to charge a capacitor connected to its drain terminal:

- gate voltage V<sub>G</sub> = 0 V

- source voltage  $V_s = V_{DD}$  (power-supply voltage)

- drain voltage  $V_D$  initially at 0 V, charging toward  $V_{DD}$

$$R_{eq} \cong \frac{3}{4} \frac{V_{DD}}{\left|I_{DSATp}\right|} \left(1 - \frac{5}{6} \lambda_p V_{DD}\right)$$

$$I_{DSAT} = -\frac{k_p'}{2} \frac{W}{L} \left( V_{DD} - \left| V_{Tp} \right| \right)^2$$

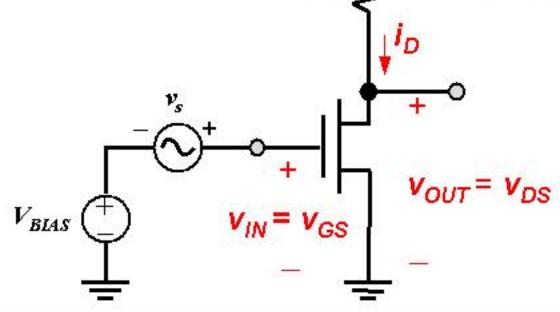

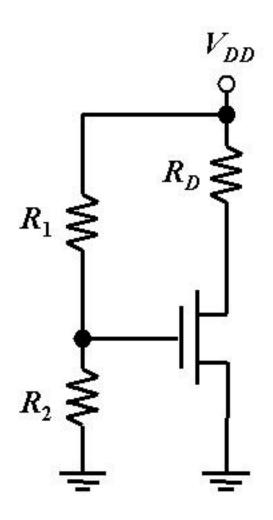

## Common-Source (CS) Amplifier

$V_{DD}$

The input voltage v<sub>s</sub> causes v<sub>Gs</sub> to vary with time, which in turn causes i<sub>D</sub> to vary.  The changing voltage drop across R<sub>D</sub> causes an amplified (and inverted) version of the input signal to appear at the drain terminal.

#### Notation

- Subscript convention:

- $V_{DS} \equiv V_D V_S$ ,  $V_{GS} \equiv V_G V_S$ , etc.

- Double-subscripts denote DC sources:

- V<sub>DD</sub>, V<sub>CC</sub>, I<sub>SS</sub>, etc.

- To distinguish between DC and incremental components of an electrical quantity, the following convention is used:

- DC quantity: upper-case letter with upper-case subscript

I<sub>D</sub> , V<sub>DS</sub> , etc.

- Incremental quantity: lower-case letter with lower-case subscript

i<sub>d</sub> , v<sub>ds</sub> , etc.

- Total (DC + incremental) quantity:

lower-case letter with upper-case subscript

i<sub>D</sub> , v<sub>DS</sub> , etc.

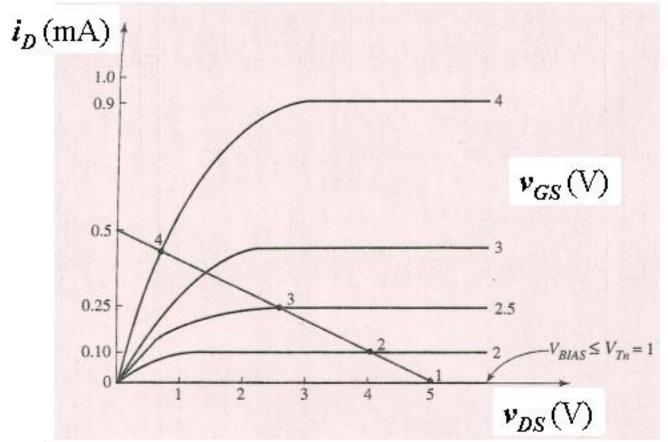

## Load-Line Analysis of CS Amplifier

The operating point of the circuit can be determined by finding the intersection of the appropriate MOSFET ip vs. vps characteristic and the load line:

#### load-line equation:

$$V_{DD} = R_D i_D + v_{DS}$$

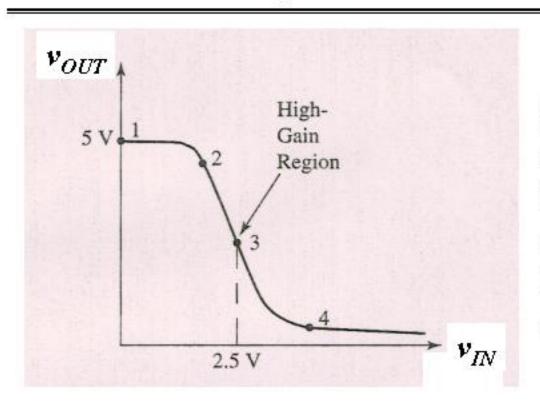

#### Voltage Transfer Function

#### Goal:

Operate the amplifier in the high-gain region, so that small changes in  $\mathbf{v}_{IN}$  result in large changes in  $\mathbf{v}_{OUT}$

- (1): transistor biased in cutoff region

- (2):  $\mathbf{v}_{IN} > \mathbf{V}_{T}$ ; transistor biased in saturation region

- (3): transistor biased in saturation region

- (4): transistor biased in "resistive" or "triode" region

#### Quiescent Operating Point

- The operating point of the amplifier for zero input signal (v<sub>s</sub> = 0) is often referred to as the quiescent operating point. (Another word: bias.)

- The bias point should be chosen so that the output voltage is approximately centered between V<sub>DD</sub> and 0 V.

- v<sub>s</sub> varies the input voltage around the input bias point.

Note: The relationship between  $v_{out}$  and  $v_{in}$  is not linear; this can result in a distorted output voltage signal. If the input signal amplitude is very small, however, we can have amplification with negligible distortion.

#### **Bias Circuit Example**

#### Rules for Small-Signal Analysis

- A DC supply voltage source acts as a short circuit

- Even if AC current flows through the DC voltage source, the AC voltage across it is zero.

- A DC supply current source acts as an open circuit

- Even if AC voltage is applied across the current source, the AC current through it is zero.

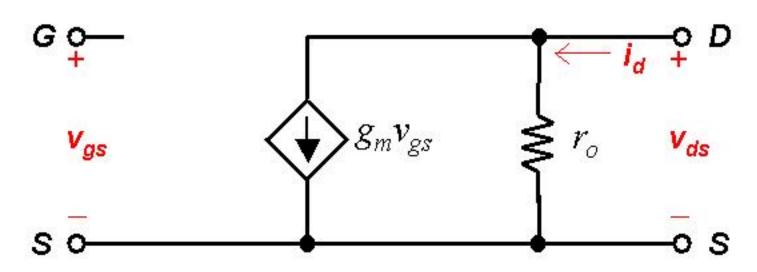

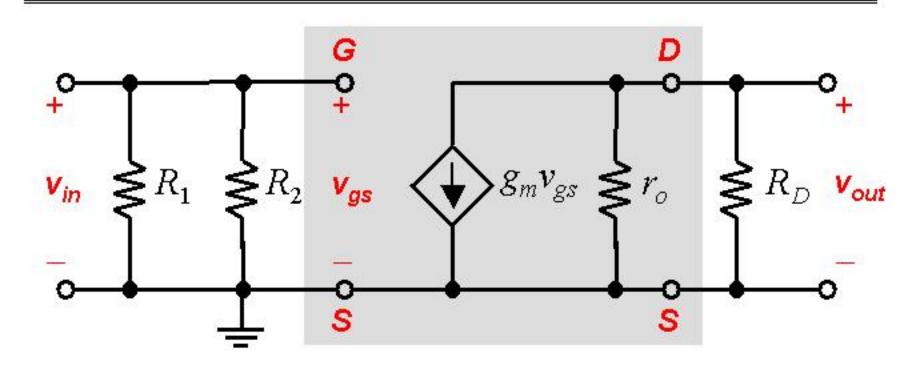

#### NMOSFET Small-Signal Model

$$i_{d} = \frac{\partial i_{D}}{\partial v_{GS}} v_{gs} + \frac{\partial i_{D}}{\partial v_{DS}} v_{ds} = g_{m} v_{gs} + g_{o} v_{ds}$$

$$g_{\scriptscriptstyle m} \equiv rac{\partial i_{\scriptscriptstyle D}}{\partial v_{\scriptscriptstyle GS}} \cong rac{W}{L} k' (V_{\scriptscriptstyle GS} - V_{\scriptscriptstyle T})$$

transconductance

$$g_o \equiv \frac{\partial l_D}{\partial v_{DG}} \cong \lambda I_D$$

output conductance

#### **Small-Signal Equivalent Circuit**

$$v_{out} = -g_m v_{gs} (r_o \parallel R_D)$$

voltage gain

$$A_{v} = \frac{v_{out}}{v_{in}} = -g_{m}(r_{o} \parallel R_{D})$$