### Lecture #26

#### **ANNOUNCEMENTS**

- Basic Tutebot demonstration due by Fri. May 7 in lab section

- Tutebot demonstration contest on Tues., May 11, 9:30-11am, 10 Evans – possible extra credit for strong efforts. Class staff will judge.

#### **OUTLINE**

- Interconnect modeling

- Propagation delay with interconnect

- Inter-wire capacitance

- Pi model for capacitive coupling

- Coupling capacitance effects

- loading

- crosstalk

#### Reading (Rabaey et al.)

Chapter 4: Secs. 4.1-4.4.4; Chapter 5: pp. 212-213

### Interconnects

- An interconnect is a thin-film wire that electrically connects 2 or more components in an integrated circuit.

- Interconnects can introduce parasitic (unwanted)

components of capacitance, resistance, and inductance.

These "parasitics" detrimentally affect

- performance (e.g. propagation delay)

- power consumption

- reliability

- As transistors are scaled down in size and the number of metal wiring layers increases, the impact of interconnect parasitics increases.

- → Need to model interconnects, to evaluate their impact

### Interconnect Resistance & Capacitance

Metal lines run over thick oxide covering the substrate

→ contribute RESISTANCE & CAPACITANCE to the output node of the driving logic gate

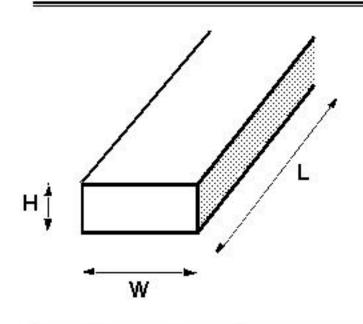

### Wire Resistance

| R    | _ | $\rho L$ | R           | L              |

|------|---|----------|-------------|----------------|

| wire |   | HW       | $r - r c_s$ | $\overline{W}$ |

| Material      | ρ(Ω-m)                 |

|---------------|------------------------|

| Silver (Ag)   | 1.6 x 10 <sup>-8</sup> |

| Copper (Cu)   | 1.7 x 10 <sup>-8</sup> |

| Gold (Au)     | 2.2 x 10 <sup>-8</sup> |

| Aluminum (Al) | 2.7 x 10 <sup>-8</sup> |

| Tungsten (W)  | 5.5 x 10 <sup>-8</sup> |

| Material                          | Sheet Res. (Ω/□) |

|-----------------------------------|------------------|

| n, p well diffusion               | 1000 to 1500     |

| n+, p+ diffusion                  | 50 to 150        |

| n+, p+ diffusion<br>with silicide | 3 to 5           |

| polysilicon                       | 150 to 200       |

| polysilicon with<br>silicide      | 4 to 5           |

| Aluminum                          | 0.05 to 0.1      |

## Interconnect Resistance Example

Typical values of  $R_n$  and  $R_p$  are ~10 k $\Omega$ , for W/L = 1

... but  $R_n$ ,  $R_p$  are much lower for large transistors (used to drive long interconnects with reasonable  $t_p$ )

Compare with the resistance of a  $0.5\mu$ m-thick Al wire:

R<sub>□</sub> =

$$\rho$$

/ H = (2.7  $\mu\Omega$ -cm) / (0.5  $\mu$ m) = 5.4 x 10<sup>-2</sup>  $\Omega$  /

Example:  $L = 1000 \,\mu$ m,  $W = 1 \,\mu$ m

$\Rightarrow R_{wire} = R \,(L/W)$

= (5.4 x 10<sup>-2</sup>  $\Omega$  / )(1000/1) = **54**  $\Omega$

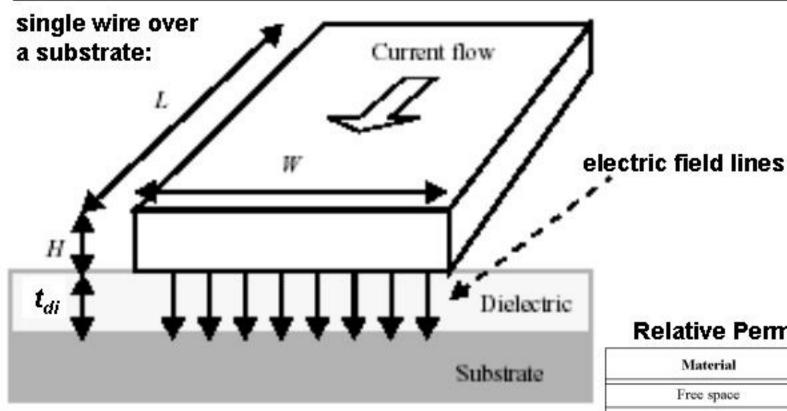

## Wire Capacitance: The Parallel Plate Model

$$C_{pp} = \frac{\varepsilon_{di}}{t_{di}} WL$$

#### Relative Permittivities

| Material                                          | ε,   |

|---------------------------------------------------|------|

| Free space                                        | 1    |

| Acrogels                                          | ~1.5 |

| Polyimides (organic)                              | 3-4  |

| Silicon dioxide                                   | 3.9  |

| Glass-epoxy (PC board)                            | 5    |

| Silicon Nitride (Si <sub>3</sub> N <sub>4</sub> ) | 7.5  |

| Alumina (package)                                 | 9.5  |

| Silicon                                           | 11.7 |

# Parallel-Plate Capacitance Example

- Oxide layer is typically ~500 nm thick

- Interconnect wire width is typically  $\sim 0.5 \mu m$  wide (1st level)

- $\Rightarrow$  capacitance per unit length = 345 fF/cm = 34.5 aF/ $\mu$ m

Example:  $L = 30 \mu m$

$\rightarrow C_{pp} \cong 1 \text{ fF (compare with } C_n \sim 2 \text{ fF)}$

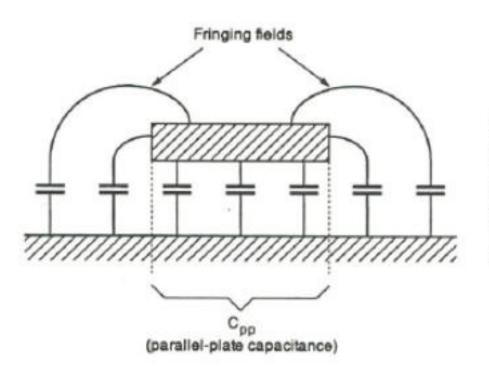

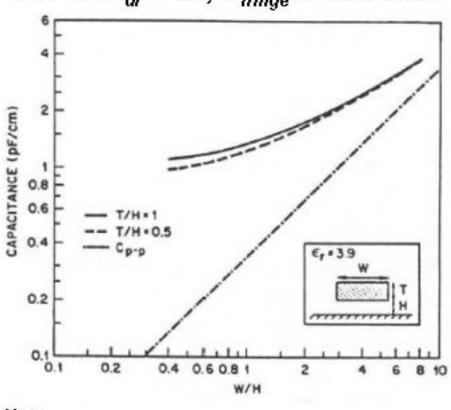

## Fringing-Field Capacitance

### Wire capacitance per unit length:

$$c_{wire} \cong c_{pp} + c_{fringe} = \frac{w \varepsilon_{di}}{t_{di}} + \frac{2\pi \varepsilon_{di}}{\log(t_{di}/H)} \qquad w$$

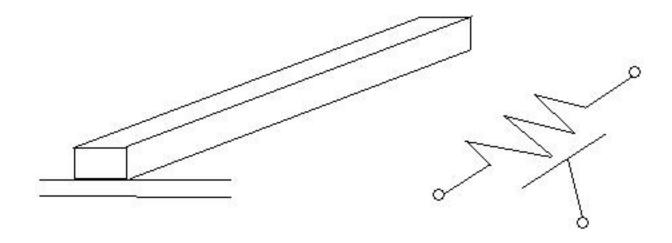

### Modeling an Interconnect

Problem: Wire resistance and capacitance to underlying substrate is spread along the length of the wire

#### "Distributed RC line"

We will start with a simple model...

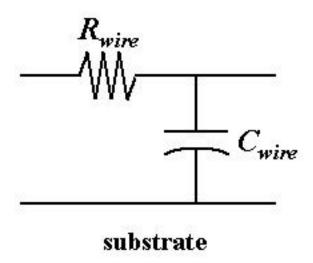

## Lumped RC Model

### Model the wire as single capacitor and single resistor:

- C<sub>wire</sub> is placed at the end of the interconnect

- → adds to the gate capacitance of the load

- R<sub>wire</sub> is placed at the logic-gate output node

- → adds to the MOSFET equivalent resistance

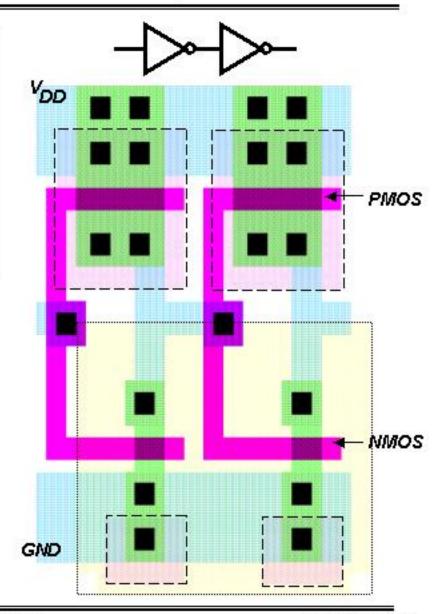

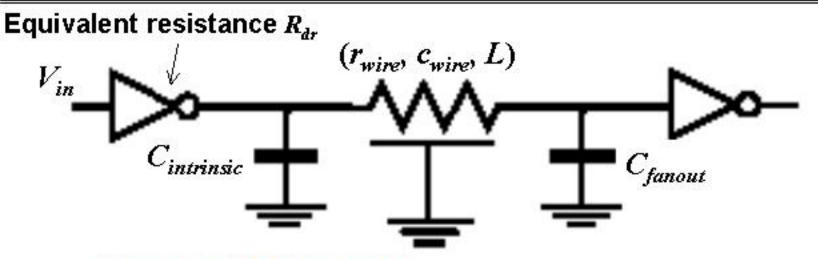

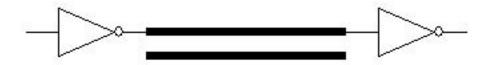

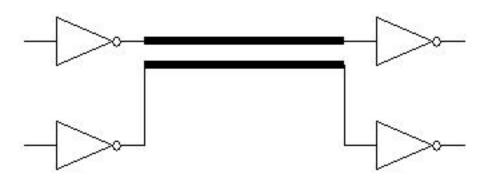

### Cascaded CMOS Inverters w/ Interconnect

### Using "lumped RC" model for interconnect:

## Effect of Interconnect Scaling

$$R_{wire}C_{wire} = \left[\rho \frac{L}{WH}\right] \left[\frac{\varepsilon_{di}}{t_{di}}(WL) + \frac{2\pi\varepsilon_{di}L}{\log(t_{di}/H)}\right] \propto \rho\varepsilon_{di}L^{2}$$

- Interconnect delay scales as <u>square</u> of L

- ⇒ minimize interconnect length!

- If W is large, then it does not appear in R<sub>wire</sub>C<sub>wire</sub>

- Capacitance due to fringing fields becomes more significant as W is reduced; C<sub>wire</sub> doesn't actually scale with W for small W

## Propagation Delay with Interconnect

#### Using the lumped-RC interconnect model:

$$\begin{split} t_p &= 0.69 \, \tau_{\scriptscriptstyle D} \\ &= 0.69 \, R_{dr} C_{intrinsic} + 0.69 (R_{dr} + R_{wire}) C_{fanout} \\ &+ 0.69 (R_{dr} + R_{wire}) C_{wire} \end{split}$$

In reality, the interconnect resistance & capacitance are distributed along the length of the interconnect.

→ The interconnect delay is actually less than R<sub>wire</sub>C<sub>wire</sub>:

$$\begin{split} t_p &= 0.69 R_{dr} C_{intrinsic} + 0.69 (R_{dr} + R_{wire}) C_{fanout} \\ &+ (0.69 R_{dr} + 0.38 R_{wire}) C_{wire} \end{split}$$

The 0.38 factor accounts for the fact that the wire resistance and capacitance are distributed.

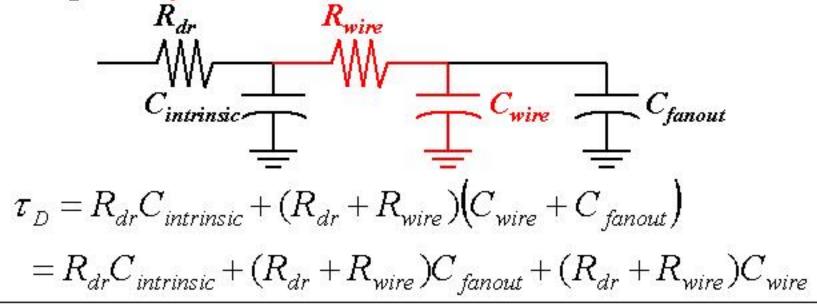

### Interconnect Wire-to-Wire Capacitance

Wire A simply has capacitance ( $C_{pp} + C_{tringe}$ ) to substrate

Wire B has additional sidewall capacitance to neighboring wires

Wire C has additional capacitance to the wire above it

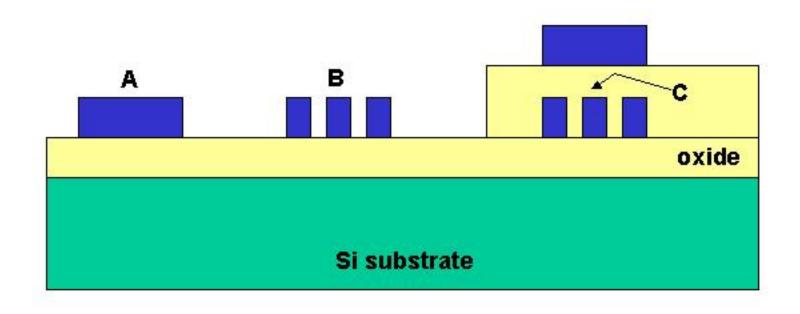

### Wiring Examples - Intel Processes

Advanced processes: narrow linewidths, taller wires, close spacing → relatively large inter-wire capacitances

EECS40, Spring 2004

Lecture 26, Slide 15

Prof. Sanders

Source: Intel Technical Journal 2002

## Effects of Inter-Wire Capacitance

- Capacitance between closely spaced lines leads to two major effects:

- Increased capacitive loading on driven nodes (speed loss)

- Unwanted transfer of signals from one place to another through capacitive coupling "crosstalk"

- We will use a very simple model to estimate the magnitude of these effects. In real circuit designs, very careful analysis is necessary.

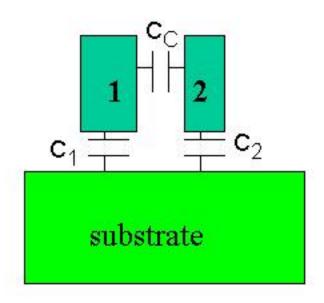

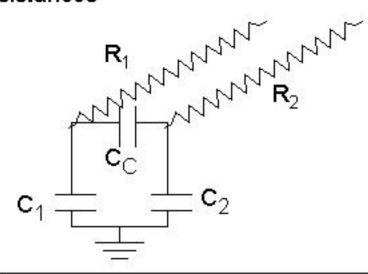

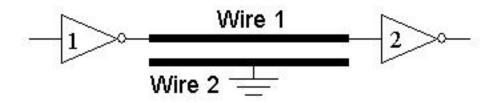

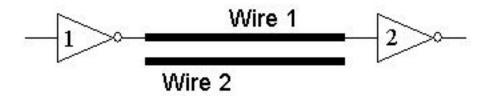

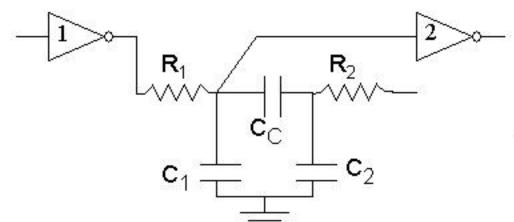

## Pi Model for Capacitive Coupling

There are three capacitances as illustrated

Using a simple lumped model for each wire we have three capacitances and two resistances

Wire 1 has resistance R<sub>1</sub>

Wire 2 has resistance R<sub>2</sub>

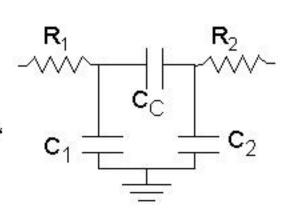

Which, when redrawn in a plane, has a "π " shape

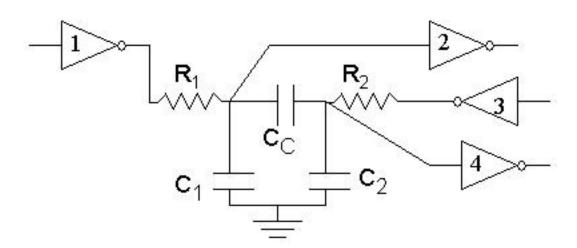

# Coupling Capacitance: Loading Effect

A) Coupling to grounded adjacent line

B) Coupling to floating adjacent line

C) Coupling to driven adjacent line

Case C is well-approximated to be the same as case A

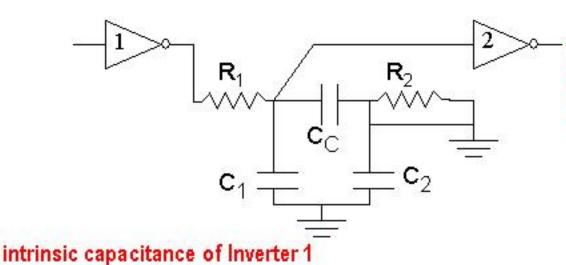

### Case A: Coupling to Grounded Line

Insert the Pi model:

C<sub>1</sub> and C<sub>C</sub> are in parallel with the input capacitance of inverter 2, C<sub>in2</sub>.

This combined C is driven by the output resistance of inverter 1 in series with the line resistance R<sub>1</sub>

$$\tau_{D} = R_{dr1}C_{out1} + (R_{1} + R_{dr1})(C_{1} + C_{C} + C_{in2})$$

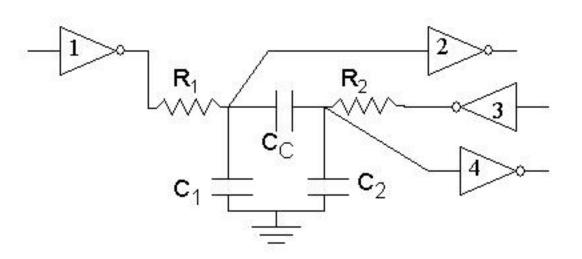

### Case B: Coupling to Floating Line

Insert the Pi model:

$C_1$  is in parallel with the series combination of  $C_C$  and  $C_2$ .

This combined C is driven by the output resistance of inverter 1 in series with the line resistance R<sub>1</sub>

$$\tau_{D} = R_{dr1}C_{out1} + (R_{1} + R_{dr1})\left(C_{1} + \frac{C_{2}C_{C}}{C_{2} + C_{C}} + C_{in2}\right)$$

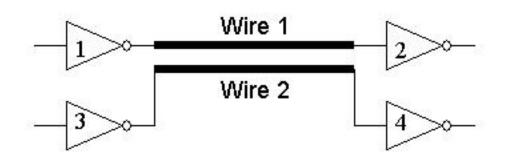

## Coupling Capacitance: Crosstalk

Signal from (1) couples to adjacent line

#### Insert Pi model:

Note that (4) receives both from (3) and from (1). The latter is undesired crosstalk.

Similarly, (2) receives signal both from (1) and from (3).

Let's assume (3) is quiet, and (1) is broadcasting...

We want to estimate the magnitude of the crosstalk signal at the input to (4).

We cannot easily treat this problem exactly (yet), but we can see that:

- The crosstalk signal is attenuated by the capacitive voltage divider C<sub>C</sub> in series with (C<sub>2</sub> || C<sub>in4</sub>).

- If C<sub>C</sub> is very large, about half the signal from (1) is coupled into (4) because of the voltage divider R<sub>1</sub>+R<sub>dr1</sub> in series with R<sub>2</sub>+R<sub>dr3</sub> where V<sub>in4</sub> is tapped off at the center.

# Approaches to Reducing Crosstalk

- Increase inter-wire spacing (decrease C<sub>C</sub>)

- 2. Decrease field-oxide thickness (decrease C<sub>C</sub>/C<sub>2</sub>)

- ...but this loads the driven nodes and thus decreases circuit speed.

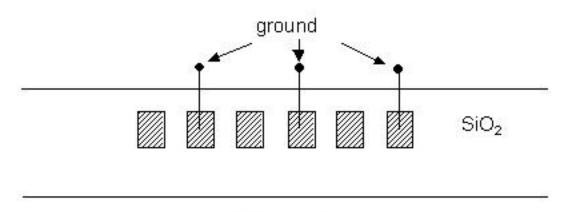

- Place ground lines (or V<sub>DD</sub> lines) between signal lines

Silicon substrate