# Supplementary Reader

# EECS 40 Introduction to Microelectronic Circuits

Prof. C. Chang-Hasnain Spring 2007

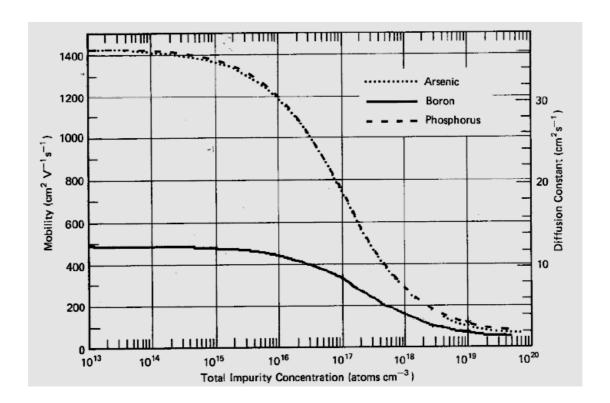

Note: This set of notes is intended to supplement the text book and not to replace it.

# **Table of Contents**

| Table of Co | ontentsi                                    |

|-------------|---------------------------------------------|

| Chapter 1.  | Bode Plots                                  |

| 1.1         | Introduction1                               |

| 1.2         | First Order Circuits                        |

| 1.2.1       | General Construction and Break Frequency    |

| 1.2.2       | Bode Magnitude Plot                         |

| 1.2.3       | Bode Phase Plot                             |

| 1.3         | Second Order Circuits                       |

| 1.3.1       | General Construction and Resonant Frequency |

| 1.3.2       | Bode Magnitude Plot                         |

| 1.3.3       | Bode Phase Plot                             |

| 1.3.4       | Definitions                                 |

| Chapter 2.  | Diode Circuits                              |

| 2.1         | Physical Behavior of Diodes                 |

| 2.2         | Solving Diode Circuits                      |

| 2.2.1       | Proof by Contradiction Approach             |

| 2.3         | Load Line Analysis                          |

| 2.4         | Zener Diodes                                |

| 2.5         | Applications for Diodes                     |

| 2.5.1       | Clipper Circuit (a.k.a. Limiter Circuit)    |

| 2.5.2       | Level Shift Circuit                         |

| 2.5.3       | Clamping Circuit (a.k.a. DC Restorer)       |

| 2.5.4       | Rectifier Circuit                           |

| 2.5.5       | Peak Detector                               |

| 2.5.6       | Voltage Doubler Circuit                     |

| 2.5.7       | Diode Logic Gates                           |

| Chapter 3.  | Semiconductor Physics                       |

| 3.1         | Introduction to Silicon                     |

| 3.1.1       | Bandgap Energy                              |

| 3.1.2       | Fermi Energy                                |

| 3.1.3       | Doping                                      |

| 3.1.4       | Doping Methods                              |

| 3.2         | Quantitative Analysis                       |

| 3.2.1       | Electric Fields 34                          |

| 322         | Electrostatic Potential 35                  |

| 3.3        | PN Junction                                                          | 35  |

|------------|----------------------------------------------------------------------|-----|

| 3.3.1      | Depletion Approximation                                              | 36  |

| 3.3.2      | PN Junction in Equilibrium                                           | 40  |

| 3.3.3      | Reverse Bias                                                         | 40  |

| 3.3.4      | Forward Bias                                                         | 41  |

| 3.4        | References                                                           | 41  |

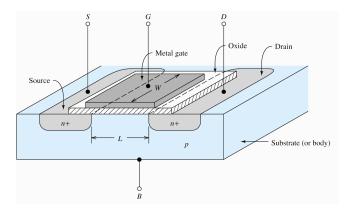

| Chapter 4. | Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)           | 43  |

| 4.1        | Introduction                                                         | 43  |

| 4.2        | Notation                                                             | 43  |

| 4.3        | NMOS and PMOS Transistors                                            | 44  |

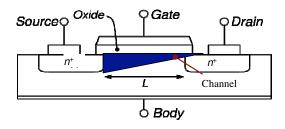

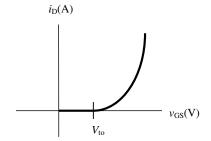

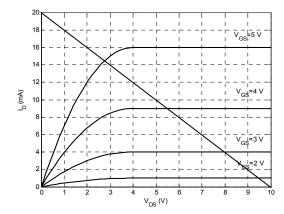

| 4.4        | N-MOSFET Operating Regions                                           | 44  |

| 4.4.1      | Cut-off                                                              | 44  |

| 4.4.2      | Triode                                                               | 45  |

| 4.4.3      | Saturation                                                           | 45  |

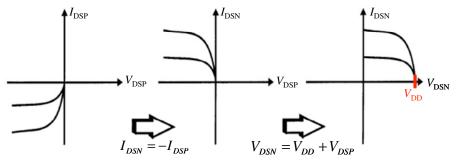

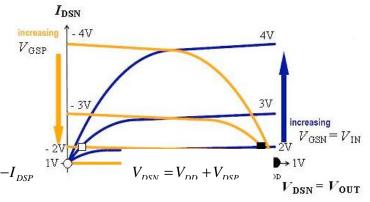

| 4.5        | PMOSFET Operating Regions                                            | 46  |

| Chapter 5. | Simple MOSFET Circuits                                               | 47  |

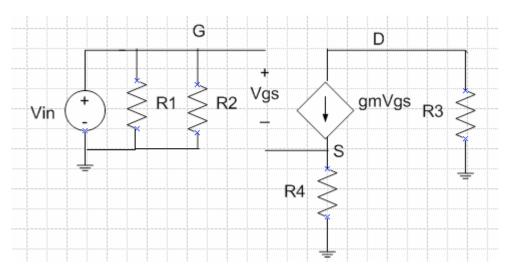

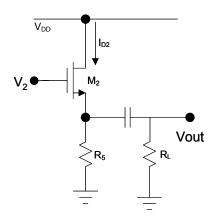

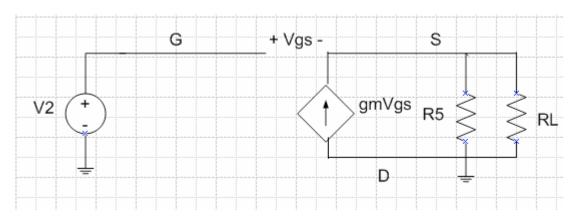

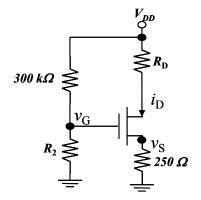

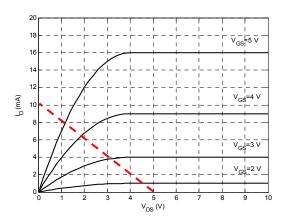

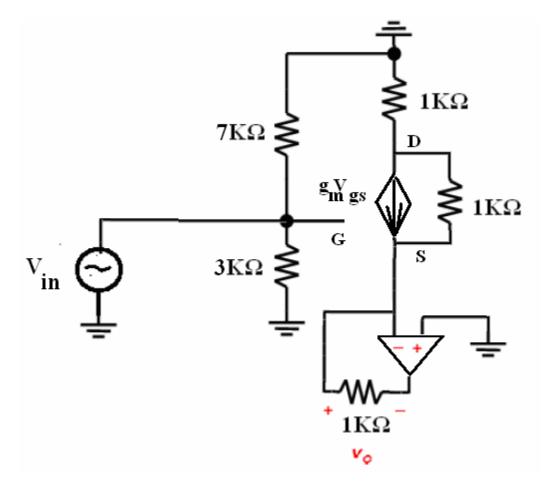

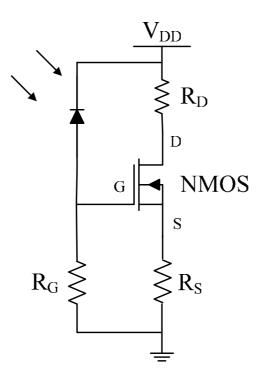

| 5.1        | Analysis for MOSFET Amplifiers                                       | 47  |

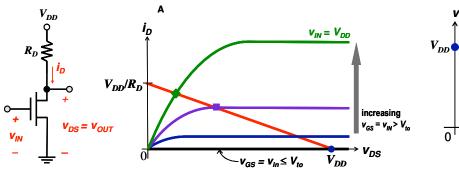

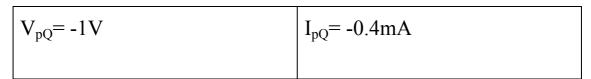

| 5.1.1      | DC Analysis – Load-Line Analysis                                     | 47  |

| 5.1.2      | Small-Signal Equivalent Circuit                                      | 47  |

| 5.1.3      | Finding Voltage Gains, Input, and Output Resistances                 | 48  |

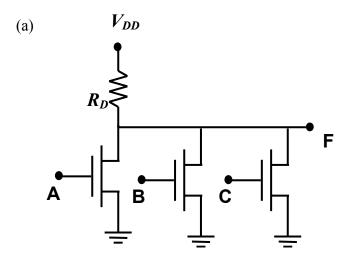

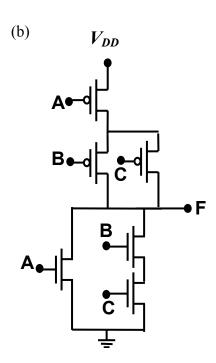

| 5.2        | The Inverter:                                                        | 48  |

| 5.2.1      | Constructing a Logic Gate: the Use of Pull-Down and Pull-Up Networks | 49  |

| 5.2.2      | NMOS Resistor Pull-Up                                                | 50  |

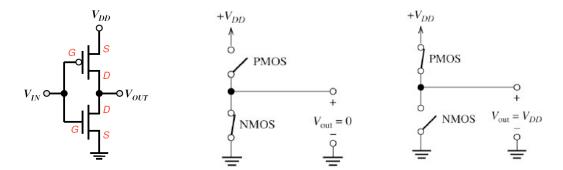

| 5.2.3      | The CMOS Inverter                                                    | 50  |

| 5.3        | 2-Input NAND Gate:                                                   | 52  |

| 5.4        | 2-Input NOR Gate                                                     | 53  |

| Doot Exame |                                                                      | 5.1 |

# Acknowledgements

We thank Abhinav Gupta, Kevin Wang, Henry Wang, and Wendy Xiao-Xue Zhao for the assistance in preparing this manuscript, and detailed editing by Isaac Seetho, Yu Ben, Timothy C Loo, Jia Zou, and Michael Krishnan.

# Chapter 1. Bode Plots

#### 1.1 Introduction

Bode plots are widely used in various fields of engineering because they characterize the magnitude and the phase response of a system. In this section, we will present step-by-step analysis to create the Bode plots of a given transfer function. We analyze the trend of the transfer function at different frequency regimes based on the value of the break or resonant frequency. This approach helps to understand the frequency behavior of the circuit, and also works for first order, second and higher order circuits.

#### 1.2 First Order Circuits

#### 1.2.1 General Construction and Break Frequency

A Bode plot illustrates the behavior of a circuit by generalizing its response into *trends* and graphing it against a log scale of frequency. Given a transfer function,  $H(\omega)$ , we may produce a magnitude and phase Bode plot. In each plot, we break down the analysis of the transfer function into 3 regimes, depending on the frequency in question:

- 1. At  $\omega = \omega_{R}$ ,

- 2. when  $\omega << \omega_R$ , or when  $\omega$  is much less than the break frequency

- 3. when  $\omega >> \omega_R$ , or when  $\omega$  is much greater than the break frequency

The break frequency,  $\omega_B$ , is a property of the filter that can be found by examining the transfer function. It describes the frequency where the trends on the Bode plot are broken, where one trend (when  $\omega << \omega_B$ ) ends and the next (when  $\omega >> \omega_R$ ) begins.

For first-order circuits, the break frequency can be found by looking solving for the frequency at which the real and complex components are equal.

#### **Example 1** – Find the Break Frequency

Given the transfer function  $H(\omega) = \frac{1}{1 + i\omega RC}$ . We find the break frequency by examining the

denominator, because it consists of two terms, 1 and  $j\omega RC$ . The first term is real and has a  $\omega^0$  dependence. The second term  $j\omega RC$  has a  $\omega^1$  dependence. The break frequency,  $\omega_B$ , occurs when the MAGNITUDE two components are equal. Thus, the break frequency for a filter with this transfer function 1

is at

$$\omega_B = \frac{1}{RC}$$

.

After finding the break frequency, we can examine the trends on either side of  $\omega_B$ . When  $\omega << \omega_B$ , the real term (in the denominator of Exp. 1) dominates and we ignore the imaginary component. When  $\omega >> \omega_B$ ,  $\omega$  dominates real term, so we work with only the imaginary term, as will be shown next.

Note: We can only disregard terms that are added and subtracted and not those that are multiplied or divided when making approximations.

Try to plug in any number you like and see if it is true.

#### 1.2.2 Bode Magnitude Plot

For the magnitude plot, we plot on the y-axis: the 'square' of the magnitude of the transfer function,  $H(\omega)$  in decibels (unit dB). This is because the transfer function describes the output to input voltage ratio. Since power is proportional to  $V^2$ , we plot  $|H(\omega)|^2$ , which in dB is:

$$|H(\omega)|_{dB} = 10 \log |H(\omega)|^{2}$$

$$= 20 \log |H(\omega)|$$

(1)

Both of these expressions can be useful, depending on the form of the transfer function. We plot  $|H(\omega)|_{dB}$  on the y-axis, against a logarithmic scale of  $\omega$  on the x-axis. One thing to keep in mind about logarithmic functions is the ability to pull multiplicative factors out, for instance:

$$20\log(A \times B) = 20\log A + 20\log B$$

$$10\log(\frac{C}{D}) = 10\log C - 10\log D$$

The key to our analysis is that we identify and examine the dominant terms of the transfer function in each of the 3 regimes in the following.

- (1) At  $\omega = \omega_B$ , we simply plug  $\omega_B$  in  $|H(\omega)|_{dB}$  and get the actual value.

- (2) When  $\omega << \omega_B$ . Examine SEPERATELY in the numerator and denominator all terms containing  $\omega$  (e.g.  $\omega^0$ ,  $\omega^1$ ). The one with the lowest power (e.g.  $\omega^0$ ) dominates in this frequency range. Hence we keep only the dominating term, one each for the numerator and denominator, respectively. The resulting formula will be used to determine the asymptotic behavior, or "trend".

- (3) When  $\omega >> \omega_B$ . Again, we examine the numerator and denominator separately. Leave only the term with the highest power ( $\omega^1$  in the previous example), one each for numerator and dominator. The resulting formula will be used to determine the asymptotic behavior, or "trend".

By analyzing these three regimes, we can construct the magnitude Bode plot. We start at the break frequency,  $\omega = \omega_B$ , and then plot the trends for  $\omega << \omega_B$  and  $\omega >> \omega_B$ .

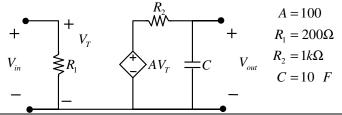

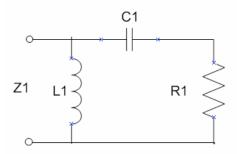

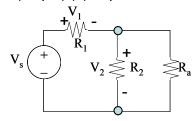

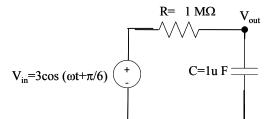

Example 2 – Find the Transfer Function,  $H(\omega)$ , and plot the magnitude Bode Plot.

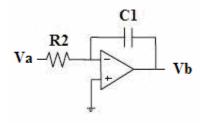

Given the following circuit, construct the magnitude Bode plot.

We can see

$$V_T = V_{in}$$

By voltage divider, we have:  $V_{out} = \frac{Z_c}{Z_c + R_2} A V_{in}$  where  $Z_c = \frac{1}{i \omega C}$

Thus, the transfer function is given by:

$$H(\omega) = \frac{V_{out}}{V_{in}} = \frac{Z_c}{Z_c + R_2} A$$

$$= \frac{1/j\omega C}{1/j\omega C + R_2} A = \frac{A}{1+j\omega R_2 C}$$

The magnitude plot will be the transfer function in dB, or:

$$|H(\omega)|_{dB} = 20\log|H(\omega)|$$

$$= 20\log\left|\frac{A}{1+j\omega R_2 C}\right|$$

Plotting this function would yield the exact behavior of our filter, but we only need the asymptotic behavior for the Bode plot. Now we begin a 3-part analysis.

#### Step 1: Break Frequency

Setting equal the real and imaginary components in the denominator, we find the break frequency:

$$\omega_B = \frac{1}{R_2 C} = \frac{1}{(1 \text{ k}\Omega)(10 \text{ \muF})}$$

$$= \frac{1 \text{ rad}}{10^{-2} \text{ s}} = 100 \text{ rad/s}$$

#### **Step 2: Asymptotes**

(1) At

$$\omega = \omega_B$$

,

$|H(\omega_B)|_{dB} = 10\log\left|\frac{A}{1+j}\right|^2 = 10\log\left(\frac{A}{\sqrt{2}}\right)^2 = 10\log\left(\frac{A^2}{2}\right)$

$$= 20\log A - 10\log 2 = 20\log A - 3dB$$

With A = 100,  $|H(\omega_B)|_{dB}$  = 37 dB. The first line of the above steps shows that at  $\omega_B$ , the output is at half the maximum power (-3dB is half in linear scale); the transfer function (voltage) has a value of  $A/\sqrt{2}$ , and power is proportional to the square of voltage. The break frequency for a first-order circuit is also referred to as the half-power frequency, where the output is one-half the maximum power. The factor of 1/2 in the logarithm can be expanded out to -20 log 2:

$$10\log\left(\frac{1}{2}\right) = 10\log 1 - 10\log 2 = 0 - 10\log 2 \cong -3 \,\mathrm{dB}$$

The half-power frequency is -3dB below the maximum power, so we also call  $\omega_B$  the -3dB frequency.

(2) For  $\omega << \omega_B$ , the constant 1 dominates in the denominator and is the only term to be kept.. The transfer function can be approximated as:  $H(\omega) \cong \frac{A}{1+0} = A$

which is purely real, so  $|H(\omega)|_{dB} = 20 \log A$  and  $|H(\omega)| = |A| = A$

Substituting the gain factor, A = 100, we obtain  $|H(\omega)|_{dB} = 20\log 100 = 20 \times 2 = 40 \text{ dB}$ .

(3) Next, for  $\omega > \omega_B$ , the  $\omega$  term dominates in the denominator term, and the transfer function can be approximated as:

$$H(\omega) \cong \frac{A}{j\omega R_2 C}$$

$$|H(\omega)|_{dB} = 20\log\left|\frac{A}{j\omega R_2 C}\right| = 20\log\left|\frac{A}{R_2 C}\right| - 20\log|j\omega|$$

$$= 20\log\frac{A}{R_2 C} - 20\log\omega = C' - 20\log\omega$$

In the asymptote, the filter's magnitude decreases at a rate of 20 dB/decade (a 10x increase in  $\omega$ ). Here C' is a constant and we can simply connect the curve for  $\omega > \omega_B$  with the point  $|H(\omega_B)|_{dB} = 37$  dB. The magnitude  $|H(\omega_B)|_{dB}$  decreases by 20 dB at  $10 \omega_B$ , 40 dB at  $100 \omega_B$ , and so on.

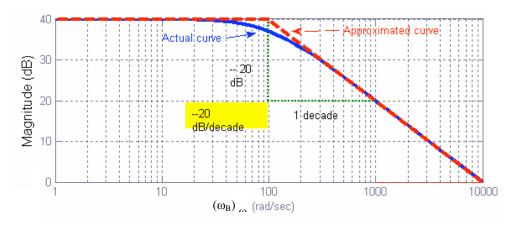

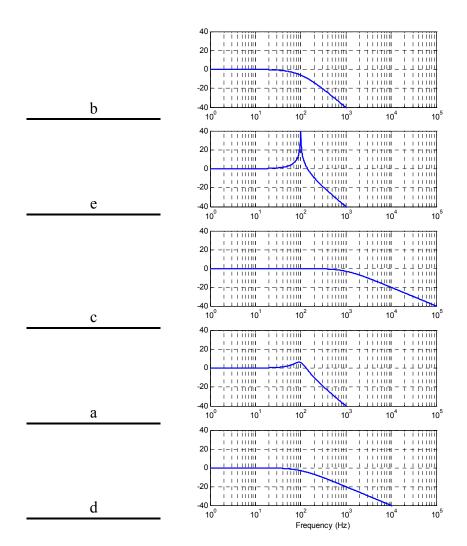

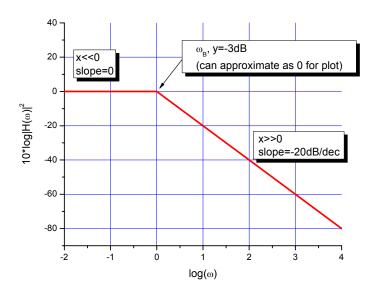

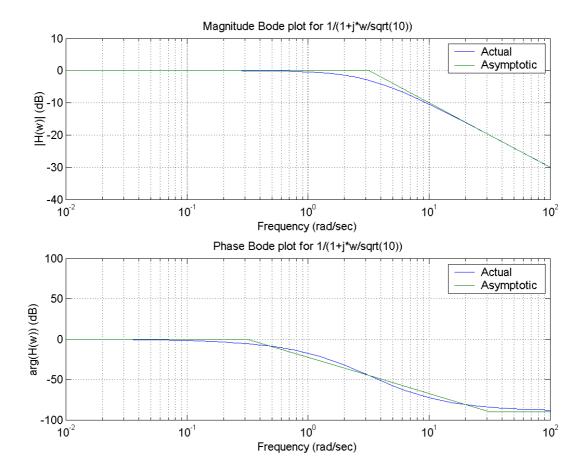

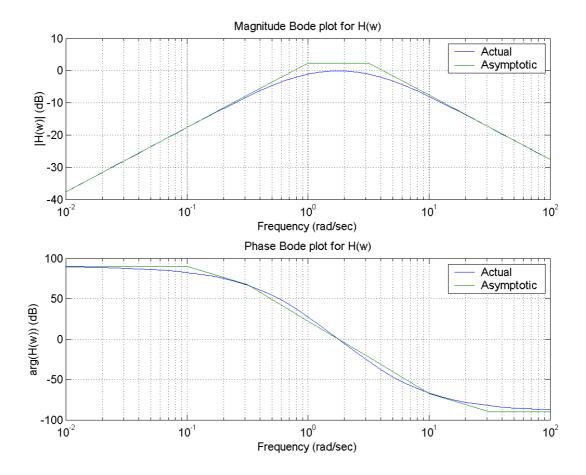

With these three regions analyzed, the magnitude Bode plot is complete and shown in Fig. 1.

Fig. 1. Magnitude Bode Plot for  $H(\omega)$  of Example 2, with the gain factor A = 100.

The dotted straight lines in Fig. 1. form the Bode plot. Note how it approximates the behavior of the actual function, shown in blue.

NOTE: This is an example of low-pass filter. The low frequencies are kept by the filter and the high frequencies are filtered out. First-order circuits are either high-pass or low-pass filters.

#### Exercise 1:

What if the voltage across the resistor  $R_2$  (Example 2) is taken as the output? Is the total energy conserved in each frequency?

#### 1.2.3 **Bode Phase Plot**

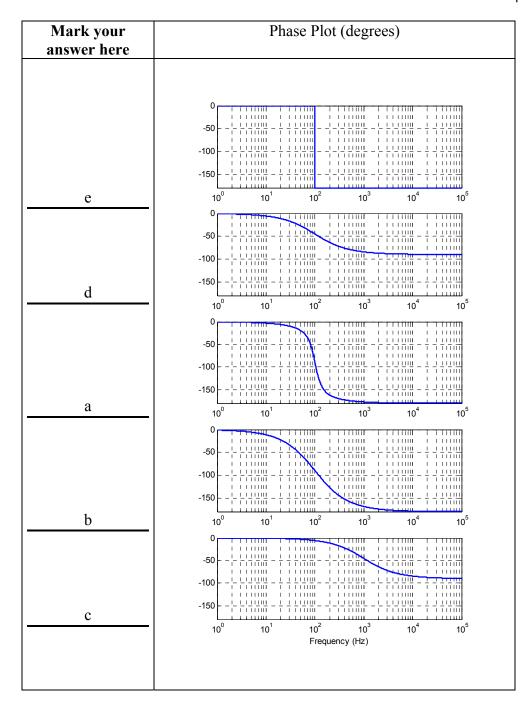

The Bode phase plot is constructed in a similar manner to the magnitude plot except we use limits (instead of trends). We first find the expression for phase,  $\angle H(\omega)$ , from the transfer function,  $H(\omega)$ . For  $\omega << \omega_R$ , we take the limit of  $\angle H(\omega)$  as  $\omega \to 0$ . At  $\omega = \omega_R$ , we use the complete expression for  $\angle H(\omega)$ , as both the real and imaginary components have equal magnitude. For  $\omega >> \omega_R$ , we find the phase by taking the limit of  $\angle H(\omega)$  as  $\omega \rightarrow \infty$ . We then construct the Bode phase plot by performing the following:

Plot lower-frequency limit value (from x  $\omega << \omega_R$  to  $\omega_B/10$ ),

Plot upper-frequency limit value (from  $x=10\omega_B$  to  $\omega \rightarrow \infty$ )

Plot the value for  $\omega = \omega_R$

Connect the extremes by curve (arctan) lines.

Example 3 – Find the Phase,  $\angle$ , of a Transfer Function,  $H(\omega)$

Using the transfer function of Example 2,

$$H(\omega) = \frac{A}{1 + j\omega R_2 C}$$

We find the net phase,  $\angle H(\omega)$ , by subtracting the phase of the denominator from the phase of the numerator:

$\angle H(\omega) = 0 - \tan^{-1} \left( \frac{\omega R_2 C}{1} \right)$  $=-\tan^{-1}(\omega R_2C)$

To plot the expression for phase in Exp. 3, we examine our 3 regions. Taking the limit of  $\angle H(\omega)$  as  $\omega \rightarrow 0$ , we find the lower-frequency asymptote,  $\omega << \omega_R$ .

$$\lim_{\omega \to 0} \angle H(\omega) = -\tan^{-1}(0) = 0$$

The upper-frequency asymptote,  $\omega >> \omega_R$  is found by taking the limit as  $\omega \to \infty$ :

$$\lim_{\omega \to \infty} \angle H(\omega) = -\tan^{-1}(\infty) = -90 \quad or -\frac{\pi}{2}$$

$\lim_{\omega\to\infty} \angle H(\omega) = -\tan^{-1}(\infty) = -90 \quad or -\frac{\pi}{2}$  At the break frequency,  $\omega_B = \frac{1}{R_2C}$ , we find the phase to be:

$$\angle H(\omega_B) = -\tan^{-1}(1) = -45 \text{ or } -\frac{\pi}{4}$$

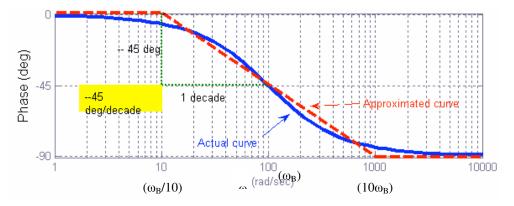

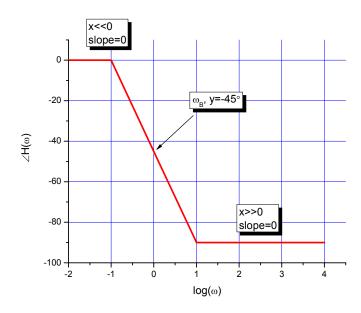

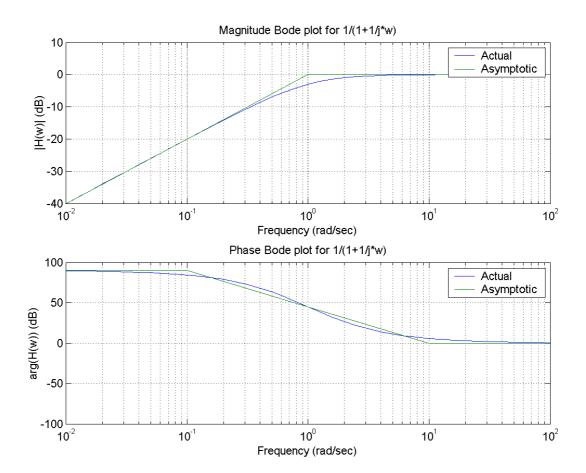

This value is in agreement with a line drawn between the upper and lower asymptotes;  $\omega_R$  is halfway between  $\omega_B/10$  and  $10\omega_B$ , and  $-45^\circ$  is halfway in between  $0^\circ$  and  $90^\circ$ . The phase Bode plot of Exp. 3 is shown in Fig. 2.

Fig. 2. Phase Bode Plot for  $H(\omega)$  of Example 2.

As before, the dotted lines in Fig. 2 outline the phase Bode plot for our transfer function, but the actual values are shown by the solid line. Note that with our approximation, in the intermediate region between  $\omega_B/10$  and  $10\omega_B$ , the phase decreases by 45 degrees per decade of angular frequency, and outside this region, the phase is constant (the asymptote).

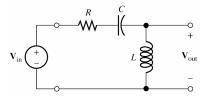

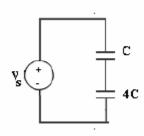

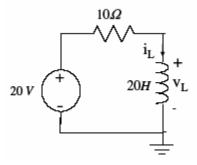

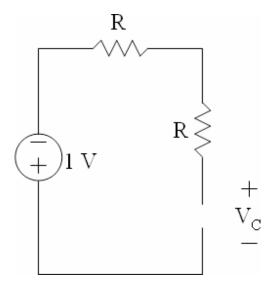

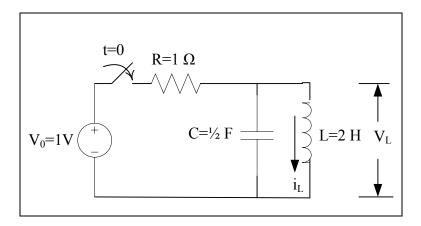

**Exercise 2:** Find the Transfer Function,  $H(\omega)$ , and plot Bode magnitude and phase plots for (a)  $V_{out}=V_L$  and (b)  $V_{out}=V_R$ . In both cases, do we have high-pass or low-pass filters?

#### 1.3 Second Order Circuits

#### 1.3.1 General Construction and Resonant Frequency

As with Bode Plots for first-order circuits, the transfer function for second-order circuits can be found by writing an equation relating  $V_{out}$  and  $V_{in}$ . Once this equation is written, an expression for  $H(\omega)$  is easily obtained. You can use this transfer function to find its magnitude and phase.

Similar to first-order circuits, we depict the behavior of second-order circuits by plotting trends of the transfer function at three frequency regimes relative to a certain resonance frequency,  $\alpha$ :

- 1. At  $\omega = \omega_0$

- 2. For  $\omega << \omega_0$ , or in other words, the limit as  $\omega \rightarrow 0$

- 3. For  $\omega >> \omega_0$ , or in the limit as  $\omega \to \infty$

Around the resonant frequency, the magnitude of the transfer function  $|H(\omega)|$  changes trend and often reaches the maximum or minimum value. Though whether it reaches the maximum or minimum depends greatly on the Q value, which will be discussed next, the trend is always changed at the resonance frequency.

The resonant frequency,  $\mathcal{A}_0$ , can be found by setting the complex part of either numerator or denominator of the transfer function to zero. This is because the magnitude of a+jb reaches minimum when b=0. If we have a complex term a+jb on the numerator, by letting b=0, we reached minimum, whereas if this complex term is in the denominator, we reached maximum.

Example 4: Finding the resonant frequency

For a circuit with transfer function as  $H(\omega) = \frac{R}{j\omega L + R - j\frac{1}{\omega C}}$

What is  $\omega_{o}$ , the resonant frequency?

Solution:

The numerator is R, which has no frequency dependence term and hence irrelevant for this question. We look at the denominator. The resonant frequency is when

$$j\omega L - j\frac{1}{\omega C} = 0$$

Hence,  $\omega_o = \frac{1}{\sqrt{LC}}$

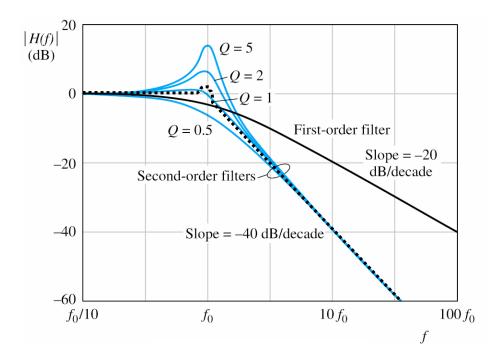

#### 1.3.2 Bode Magnitude Plot

Constructing Bode Plots for second-order circuits is the same as for first-order circuits, so analyzing trends consists of the same process mentioned earlier – finding the dominant term amongst now typically three terms  $(\omega^{-1}, \omega^0, \omega^1)$  in both numerator and denominator *separately*.

Example 5 below shows how to construct a Bode magnitude plot. Note, that in most Bode Plot problems, you will be asked the slope at which lines are ascending and descending. By using the techniques of Example 2, you will be able to answer such questions very easily.

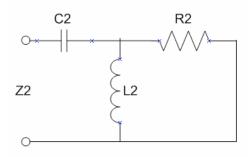

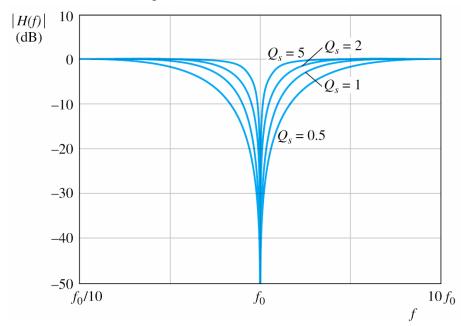

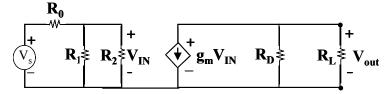

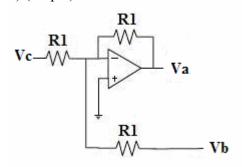

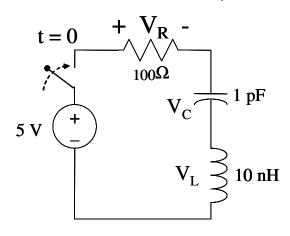

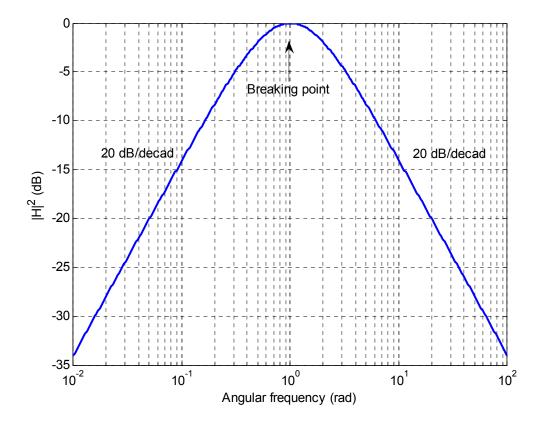

Example 5: Constructing the transfer function and Bode magnitude Plot

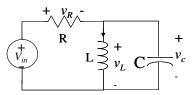

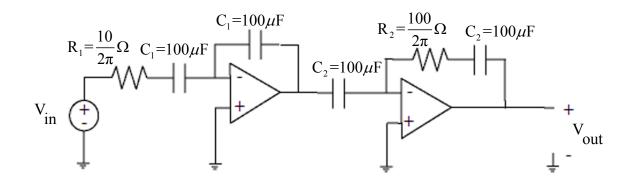

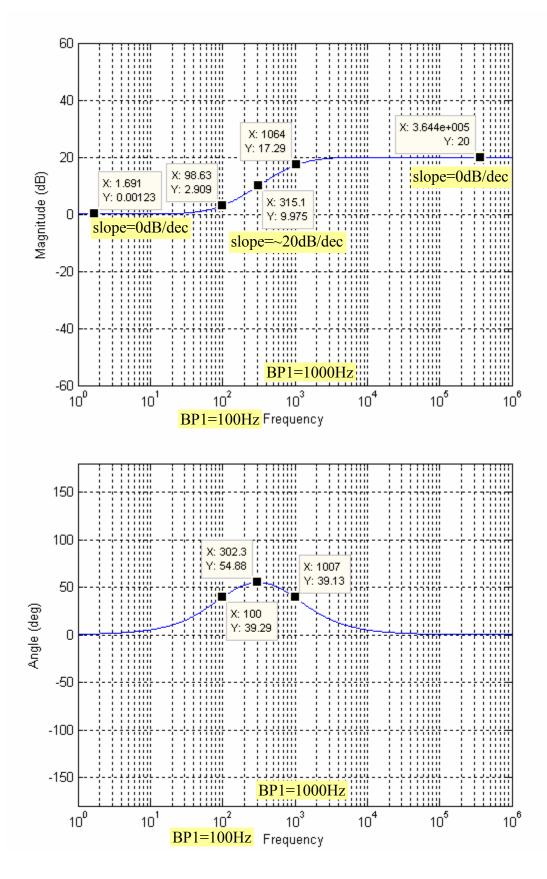

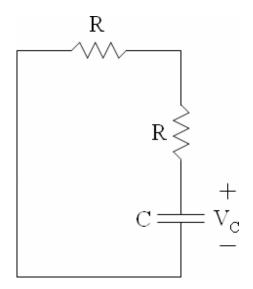

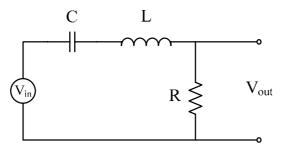

Construct the magnitude Bode Plot for the circuit shown in the diagram below. Also, label the slopes of any lines in the plot.

First, write the output voltage in terms of the values given. Notice that all the electrical components of the circuit are in series, so applying the voltage-divider technique gives the following:

$$V_{out} = \frac{j\omega L}{R + j\omega L + \frac{1}{j\omega C}} V_{in}$$

(1)

So, the transfer function becomes:

$$H(\omega) = \frac{j\omega L}{R + j\omega L + \frac{1}{j\omega C}}$$

(2)

#### **Step 1: Finding the Resonance Frequency**

The magnitude for (2) is the magnitude of the numerator divided by the magnitude of the denominator. Remembering that the magnitude for a complex number, a+bi, is  $\sqrt{a^2+b^2}$ , we obtain the following:

$$|H(\omega)| = \frac{\omega L}{\sqrt{R^2 + (\omega L - \frac{1}{\omega C})^2}}$$

(3)

This is an example that we cannot simply use the definition of  $|H(\omega)|$  reaching maximum or minimum, because we have a  $\omega$  dependence on the numerator. However, we can use the definition of breaking trends. The denominator has three terms,  $\omega^{-1}$ ,  $\omega^0$  and  $\omega^1$ . The trend is either dominated by  $\omega^{-1}$  or  $\omega^1$  at very low or high frequencies, respectively. At the resonant frequency, only the  $\omega^0$  term will dominate.

Hence,

$$\omega_0 L - \frac{1}{\omega_0 C} = 0$$

.

And  $\omega_0 = \sqrt{\frac{1}{LC}}$  (4)

Note: This resonant frequency is the same formula we got using second-order differential equation on slide 177 of EE40 Reader! (Surprise or not a surprise?)

#### Step 2: Asymptotes

Now, we must analyze this magnitude function in the three regimes mentioned above.

(1) For  $\omega \ll \omega_o$ , the numerator has only one term, so we leave it alone. For the denominator, we compare the three terms and keep only the dominant one. In this case, we will keep the  $(\omega C)^{-1}$  term.

So, we obtain the following equation:

$$|H(\omega)| = \frac{\omega L}{(\frac{1}{\omega C})} = \omega^2 LC$$

$$Or$$

$$|H(\omega)|_{dB} = 10\log(\omega^2 LC)^2 = 40\log(\omega) + 20\log(LC)$$

(5)

Note that as  $\omega \to 0$ ,  $|H(\omega)|$  goes to 0, which means that  $|H(\omega)|_{dB}$  goes to  $-\infty$ . Note that the x-axis on a Bode Plot is  $\log(\omega)$  and the y-axis is  $|H(\omega)|_{dB}$ , so equation 5 is of the form:

$$y = 40x + B$$

where B is a constant

This says that the slope of the Bode magnitude plot for  $\omega \ll \omega_o$  is 40 dB/decade.

(2) For  $\omega >> \omega_o$ , we will keep only the  $\omega L$  in the denominator of the transfer function. This gives the magnitude as:

$$|H(\omega)| = 1$$

$$OR$$

$$|H(\omega)|_{dB} = 10\log(1) = 0dB$$

(6)

This means that the output remains unchanged for large values of  $\omega$  and the slope is 0 dB/decade.

(3) At

$$\omega = \omega_{\alpha}$$

,

$$|H(\omega)| = \frac{\sqrt{(\omega_o L)^2}}{\sqrt{R^2 + (\omega_o L - \frac{1}{\omega_o C})^2}} = \frac{\sqrt{(\omega_o L)^2}}{\sqrt{R^2}} = \frac{\omega_o L}{R} = \frac{1}{\omega_o RC} = Q_S$$

$$OR$$

$$|H(\omega)|_{dB} = 20 \log(Q_S)$$

(7)

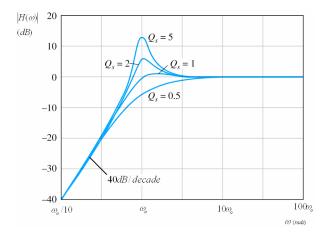

The Bode magnitude Plot for this circuit is shown below.

This is a high-pass filter which rejects low frequencies while leaving the high frequency content unchanged. Note, this is better than the first-order high-pass filter because the slope of this filter in the low-frequency region is steeper, 40dB/decade, rather than the 20dB/decade slope of the first-order filter. The increased slope provides stronger discrimination against the unwanted low frequencies.

Also note, a high value of  $Q_S$  means a large hump in the figure below. As  $Q_S$  increases, so does the value of  $|H(\omega_o)|_{dB}$ . At  $Q_S=0.5$ ,  $|H(\omega_0)|_{dB}=20\log(Q_S)=-3dB$ ; this curve resembles a first-order filter the most with only exception that the slope of filtered frequency is steeper.

Note:

$$Q_S = \frac{1}{2\varsigma}$$

(Surprise or not a surprise?)

Hence when  $Q_s=0.5$ ,  $\zeta=1$ , we have critically damped circuit.

When  $Q_s>0.5$ ,  $\zeta<1$ , we have under-damped circuit, whose signal, in the time domain, oscillates a great deal (slide 178, EE40 Reader). This can also be seen with the frequency response, we see  $|H(\omega_o)|>1$  or  $|H(\omega_o)|_{_{dB}}>0dB$ . Likewise, we have an over-damped circuit with  $Q_s<0.5$ .

*Exercise 1* Find the Transfer Function,  $H(\omega)$ , and plot Bode magnitude plot for  $V_{out} = V_C + V_R$  in Example 5. Do we have high-pass or low-pass filter? Is the energy conserved at  $\omega_0$ ?

**Exercise 2** Repeat the exercise for  $V_{out} = V_C$  in Example 5. What kind of filter is this?

**Exercise 3** Repeat the exercise for  $V_{out} = V_C + V_L$ . in Example 5. What kind of filter is this?

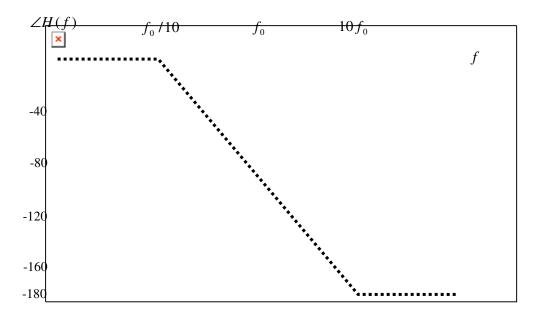

#### 1.3.3 Bode Phase Plot

Constructing the phase plot is done in a similar manner to the magnitude plot. After finding the transfer function, you can find its phase. Remember that the phase of a function is the phase of the numerator minus the phase of the denominator, and the phase of a complex number, a + bi, is  $\arctan(b/a)$ . After finding

the phase function, you must analyze the function in the same 3 regimes as was done for the magnitude plot. Follow the next example, which constructs a phase plot for the circuit in Example 2.

Example 6: Constructing the Phase Plot:

Construct the Phase Plot for the circuit shown in Example 5.

Solution:

The transfer function of example 2 is reproduced below:

$$H(\omega) = \frac{j\omega L}{R + j\omega L + \frac{1}{j\omega C}}$$

(6-1)

The phase of the above transfer equation is:

$$\angle H(\omega) = 90 - \arctan(\frac{\omega L - \frac{1}{\omega C}}{R})$$

(6-2)

Now, we must analyze this function in the same 3 regimes as before.

(1) For  $\omega \ll \omega_o$  or as  $\omega \to 0$ , we can disregard the  $\omega L$  term in the numerator of the second term since this value is approaching 0 and will not make a significant effect when added to other values. So, the above function reduces to:

$$\angle H(\omega) = 90 - \arctan(\frac{-\frac{1}{\omega C}}{R}) = 90 + \arctan(\frac{1}{\omega RC}) = 90 + \arctan(\frac{\omega_0}{\omega Q_S})$$

(6-3)

Notice that as  $\omega \to 0$ , the argument to arctan in equation 3 becomes very large, so:

$$\angle H(\omega) = 90 + 90 = 180$$

(6-4)

(2) For  $\omega >> \omega_o$  or as  $\omega \to \infty$ , in equation 2, we can disregard the  $(-1/\omega C)$  term in the numerator because it becomes very small and has a negligible effect when it is added to other values. So, equation 2 reduces to:

$$\angle H(\omega) = 90 - \arctan(\frac{\omega L}{R}) = 90 - \arctan(Q_S \frac{\omega}{\omega_0})$$

(6-5)

As  $\omega \to \infty$ , in equation 5, the argument to arctan becomes very large, so:

$$\angle H(\omega) = 90 - 90 = 0$$

(6-6)

(3) At  $\omega = \omega_a$ , equation 2 becomes:

$$\angle H(\omega) = 90 - \arctan(\frac{0}{R}) = 90$$

(6-7)

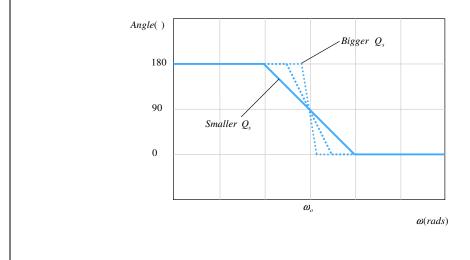

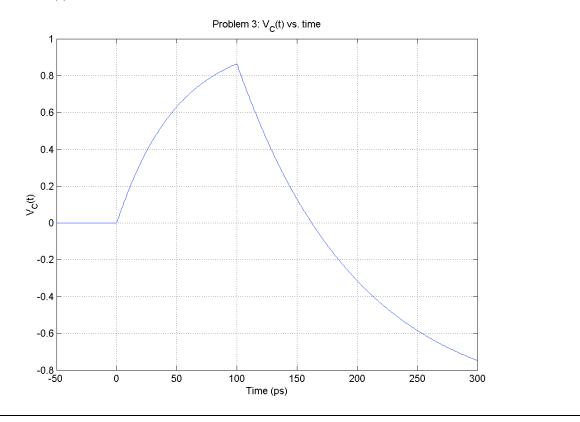

The figure below shows the phase plot for equation 2. As seen in the plot, for low frequencies, the phase completely changes, yet for high frequencies, it remains unchanged.

Note that as  $Q_S$  increases, the downward sloping line becomes steeper. This can be seen using either equation 6-3 for  $\omega < \omega_0$  and 6-5 for  $\omega > \omega_0$  respectively.

If  $Q_{\rm S}$  could reach  $\infty$ , the downward sloping line would become vertical which approaches an ideal high-pass filter.

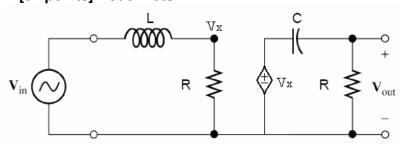

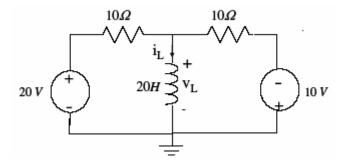

*Exercise.* Find the Transfer Function,  $\overline{H(\omega)}$ , and plot Bode magnitude and phase plots for (a)  $V_{out}=V_L$  and (b)  $V_{out}=V_R$ . In both cases, what filters do we have? Show the definition of Q is different for a parallel LC than a series LC circuit. Explain how is Q related to the damping ratio in this case.

#### 1.3.4 Definitions

Table 1. Symbol Table for  $\mathcal{Q}_o$ ,  $Q_s$  and  $Q_p$

| Symbol                                               | Definition                                                                                                                                                                         |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\omega_o = 1/\sqrt{LC}$                             | The resonant frequency is defined to be the frequency at which the impedance is purely resistive.                                                                                  |

| $Q_s = \frac{\omega_0 L}{R} = \frac{1}{\omega_0 RC}$ | The quality factor for a series resonant circuit is defined to be the ratio of the reactance of the inductance at the resonant frequency (e.g. $\omega_o L$ ) to the resistance.   |

| $Q_p = \frac{R}{\omega_0 L} = \omega_0 RC$           | The quality factor for a parallel resonant circuit is defined to be the ratio of the resistance to the reactance of the inductance at the resonant frequency (e.g. $\omega_o L$ ). |

# **Chapter 2. Diode Circuits**

#### 2.1 Physical Behavior of Diodes

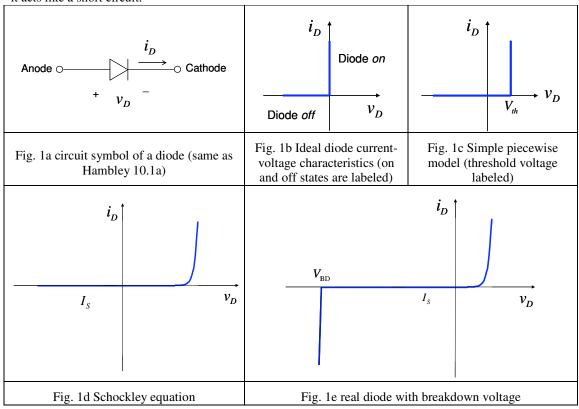

A diode is a simple two terminal device. The two terminals are labeled anode (positive side) and cathode (negative side). The diode symbol used in a circuit is shown in Fig. 1a, with the definition of the plus and minus directions of voltage and current. A positive voltage applied to the diode is referred as a forward bias and negative, a reverse bias. In this part of the course, we will introduce three models to describe the current-voltage (I-V) characteristics of a diode: the ideal diode model, a simple piecewise model and the Shockley equation.

An ideal diode has only two modes of operation: off and on, as shown in Fig. 1b. When the diode is "off", it passes through no current but the voltage can be any value less than zero. It behaves like an open circuit. When the diode is "on", the voltage is clamped at zero while its current can be any positive value. Hence, it acts like a short circuit.

The simple piecewise model is similar to the ideal diode model with "off" and "on" states being open and short circuit, respectively. The only difference is the inclusion of a threshold voltage. As shown in Fig. 1c, when the diode is biased below a certain threshold voltage, it is "off", i.e. the current passing through the diode is zero. When the diode is "on", voltage is clamped at this threshold voltage while current can be any positive value depending on the rest of the circuit. In EE 40, this threshold voltage is set to be 0.7 V. Note, this number is just a matter of convention and not based on fundamental physical laws. In this set of notes, this simple piecewise model is slightly different from the model used in section 10.5 of Hambley. This model is a simpler version of the piecewise-linear model described in 10.5, hence the name "simple piecewise model."

Shockley Equation model, shown by Fig. 1d, is more accurate than the first two. With forward bias, the current increases exponentially with voltage. For reverse bias, the current is negative and saturates at a saturation current. Since it is difficult to use this model to reach analytical solutions, for the circuits in this chapter, we use the ideal and simple piecewise model.

None of the models describe what happens when the voltage bias becomes a large but negative value, which is known as reserve bias breakdown voltage, for example, as in Zener diodes (Hambley 10.3). In the circuit analysis part of this course, we will simply add a reverse voltage as in 10.3. The physics behind the reverse breakdown phenomenon and the Shockley equation will be briefly discussed in the next Chapter. However, you will not see more detailed discussion until EE 105 and EE130, which I hope you will take next year.

Note, no matter which model you use, a diode has its I-V curve passes through the origin, i.e. with zero voltage there should be no current flow. The only exception is when unless there is an external source to generate electrons, e.g. in the case of sun light or laser beam shinning on a photodiode. In general, if we did not specifically mention photo-generation of electrons, zero voltage bias across a diode leads to zero current. Do not lose this "common sense" when dealing with diode problems.

$$I = 0 \longleftrightarrow V = 0$$

#### 2.2 Solving Diode Circuits

#### 2.2.1 Proof by Contradiction Approach

The proof by contradiction method uses guess-and-check, also discussed in the text book.

- ∞ For each diode in the circuit, "guess" an "on" or "off" state and replace it with the corresponding model (open circuit for "off", and 0.7 volt source for "on")

- ∞ If diode is assumed on, the current should flow into the positive terminal of the diode. If diode is assumed off, the voltage should be negative across the diode, i.e. reverse biased.

We apply the contra-positive of the second bullet above to contradict our guess. (If  $A \rightarrow B$ , then Not  $B \rightarrow N$ ot A) In other words, if we solve the circuit and find a negative current through an "on" diode or a voltage greater than 0.7V across an "off" diode, we guessed the wrong states.

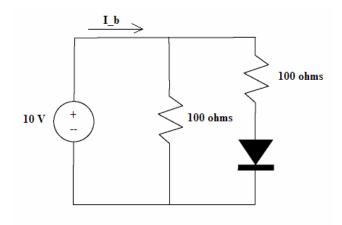

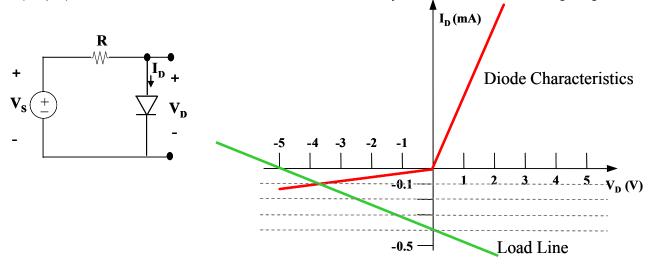

#### 2.3 Load Line Analysis

Load line analysis is simply about finding the intersection point based on the physical characteristics of a device (the load), the physical characteristics of a driving circuit, based on fundamental laws such as KCL and KVL. For our present discussion, the diode is our load, but this powerful technique can be applied to other loads as well.

From the physical behavior of a diode, we know that a diode behaves in a certain way. This presents an I-V characteristic based on the model we choose. When this diode is placed in a simple circuit, the circuit will also want to dictate the way it behaves. In particular, by KVL, the driving circuit and the load must see the same voltage at their interface. In addition, the current out of the driving circuit must match the current into the load.. For the circuit to be consistent, both of these constraints must be satisfied. Therefore, we find the intersection of the curves representing the physical characteristic of a diode and the curve representing the manner in which the diode will behave when placed in a circuit (the load's IV curve, or "load line"). We call this intersection point, the "operating point", because it is the point at which the device will operate.

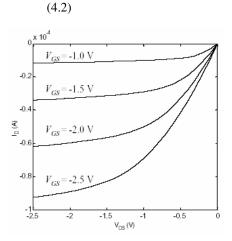

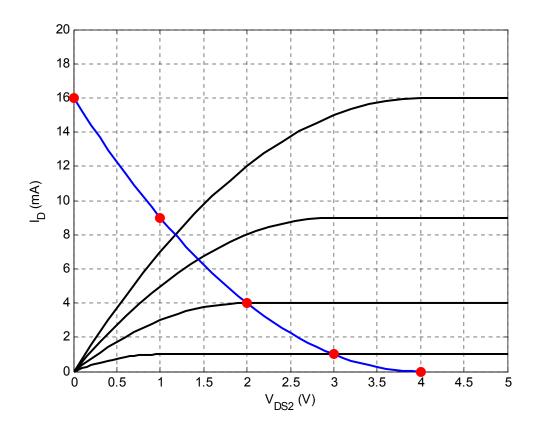

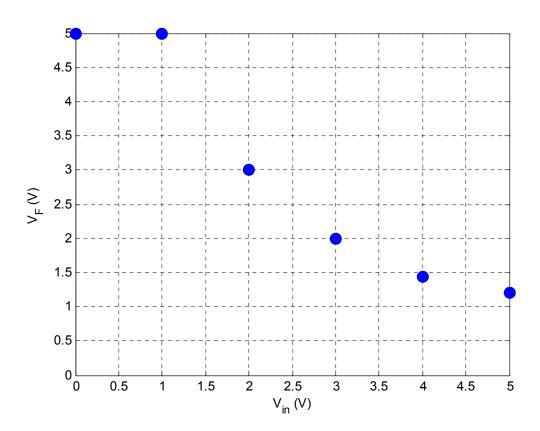

The physical characteristic of a diode (or other device) is sometimes represented by a set of family curves at different operating conditions. For example, in photodiode, two curves typically exhibit for the conditions with and without light illumination. In the case of MOSFET, characteristics are represented by  $I_{ds}$ - $V_{ds}$  at different gate voltage ( $V_g$ ) levels. But no matter how many curves are used to represent the physical characteristic of the diode, you are simply intersecting this characteristic with the behavior you obtain from analyzing the load in a circuit. Each intersection point of the characteristic and the load line indicates the Q-point in that particular condition.

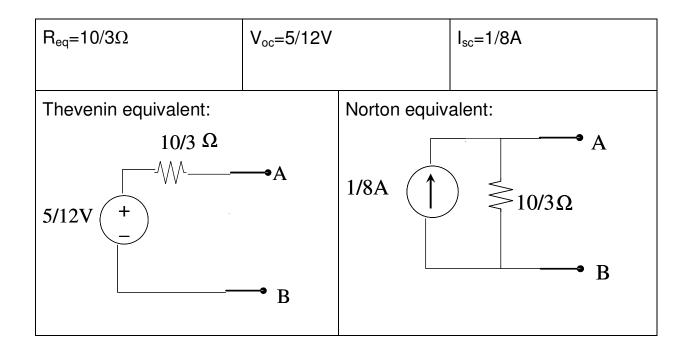

The circuit may become more complicated than a simple source, diode, and resister in series. But even in a more complicated circuit, we can simplify the problem by first finding the Thevenin equivalent circuit of the linear portion of the circuit. Then, we can resort to the fundamental KVL principle to obtain the equation for the load line.

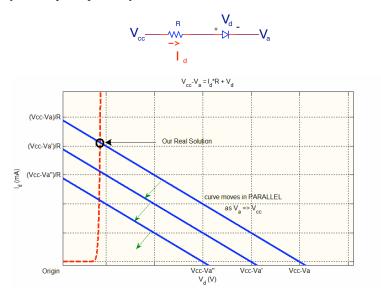

Once we find the load line equation using KVL, we can graph its I-V characteristic and find the solution from the intersection point. As shown in Fig. 2, as the source voltage is increased while keeping the

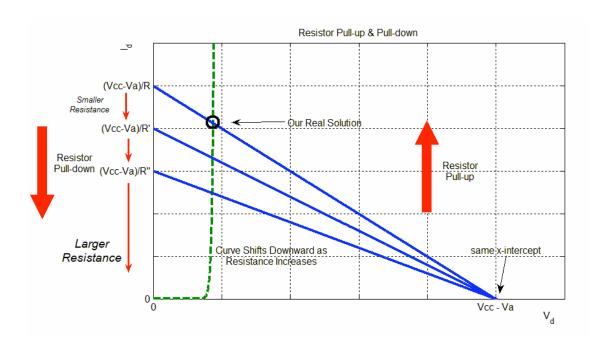

resistance constant, the load line is moved upwards in parallel to the original curve. The intersection point is changed accordingly. If, however, the value of the resistance is changed, the y-intercept of the load line is changed accordingly. When the resistance is decreased, the y-intercept increases, and the curve is pulled up with the same x-intercept. The official terminology for this upward shift due to a decrease in resistance is "resistor pull-up." Fig. 3 shows how the curve shifts downward as we increase the resistance. Because the x-intercept remains the same, the curve does not shift in parallel.

It is important to familiarize yourself with the various graphical representations of the load line because we sometimes may simply read off the values by examining the x and the y intercepts. For example, in Fig. 2, if we assume  $V_a$  is zero, then we instantly find the value of  $V_{cc}$  and R numerically by examining the x-intercept and the y-intercept, respectively.

Fig. 2. The load line is shifted in parallel, indicated by the arrow, when the parameter  $V_a$  approaches  $V_{cc}$ , assuming that the resistance is kept at a constant value. The circuit for the particular load line is shown above.

Fig. 3. The load line shifts as we vary the resistance, assuming Vcc and Va as constant. The curve does not shift in parallel because the x-intercept remains the same.

#### 2.4 Zener Diodes

In a normal diode, the "activities" occurs in the first quadrant of the I-V characteristic. In Zener diode, the "activities" occurs in the third quadrant. In Zener diode, we assume that upon a certain negative voltage, named the breakdown voltage, the magnitude of the current increases dramatically. We are not so much interested in the positive voltage regime, but rather more in how the diode will behave in the realm of negative voltage. We still apply the same technique to obtain the load line equation from the circuit.

Example 10.3 in Hambley shows the graph of a Zener diode characteristic and its load line for two different supply voltages. The motivation for using a Zener diode rather than a regular diode is the high voltage switching applications. While a regular diode provides switching behavior, the voltage involved is fairly small. With Zerner diode, voltage switching occurs on the order of magnitude of 100 V. Moreover, a very small change in the voltage induces a large change in current; therefore, the resistance is very small by Ohm's Law, as the slope of the Zener diode characteristic is fairly large.

#### 2.5 Applications for Diodes

The widespread applications for diode include, but are not limited, to the following:

- ∞ AND/OR gate

- ∞ Half & full wave rectifier

- ∞ Clamping circuit

- ∞ Clipper circuit

- ∞ Peak detector

- Level shift

- ∞ Voltage doubler

In the following section, I will discuss each application separately and briefly.

#### 2.5.1 Clipper Circuit (a.k.a. Limiter Circuit)

To begin the analysis of clipper circuit, we present two basic forms. In each of the two forms, we will examine the transfer characteristic, namely the output voltage as a function of input voltage, and the output voltage as a function of time.

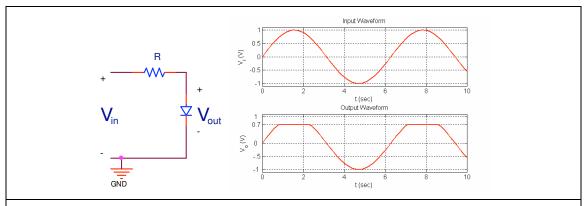

The first basic form is shown in Fig. 4. We will use the simple piecewise 0.7 model in our analysis.

If the input is less than 0.7 V, the diode is off, the output voltage will be equal to the input voltage because the diode is an open circuit. The slope of the transfer characteristic curve for input less or equal to 0.7 V will have a slope of 1. If the input is greater than 0.7V, the diode is on, the output will be clamped at 0.7 V. The difference voltage between the input and 0.7V will be "carried" by the series resistor, as there is now current flow in this case. Assuming the input is a sine wave with a magnitude of 1, the output waveform as a function of time is shown in Fig. 4(b). When the voltage exceeds 0.7 V, the output voltage is clipped off and remains at 0.7 V.

Exercise: Draw the transfer characteristics of the output vs. input voltage.

Fig. 4. 1st Clipper circuit using the simple piecewise 0.7 model. (a) The diode circuit representing a single limiter. (b) The plot of the input voltage and the resulting output voltage as a function of time.

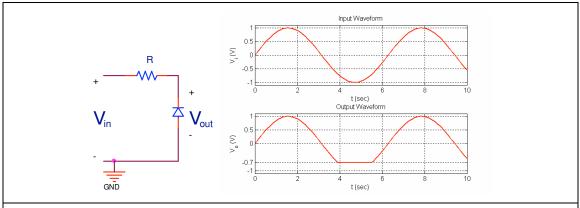

If the orientation of the diode is switched, as shown in Fig. 5(a), the same analysis follows. If the input voltage is greater than -0.7V, the diode is an open circuit, and the output voltage is equivalent to the input voltage. On the other hand, if the input is less than -0.7 V, the diode is on and is a short circuit, thus output voltage is limited to be -0.7 V. Fig. 5(b) shows the output voltage as a function of time when input is a sine wave with 1V magnitude. When the input voltage falls below -0.7 V, the output voltage is clipped off and remains at -0.7 V.

Fig. 5. Examination of behavior with diode orientation reversed, assuming the simple piecewise 0.7 model. (a) The diode circuit representing a single limiter. (b) The plot of the input voltage and the resulting output voltage as a function of time.

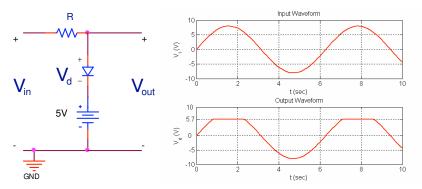

With the first canonical form, we have a limitation on the value the output becomes bounded, i.e., it is bounded by either 0.7 V or -0.7 V. We can change this value by adding a battery in series with the diode. We obtain our second canonical form by augmenting this battery, as in Fig. 6. The input needs to become (0.7 + battery voltage) Volts before the output voltage in the transfer characteristic flattens out. Furthermore, if the orientation of the battery is switched, the clipping will occur in the negative region.

Fig. 6. The 2<sup>nd</sup> canonical form for analyzing clipper circuit, assuming the simple piecewise 0.7 model. (a) The new circuit with battery added in series with the diode. (b) The plot of the input voltage and the resulting output voltage as a function of time.

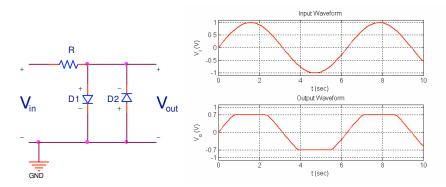

What we have examined is known formally as a single limiter, since the circuit will limit the output voltage on one side. By placing the two diodes with different orientation together in parallel, we obtain a circuit that bounds the output voltage on both sides. This double clipping action is more formally known as a double limiter. An example is shown in Fig. 7. The output voltage is both bounded below and above by 0.7 V and -0.7 V, respectively.

Fig. 7. A combination of two canonical forms in parallel, again assuming simple piecewise 0.7 model. (a) The double limiter circuit. (b) Plot of input voltage waveform and the resulting output voltage waveform.

Using the second canonical form, we can achieve a clipping at different voltages by placing different battery voltages. A classical example, used both in lecture and the textbook, is shown in Fig. 8. Knowing the canonical forms, we easily simplify the problem by examining each of the two parallel branches separately and superposing the two results.

Fig. 8. Clipper circuit diagram.

#### 2.5.2 Level Shift Circuit

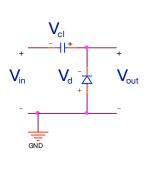

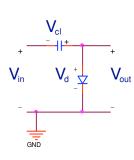

A level shift circuit is composed of a capacitor in series with a diode. Note the orientation of the diode in relation to the output voltage and also note the polarity of the capacitor, as shown in Fig. 9. The intuition behind a level shift circuit is gained by considering the two cases with the diode on and off separately. We will use the ideal diode model. When the diode is turned on, we have a short circuit; hence the output voltage is zero. At this stage, the capacitor will get charged to an equal and opposite value as the input voltage. On the other hand, when the diode is turned off, the output voltage is given by KVL,  $V_{out} = V_{cl} + V_{in}$ .

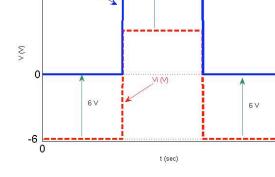

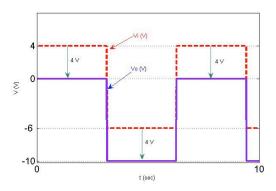

Let's look at an example now. Consider a square wave as an input passed into the level shift circuit shown in Fig.10, with the positive peak at 4 V and negative peak at -6 V. Initially, when the square wave takes a negative value, the diode becomes a short circuit; hence the output voltage becomes zero. At this stage, the capacitor will get charged to become the negative of the input voltage; KVL shows us that  $V_{in} = -V_{cl}$ . Thus  $V_{cl} = 6V$  here. When the input jumps to a positive value, the diode will be turned off, and  $V_{out} = V_{cl} + V_{in} = 4 + 6 = 10 \text{ V}$ . When the input returns to -6V again, the diode is again a short circuit and  $V_{out} = 0$ . But in this case, the capacitor is already fully charged to 6V, there will be no longer current flow. The resulting waveform is shown in Fig. 10.

6 V

Fig. 9. The prototypical level shift circuit. Note the orientation of the diode and capacitor in relation to the input voltage.

Fig. 10. The output voltage waveform,  $V_{\text{out}}$ , shown in solid lines, is obtained when the input voltage waveform,  $V_{\text{in}}$ , shown in dashed lines, is passed into the level shift circuit in Fig. 9. The resulting output waveform is shifted upward by 6 V.

If we switch the orientation of the diode (but still define all the polarities in the same way), the square wave will be shifted downward instead of being shifted upward. This new orientation is shown in Fig. 11. The polarity of the capacitor and output voltage remained the same. The only change is that the direction of the diode is reversed. The resulting waveform will then take the form as shown in Fig. 12.

Fig. 11. Reversing the orientation of the diode while keeping the polarity the same.

Fig 12. The output voltage waveform,  $V_{\text{out}}$ , shown in solid lines, is obtained when the input voltage waveform,  $V_{\text{in}}$ , shown in dashed lines, is passed into the level shift circuit in Fig. 10. The resulting output waveform is shifted downward by 4 V.

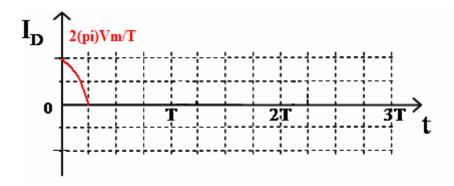

#### Exercise: Draw the diode current as a function of time.

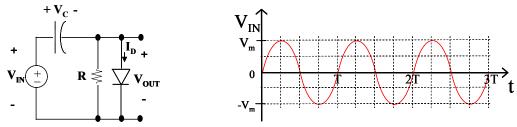

#### 2.5.3 Clamping Circuit (a.k.a. DC Restorer)

The level shift circuit shows that the square wave can be shifted upward and downward, depending on the orientation of the diode. In either case, the wave is bounded above or below by the threshold value of the diode. In other words, the peak or trough of the waveform is "clamped" at this particular threshold value of the diode. Because we assume the ideal diode model, the output waveform becomes bounded by 0 V. If we had assumed the simple piecewise 0.7 model, the output waveform would become bounded either below or above by 0.7 V. We can clamp the waveform by utilizing different diodes with different threshold value. However, we sometimes wish to clamp the waveform with a large range of possible voltage values. To accomplish this greater freedom, we add a battery in conjunction with the diode. Thus, it can be seen that clamping circuit is a more generalized class of a level shift circuit.

#### 2.5.4 Rectifier Circuit

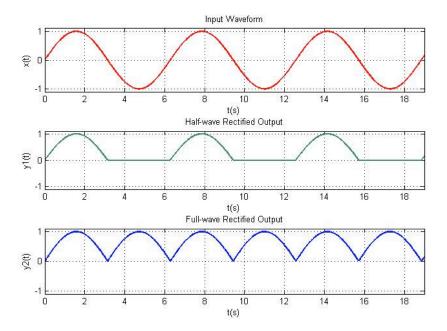

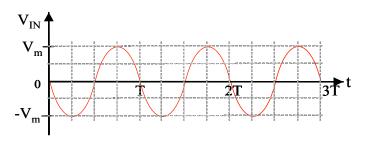

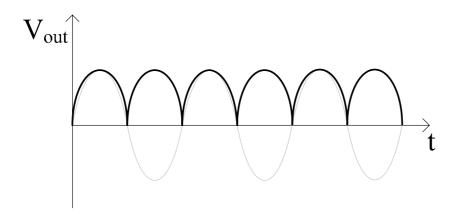

Rectifier circuits are divided into two classes - half-wave and full-wave rectifier. Consider a sinusoidal

input signal x(t) as given. Mathematically, a half-wave rectifier produces an output  $y_1(t) = \frac{|x(t)| + x(t)}{2}$ ,

while a full-wave rectifier produces an output  $y_2(t) = |x(t)|$ . These outputs,  $y_1(t)$  and  $y_2(t)$ , represent a half wave and a full-wave rectified output, respectively, assuming the ideal diode model. An example showing the input and output waveform for a half-wave and a full-wave circuit is shown in Fig. 13. If we were mathematicians, our discussion of rectifier circuits would terminate here; however, as an engineer, we want to know how to construct circuits to produce the output signals  $y_1(t)$  and  $y_2(t)$  given an input signal x(t).

Fig. 13 Half-wave rectified and full-wave rectified signals. The topmost signal is the input signal which is fed into a half-wave rectifier to produce the middle output signal, and fed into a full wave rectifier to produce the bottom signal.

### Half-Wave Rectifier

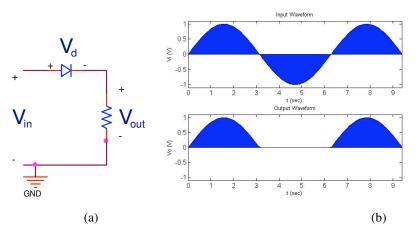

Fig. 14 shows the classical half-wave rectifier circuits. To analyze the output, we follow the input voltage and apply fundamental diode principles and KVL. When the input is positive, the diode behaves as a short circuit, thus the output voltage is given by  $V_{out} = V_{in} - V_d$  (KVL). Assuming an ideal diode model,  $V_{out} = V_{in}$ . Assuming a simple piecewise 0.7 model,  $V_{out} = V_{in} - 0.7$ . When the input is negative, the diode is reverse biased and behaves as an open circuit. Thus, the output voltage is zero since no current flows in the closed loop.

Fig. 14. (a) Half-wave rectifier circuit. (b) A sinusoidal input and the resulting output.

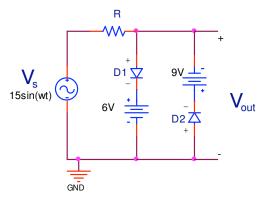

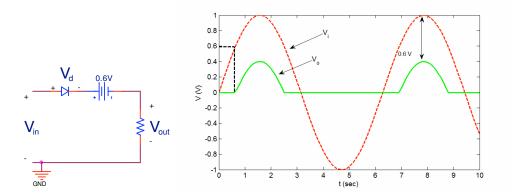

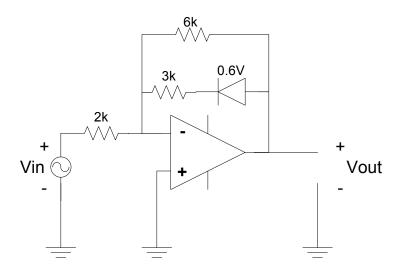

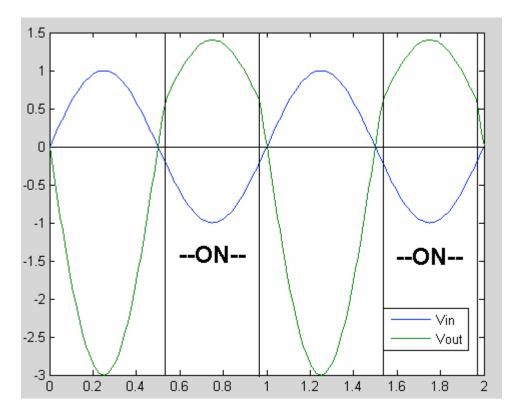

Now consider adding a 0.6 V battery to produce the circuit shown in Fig. 15. The ideal diode model is still assumed. The diode will be on only when the input is greater than the voltage across the battery, 0.6 V, since only then will the voltage across the diode be positive. ( $V_d = V_{in} - 0.6 \text{ V}$ ) The output voltage will be  $V_{in}$  - 0.6 (KVL). Whenever the input voltage falls below 0.6 V, the diode will be reverse biased. Thus, a zero current implies zero voltage.

Fig. 15. Adding a 0.6 V battery to the circuit produces the corresponding output signal, shown in green from the input signal, shown in red. Ideal diode model is assumed here.

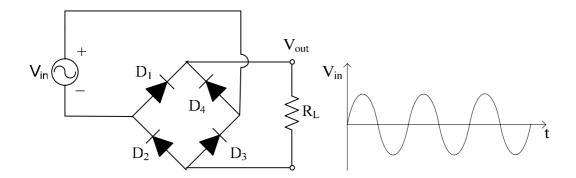

## Full-Wave Rectifier

A full-wave rectifier can be constructed in two ways:

- 1. Using two AC sources and two diodes

- 2. Using a diode bridge

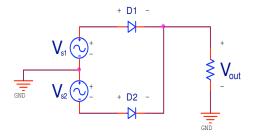

The first method composes of two sources which have  $\pi$  phase difference along with two diodes, as in Fig. 16. When  $V_{s1}$  is positive,  $V_{s2}$  is negative. Hence the top diode will be a short and the bottom diode will be an open. On the other hand, when  $V_{s1}$  is negative,  $V_{s2}$  is positive. Hence the bottom diode will be on and the top diode will be an open circuit. Therefore, we obtain the resulting waveform as shown in Fig. 13. In practice, a transformer can be used to provide the two out-of-phase voltage sources.

Fig. 16. A full-wave rectifier implemented using two AC sources and two diodes model. The two voltage sources are out of phase, as seen from the left plot.

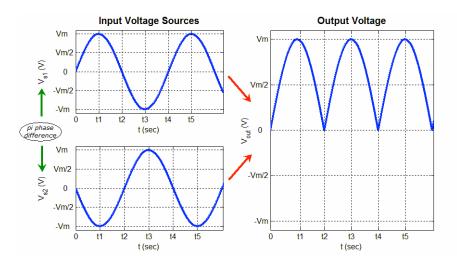

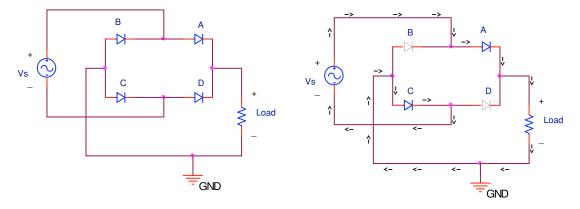

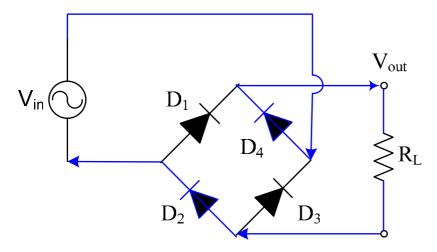

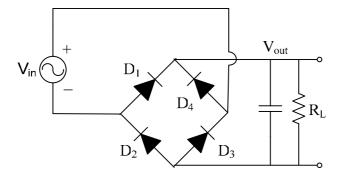

A second way to construct a full-wave rectifier is to use a diode bridge. This configuration is used because sometimes it may be impractical to obtain two voltage sources. Fig 17 shows a diode bridge. The four diodes are aligned such that diode A and C orient in the same direction and diode B and D orient in the same direction. The output is taken across the load resistor. The negative lead of the resistor is essentially the ground that connects to the junction between B and C.

In the positive portion of the cycle, both diode A and C will be on and both diode B and D will be under reversed bias. The current will flow through diode A, the load resistor, the ground, and return through diode C. The direction of the current is shown by arrows in Fig. 18. Diode B and D is shaded to indicate that they are both under reverse bias and off.

Fig. 17. A full-wave rectifier implemented using a diode bridge model.

Fig. 18. The input is in the positive cycle. The arrows show the path of the current. Diode B and D, shown in gray, are both under reverse bias and therefore off.

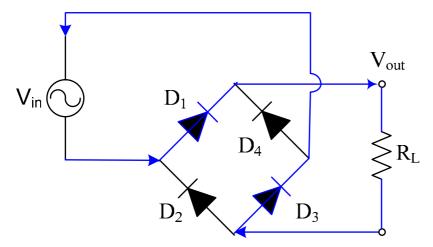

In the negative portion of the cycle, the opposite occurs. Diode B and D will be on and diode A and C will be under reverse bias. The current flows through diode D, the load resistor, and returns through diode B. This scenario is shown in Fig. 19. Again, the shading of diode A and C indicate their reverse bias condition, and the arrows show the path of the current.

Fig. 19. The input is in the positive cycle. The arrows show the path of the current. Diode A and C, shown in gray, are both under reverse bias and therefore off.

In either case, current will flow through the load resistor from the marked positive lead toward negative. Therefore, the voltage measured across the load will always be positive, so we obtain a full-wave rectified version of the original sinusoid.

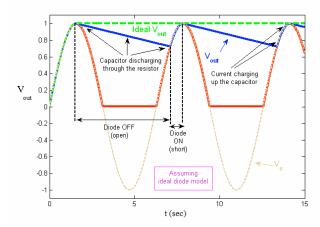

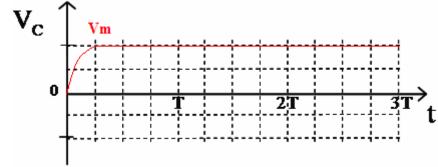

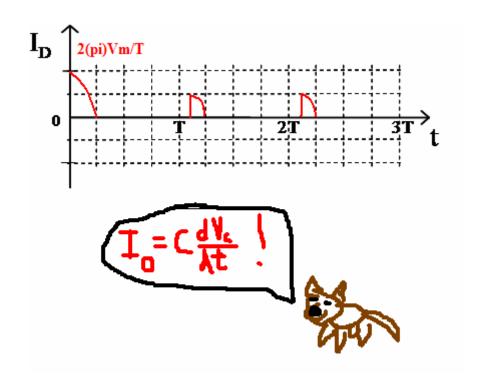

#### 2.5.5 Peak Detector

Peak detectors have useful applications in converting an AC signals into DC signals. They also have extremely important applications in envelope detection.

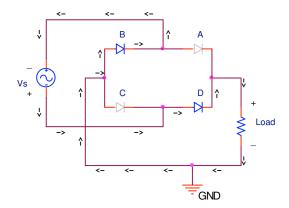

Fig. 20. Peak detection. (a) The top waveform is fed into a peak detector circuit to produce the bottom curve, assuming the capacitance is nearly infinite. (b) Peak detection circuit.

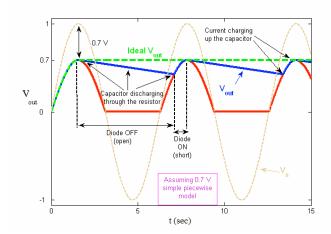

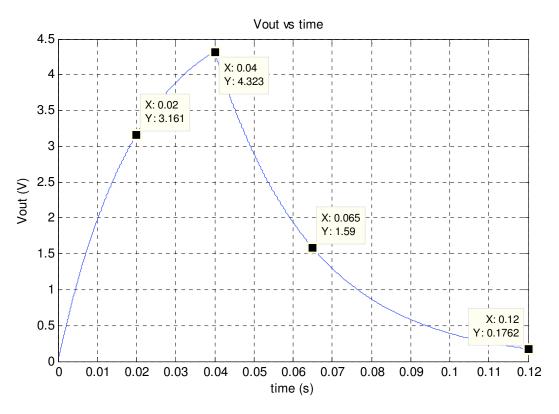

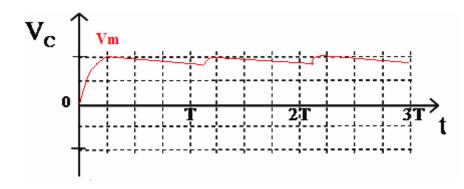

To construct a peak detector, we add a capacitor in parallel with the resistor in the existing configuration of a standard half wave rectifier. Assume the capacitor is initially uncharged.  $V_d = V_s - V_c$ . Initially, in the first quarter of a full period of a sine wave input, the diode will be a short circuit because the voltage across it will be positive, since  $V_s > V_c$ . The capacitor will get charged, thus the voltage across the capacitor will follow the input voltage.

When the input voltage reaches the peak of the sinusoidal curve, the input voltage will start to drop faster than the capacitor voltage, since we assume that the capacitor is fairly large (thus large time constant). When the input voltage drops faster than the capacitor voltage,  $V_s < V_c$ ,  $V_d < 0$ , and diode is turned off. The output voltage follows the capacitor discharge (as Vout = Vc). The shape of this curve will depend on how large the capacitance is. If the capacitance is assumed infinity, the curve will be a flat line. As the capacitor continues to discharge, there will be a point in which it intersects the input curve. After this intersection,  $V_s > V_c$ ,  $V_d > 0$ , diode will turn on again, and the capacitor follows the input curve as it gets charged up again.

Fig. 21. The plot of the output voltage  $V_{out}$  versus the input voltage  $V_s$ , given the peak detector circuit in Fig. 19 and assuming the ideal diode model. The ideal voltage output is shown in thick dashed lines, when the capacitor is assumed to be nearly infinite.

How does adding a battery in series with the diode affect the behavior of the output? We can gain an intuitive understanding of a peak detector by considering the circuit first without the capacitor. In another word, the capacitor is nonexistent, and it is simply a short where the capacitor should be. In this case, the output with a battery will be a half wave rectified shifted downward by the voltage across the battery. Adding the capacitor will add a curve connecting from the peaks to a point on the rising portion of the peak.

Fig. 22. The plot of the output voltage  $V_{out}$  versus the input voltage  $V_s$ , given the peak detector circuit in Fig. 19 and assuming the 0.7 simple piecewise model. The ideal voltage output is shown in thick dashed lines, when the capacitor is assumed to be nearly infinite.

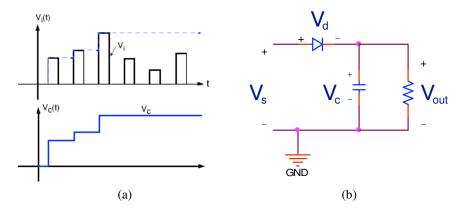

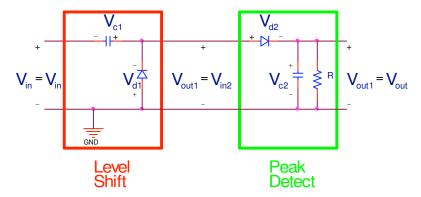

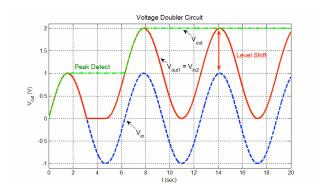

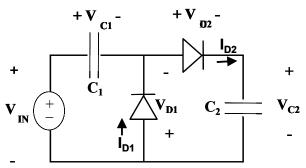

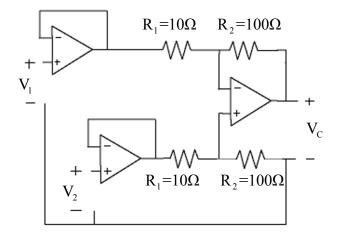

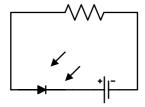

#### 2.5.6 Voltage Doubler Circuit

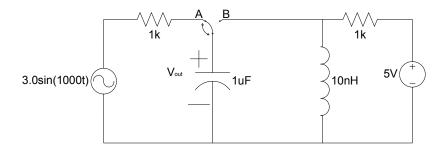

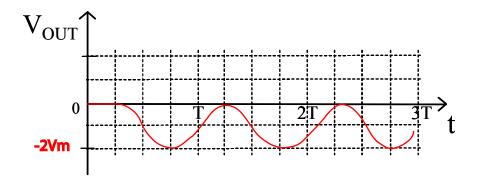

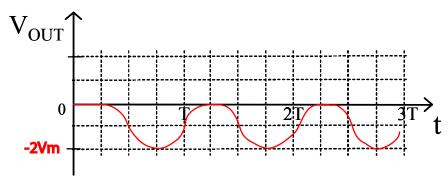

A voltage doubler is composed of a level shift circuit and a peak detector circuit in a cascade composition. In a sense, the level shift circuits will already double the input voltage. However, we use a peak detector to convert this AC signal into a DC signal. Fig. 23 shows such cascade composition. The output of the level shift circuit on the left is passed as an input to the peak detector circuit on the right.

Fig. 23. Voltage doubler circuit. A cascade composition of the level shift circuit with the peak detector. The output of the level shift circuit on the left is passed in as the input to the peak detector circuit on the right.

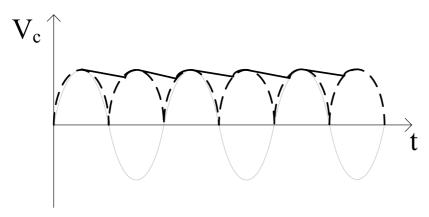

An example is shown below in Fig. 24. The input voltage waveform, indicated by dash lines, is passed into the circuit. After passing through the level shift circuit, a shifted version of the original waveform is formed. This new waveform is passed as an input to the peak detector circuit. The peak detector detects the peak of the new waveform, resulting in the final line indicated by 'peak detect.'

Fig. 24 A plot of the input voltage  $V_{in}$ , the intermediate voltage  $V_{outl}$  or  $V_{in2}$ , and the final voltage output  $V_{out}$ . After the initial waveform, indicated in dash, is shifted upward, the peak detector detects the peak to obtain the final output voltage.

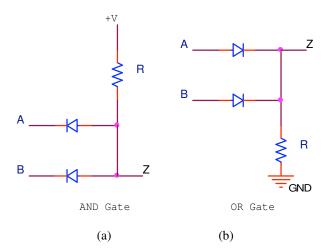

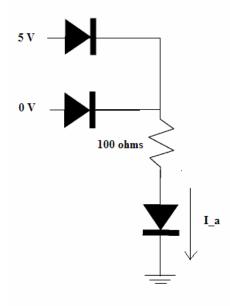

#### 2.5.7 Diode Logic Gates

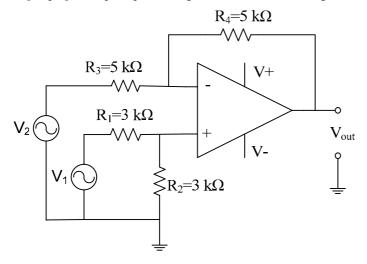

The two fundamental logic gates, AND and OR, can be implemented using diodes, as shown in Fig. 25. In an AND gate (Fig. 25(a)), the cathodes of the diodes are connected to a resistor that connects to a positive voltage source. The output is measured at point Z, the cathode of two diodes. In an OR gate (Fig. 25(b)), the anodes of the diodes are connected to a resistor that connects to ground, and the output is taken at point Z, the anode the two diodes.

Fig. 25. Diode logic gates. Z represents the output, given A and B as inputs. (a) AND gate. (b) OR gate.

#### AND Gate

AND gate is shown in Fig. 25(a). If either input A or B is low, the diode will conduct, resulting in a short circuit thus a low output Z. Only when both the inputs to A and B are high will neither of the diode conduct. The diode will behave as open circuits resulting in a high output Z. These conditions are shown in Table 1, which presents the truth table for the AND gate.

Table 1. The truth table for the AND gate shown in Fig. 24(a).

| A | В | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

#### OR Gate

OR gate is shown in Fig. 25(b). If both of the input to A and B is low, the diode will be off because the voltage across the diode is zero, hence no current flows. The output will therefore be pulled down to zero. If either of the input is high, the diode will conduct, as current flows from the higher potential to a lower potential. The output voltage at point Z will hence be a positive, high voltage, which is equal to the voltage across the resistor. Table 2 below presents the truth table for the OR gate. We can see from the table that the output is high when either one of the inputs A or B is high.

Table 2. The truth table for the OR gate shown in Fig. 24(b).

| A | В | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

# EE 40, University of California Berkeley

# Professor Chang-Hasnain

| 1 | 0 | 1 |

|---|---|---|

| 1 | 1 | 1 |

# **Chapter 3. Semiconductor Physics**

#### 3.1 Introduction to Silicon

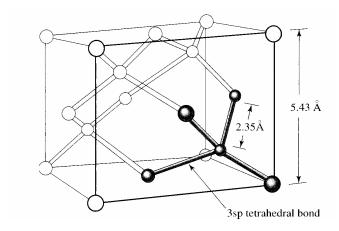

Almost all semiconductors used in integrated circuit (IC) technology are single crystalline Silicon (Si) material. Si is element 14, in Group IV, with an electronic configuration of  $1s^2 2s^2 2p^6 3s^2 3p^2$ . From this electronic configuration, we can see that Si has 4 valence electrons in the n=3 energy level. A silicon crystal is tetrahedrally arranged in a diamond cubic unit cell, in which the valence orbital are  $sp^3$  hybridized.

Fig. 1. Unit cell of crystalline silicon.

The atomic density of crystalline silicon can be calculated from its unit cell, shown in Fig. 1, by observing that there are 8 atoms in corners, each having 1/8 of the atom lie within the unit cell. There are 6 atoms on the faces of the cube, with 1/2 the atom inside the unit cell, and 4 more atoms completely inside the unit cell. Thus, the atomic density of silicon can be calculated, given the size of the unit cell, with length  $a_0$  on each side:

$$\frac{\#Atoms}{Volume} = \frac{8 \times \frac{1}{8} + 6 \times \frac{1}{2} + 4}{a_0^3} = \frac{8}{(5.43 \times 10^{-8} cm)^3} = 5.00 \times 10^{22} cm^{-3}$$

A common representation of the silicon crystal structure is given in Fig. 2. Each black line denotes a single bond, involving 2 electrons. Note that this does not represent a planar description of the crystalline structure of Si. Rather, this diagram demonstrates the bonding between each silicon atom and its 4 closest neighbors.

Fig. 2. Silicon bonding model.

#### 3.1.1 Bandgap Energy

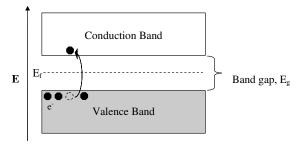

Conduction occurs in a substance through the flow of electrons (negative charge) and holes, or the lack of an electron (positive charge). The arrangement of atoms bonded together produces for its electrons many energy levels that are so close to each other that we may regard them as energy bands. Electrons are mobile in the high energy conduction band, while holes are mobile in the lower energy valence band. To form electron-hole pairs, electrons must have sufficient energy to overcome the bandgap energy, which is a region with no allowed energy levels. The excited electrons move from the valence band into the conduction band, leaving holes in the valence band. (See Fig. 3). Situations like this may occur when the crystal is illuminated with light or photons whose energy is larger than the bandgap energy, or when the crystal is sufficiently heated.

Fig. 3. Energy band diagram of semiconductors.

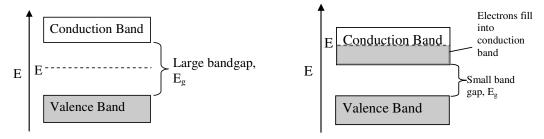

Insulators have a large band gap, usually 3.5 electron-volts (eV) or greater, preventing substantial amounts of charge carriers from flowing. Metals are good conductors, with electrons filling up into the conduction band. This means electrons are inherently mobile through a crystal, with thermal excitation producing even more electron-hole pairs. Semiconductors are in between, with band gaps ranging from 0.5 - 3.0 eV, allowing the easy excitation of electrons into the conduction band. However, it is the intermediate conductivity of semiconductors that is important for the electronics industry, along with their great flexibility in conductivity through doping.

Fig. 4(a). Band diagram of an insulator.

Fig. 4(b). Band diagram of a metal.

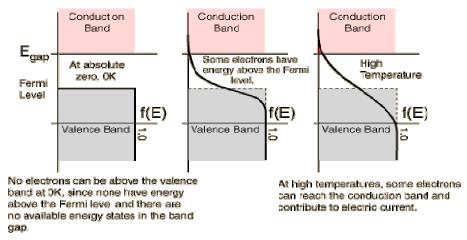

#### 3.1.2 Fermi Energy

The Fermi-Dirac function provides the probability that an energy level is occupied by a fermion which is under thermal equilibrium. Electrons as well as holes are Fermions and hence obey Fermi-Dirac statistics. (A hole is simply "the lack" of an electron.) As electrons are added to an energy band, they will fill the available states in an energy band just like water fills a bucket. The states with the lowest energy are filled first, followed by the next higher ones. At the Fermi level, the probability of filling the state is exact 50%. The transition between completely filled states and completely empty states is gradual rather than abrupt, and the transition depends on temperature. The Fermi function which describes this behavior, which is given by:

$$f(E,T) = \frac{1}{1 + e^{(E - E_f)/kT}}$$

(1)

where k is the Boltzmann constant,  $E_f$  is the Fermi energy, E is the energy of concern and T is the temperature at which the material is kept.

Figs. 4(a) and (b) show the position of the Fermi level in an insulator and a metal, respectively. Fig. 5 shows the Fermi function plotted with the energy bands at different temperatures. The x-axis, f(E), is the probability that an energy level is occupied. The lowest energy levels are almost always occupied, with a probability of 1, and the highest levels have a probability of nearly 0, but this probability increases with higher temperature. To be more precise, the sharp edge of Fermi function is smeared out due to the increase in temperature.

Fig. 5. Fermi function plots at absolute zero, mid-range, and high temperature.

For a given piece of semiconductor at a particular location (space coordinate) under thermal equilibrium, there is *only one Fermi level* for both the conduction and valence band, as it describes one equilibrium system.

For a semiconductor where  $E_v < E_f < E_c$ , we can derive the electron density, n and hole density, p, which are the density of states multiplied with Fermi probability function.

$$n = N_c \frac{1}{1 + e^{(E_c - E_f)/kT}} \sim N_c e^{(E_f - E_c)/kT}$$

$$p = N_v \left[ 1 - \frac{1}{1 + e^{(E_v - E_f)/kT}} \right] \sim N_v e^{(E_v - E_f)/kT}$$

$$np = N_c e^{(E_{f,i} - E_c)/kT} N_v e^{(E_v - E_{f,i})/kT} = N_c N_v e^{(E_v - E_c)/kT} = N_c N_v e^{-E_g/kT}$$

Here,  $N_c$  and  $N_v$  are the effective density of states in the *conduction* and valence band, respectively, and  $E_g$  is the bandgap energy. All three are constants for Si at a given temperature. This property is referred to as the *mass action law*

For an intrinsic (undoped) Si, the electron density  $n_i$  equals to the hole density, p, which is thus:

$$\begin{aligned} n_i &= p_i \\ n_i p_i &= n_i^2 \\ n_i &= \sqrt{N_c N_v e^{-E_g/kT}} \end{aligned}$$

#### **3.1.3 Doping**

Doping a semiconductor refers to the careful addition of impurity atoms into the semiconductor. A doped semiconductor is considered extrinsic, and has enhanced conductivity due to additional charge carriers from the dopant atoms. The two categories of dopants are n-type, with excess electrons producing donor energy levels near the conduction band, and p-type, with holes (lack of electrons) producing acceptor energy levels just above the valence band. The two types of doped semiconductors are named for their majority charge carriers (the leading contributors to conduction in a material): n-type's majority charge carrier is electron (negative charge), while p-type's is hole (positive charge).

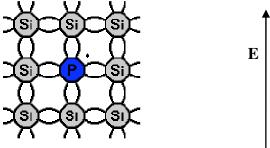

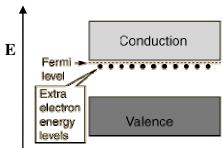

N-type dopants are typically group V elements, such as Phosphorus (P) and Arsenic (As), with five valence electrons. When a group V element is incorporated into Si and, in fact, replaces a Si atom in a lattice, it provides four of its outermost electrons to form covalent bonds with the surrounding Si atoms. However, there is an extra electron remaining, loosely orbiting the dopant atom, at a large radius, or high energy, as shown in Fig. 6(a). Thus, the extra electron form the donor electron that are close and easily excitable to the conduction band.

Typically, we may consider the electron density  $n = N_d$ , where  $N_d$  is the n-doping density, which can be seen as an increased Fermi energy level, shifting it closer to the conduction band compared to an undoped semiconductor at the same temperature. (See Fig. 6(b).) We can calculate the Fermi level relative to the conduction band edge and the hole density using the following equations.

$$n = N_d = N_c e^{(E_f - E_c)/kT}$$

$$p = n_i^2 / N_d$$

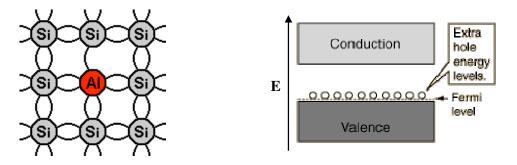

P-type dopants are typically Group III elements, such as Boron (B) and Gallium (Ga), with three valence electrons. Of the four covalent bonds with surrounding Si atoms in the crystal lattice, only three are filled with an electron from the dopant atom. This vacancy creates an acceptor energy level just above the top of the valence band, for surrounding electrons to fill with ease. An electron that fills this hole propagates the vacancy to a Si atom, which is now missing an electron and positively charged. In this manner, the hole represents a region of positive charge, and is mobile just as an electron is, as shown in Fig. 7(a).

Fig. 6(a). Bonding model of n-type dopant (donor). Fig. 6(b). Band diagram of n-doped semiconductor.

The presence of holes shifts the effective Fermi level downwards. This means less electrons will be found in the conduction band (while more holes can be found in the valence band) than in an intrinsic semiconductor, and the positively charged holes serve as the majority charge carrier. Fig. 7(b) shows the energy band diagram, where electrons can easily occupy the low energy acceptor levels provided by the p-dopants. In this case, we will have:

$$p = N_A = N_v e^{(E_v - E_f)/kT}$$

$$n = n_i^2 / N_A$$

It is amazing to see that a tiny amount of dopant is enough to achieve a great effect. For instance, typical doping concentrations are  $10^{16} - 10^{19}$  cm<sup>-3</sup>, but compared to the  $5.0 \times 10^{22}$  cm<sup>-3</sup> density of Si atoms, a  $10^{18}$  doping concentration means a 1:50,000 ratio of dopant atoms to Si atoms.

Figure 7(a). Bonding model of p-type dopant (acceptor). Figure 7

Figure 7(b). Band diagram of p-doped semiconductor.

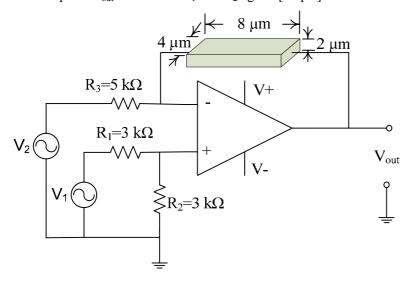

#### 3.1.4 Doping Methods

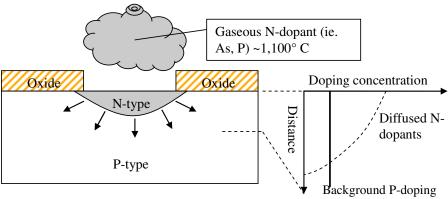

A common method of doping is diffusion. When a silicon crystal is exposed to high temperature dopants (gas phase), dopant atoms will diffuse against a concentration gradient into the silicon, where its concentration is much lower. Fig. 8(a) illustrates the process, where an oxide (SiO<sub>2</sub>) shields the silicon from the dopant. Fig. 8(b) plots the doping concentrations along the material, as a cutout from Fig. 8(a).

Fig. 8(a). Doping through diffusion of n-dopants into p-type silicon.

Fig. 8(b). Doping profile of the upper region of silicon in Fig. 8(a).

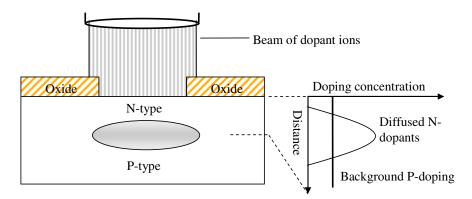

An alternative method to the high-temperature diffusion is ion implantation. Dopant ions are accelerated to high speed, and directed in a beam towards the silicon. This process allows more control of doping distribution than diffusion, because the penetration depth of the ions is directly correlated to their kinetic energy. Fig. 9(a) illustrates ion implantation, again in which an oxide shields areas to remain undoped. Fig. 9(b) shows the doping profile of the sample in Fig. 9 (a) after ion implantation.

Ion implantation allows silicon to be doped at lower temperatures than diffusion. However, the silicon crystal is damaged by the penetrating dopant atoms. Fortunately, a thermal treatment, annealing, of the silicon can remove most of the damage.

Fig. 9(a). Doping through ion implantation of N-dopants into P-type silicon.

Fig. 9(b). Doping profile of the upper region of silicon in Fig. 9(a).

#### 3.2 Quantitative Analysis

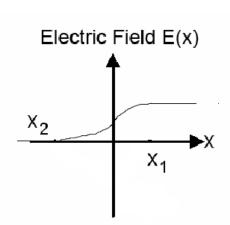

#### 3.2.1 Electric Fields

Gauss's law relates the electric field,  $\vec{E}$  , and charge. In differential form, Gauss's law is:

$$\nabla \cdot \vec{E} = \frac{\rho}{\varepsilon} \tag{1}$$

The divergence of the electric field from a point is equal to the volume charge density,  $\rho$  (units of Coulombs / cm³), divided by the electric permittivity,  $\mathcal{E}$  (units of Farads / cm). Thus, the units of electric field,  $\vec{E}$ , are Volts / cm. The permittivity measures a material's ability to polarize in response to an electric field, and consequently cancel out the field. The permittivity of free space,  $\mathcal{E}_0$ , is about  $8.85 \times 10^{-14}$  F/cm, while the permittivity of silicon is around  $11.7 \mathcal{E}_0$ .

In integral form, Gauss's law is:

$$\oint_{S} \vec{E} \cdot d\vec{A} = \frac{1}{\varepsilon} \oint_{V} \rho \cdot dV = \frac{Q_{encl}}{\varepsilon}$$

The surface integral of electric flux is equal to the charge, Q (Coulombs), enclosed by the surface, divided by the electric permittivity.

In our study of semiconductors, we usually need only the 1-dimensional version of Gauss's law:

Differential form:

$$\frac{dE}{dx} = \frac{\rho}{\mathcal{E}}$$

(2)

Integral form:

$$\int_{x_a}^{x_b} d[\mathcal{E}E(x)] = \mathcal{E}_b E(x_b) - \mathcal{E}_a E(x_a)$$

$$= \int_{x_a}^{x_b} \rho(x) dx = Q_{encl} \Big|_{x_a}^{x_b}$$

(3)

where  $Q_{\text{encl}}$  is the charge enclosed between  $x_a$  and  $x_b$ . The permittivity,  $\varepsilon$ , may differ throughout a material, so it is included inside the differential, along with the electric field, E(x).  $\varepsilon_a$  is the permittivity at  $x_a$ , and likewise for  $\varepsilon_b$ . We can find the electric field at a point b, by selecting a boundary point a that contains zero charge density. The electric field at the boundary location,  $E(x_a)$  would then be 0.

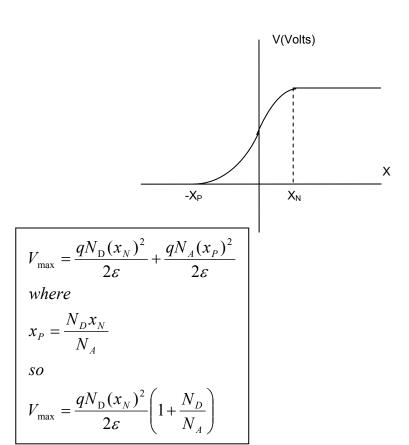

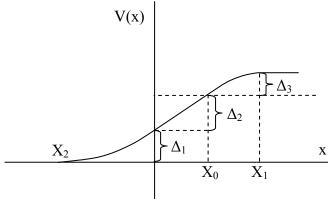

#### 3.2.2 Electrostatic Potential

Poisson's Equation relates electrostatic potential,  $\phi$ , to the electric field,  $\vec{E}$ , and to charge density,  $\rho$ . The units of potential are Joules / Coulomb, or Volts.

In differential form, it is:

$$\nabla^2 \phi = -\nabla \cdot \vec{E} = -\frac{\rho}{\varepsilon}$$

As before, we only need the one dimensional version in our analysis of semiconductors:

$$\left| \frac{d^2 \phi(x)}{dx^2} = -\frac{dE(x)}{dx} = -\frac{\rho(x)}{\varepsilon} \right| \tag{4}$$

By definition, the electrostatic potential  $\phi(x)$  is found with respect to an arbitrary value at a reference point  $x_0$  as the integral of the negative of the electric field E from  $x_0$  to x:

$$\phi(x) - \phi(x_0) = \int_{x_0}^{x} -E(x)dx$$

(5)

Like any potential function, only the potential difference (voltage) between two points is physically meaningful, since any constant can be added to  $\phi$  without affecting  $\vec{E}$ . Thus, the usual value chosen for the potential at the reference point,  $x_0$ , is  $\phi(x_0) = 0$ .

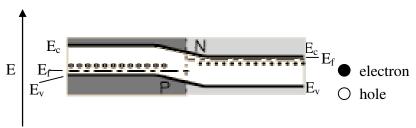

#### 3.3 PN Junction

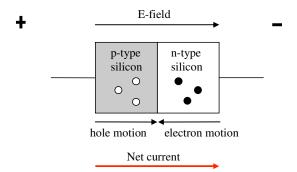

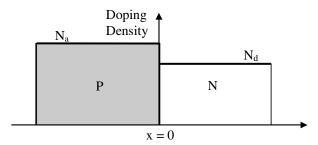

A PN junction is formed when p-type material is in contact with an n-type material. This device allows considerable current to flow in only one direction (forward bias), while basically preventing current from flowing in the opposite direction (reverse bias) as shown in Fig. 14. Note that this semiconductor is a single crystal, in which one region is doped with acceptor impurity atoms (P-region), and the adjacent region is doped with donor atoms (N-region). For simplicity, we will consider a step junction where the doping concentration is uniform in each region, and there is an abrupt change in doping at the junction (see Fig. 15). Doping concentrations  $N_a$  in the P-region and  $N_d$  in the N-region are in units of cm<sup>-3</sup>, denoting 1 impurity atom / cm<sup>3</sup>.

Fig. 14. PN junction with applied electric potential (forward bias).

Fig. 15. Doping profile of a PN junction.

#### 3.3.1 Depletion Approximation

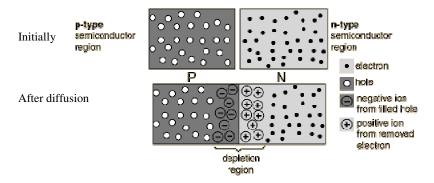

The behavior of the PN junction can be understood by analyzing the physics of the diode as modeled in Fig. 16. Initially at the junction, there is a very large concentration gradient in the electron and hole concentrations. Majority carrier electrons in the N-region will begin diffusing into the p-region and majority carrier holes in the P-region will begin diffusing into the N-region. **Even though a doped semiconductor has excess electrons and holes, it is electrically neutral.** However, as electrons diffuse from the N-region, positively charged donor atoms are left behind (see Fig. 16). Likewise, holes diffusing from the P-region will leave negatively charged acceptor atoms.

Fig. 16. Formation of the depletion region due to mobile charge carrier diffusion in a PN junction.

The dopant atoms, now ionized, are immobile because they are fixed in the crystal by their covalent bonds with surrounding silicon atoms. The regions on both sides of the junction are now depleted of mobile charge carriers, because the mobile carriers (electrons and holes) have diffused to the other side. The N-side is now positively charged with ionized donors near the junction, and the P-side is negatively charged with ionized acceptors, due to the ionized dopants. We call this the depletion region, which on either side, is depleted of mobile charge carriers and has a constant charge density due to the constant doping

concentration. The presence of immobile ions, as illustrated in Fig. 16, generates a built-in electric field pointing from N-side to the P-side within the depletion region. This built-in field will prevent mobile charge diffusion across the junction and balance the carrier motion in a PN junction under thermal equilibrium.

The portions of the semiconductor outside the depletion region are electrically neutral, due to the balance of charge carriers and dopant atoms. Reference 1 present a good quantitative treatment of the depletion approximation, in which we assume:

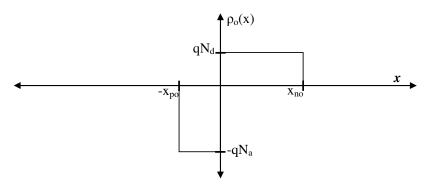

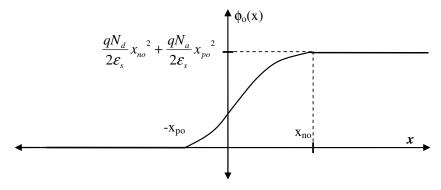

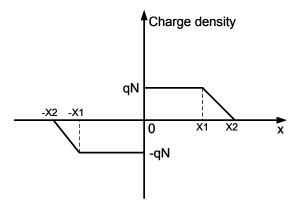

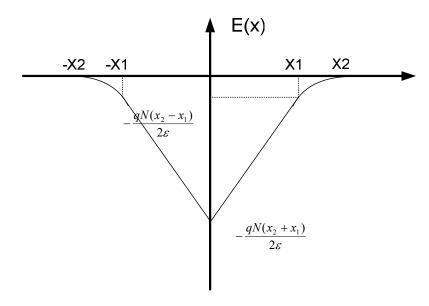

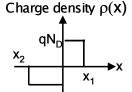

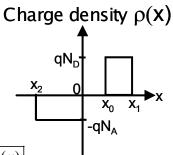

$$\rho_0(x) \approx \begin{cases} -qN_a & (-x_{p0} \le x \le 0) \\ qN_d & (0 \le x \le x_{n0}) \end{cases} \text{ and } \rho_0(x) = 0 \quad (x < -x_{p0}, \ x > x_{n0}) \quad (10)$$

The charge distribution above in equation (10) describes the depletion region of a PN junction with the P-side between  $x = -x_{po}$  and x = 0, while the N-side is between x = 0 and  $x = x_{no}$ . The P-side has a doping concentration of  $N_a$ , and its acceptor dopants ionize to negatively charged atoms, so the charge density,  $\rho_o$ , of this side is  $-qN_a$ . Likewise, the N-side has a doping concentration of  $N_d$ , with positively charged donor ions, giving a charge density,  $\rho_o$ , of  $qN_d$ . Keep in mind that the PN junction actually extends past  $-x_{po}$  and  $x_{no}$ , but this bulk silicon outside the depletion region is neutrally charged, so  $\rho_o = 0$  in the regions where  $x < x_{po}$  and  $x > x_{no}$ .

Fig. 17. Charge distribution,  $\rho_0(x)$ , of the PN junction, with depletion region as approximated in Equation (10).

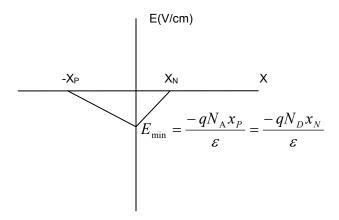

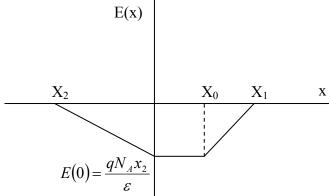

#### 3.3.1.1 Finding the electric field

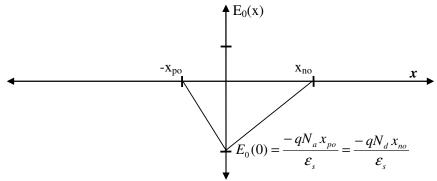

The subscript 0 for the charge density  $\rho_o(x)$  indicates that our PN junction is in thermal equilibrium. We now integrate the charge density to find the electric field  $E_o(x)$  and then integrate again to find the electrostatic potential  $\phi_o(x)$ . Gauss's Law relates the charge density to the derivative of the electric field:

$$\frac{dE_0}{dx} = \frac{\rho_0(x)}{\varepsilon_s} \tag{11}$$

where  $\mathcal{E}_s = 11.7 \,\mathcal{E}_0$  is the electric permittivity of silicon.

The PN junction in thermal equilibrium has no net current flow. In the formation of the depletion region, the total negative charge on the P-side is equal and opposite to the positive charge on the N-side, because an equal number of holes from the p-side and electrons from the n-side diffused and recombined at the interface. Thus, differing doping concentrations  $N_a$  and  $N_d$  will result in regions of different width, but the net charge on either side is the same:

$$qN_a x_{po} = qN_d x_{po} (12)$$

This fact means that the electric field at the boundaries  $-x_{-po}$  and  $x_{no}$  is 0, because the net enclosed charge in the depletion region is 0 (Gauss's Law states that if a surface encloses no net charge, there is no electric

flux through the surface). Also important, the adjacent bulk silicon outside the depletion region is neutrally charged.

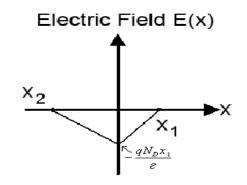

On the P-side of the depletion region  $-x_{po} < x < 0$ , we integrate the charge distribution of equation (10) to obtain the electric field:

$$E_0(x) = \int_{-x_{po}}^{x} \frac{\rho_0(x)}{\mathcal{E}_s} dx + E_0(-x_{po}) = \frac{-qN_a}{\mathcal{E}_s} (x - (-x_{po})) + 0$$

where our constant of integration,  $E_o(-x_{po})$ , is 0, because at the edge of the depletion region, the electric field is 0. This is because there is no charge density on the left side (bulk p-silicon). Therefore,

$$E_0(x) = \frac{-qN_a}{\varepsilon_s}(x + x_{po}) \qquad (-x_{po} < x < 0)$$

(13)

In the N-region, the electric field can be found by noting that at the boundary of the depletion region with the bulk n-silicon,  $x_{no}$ , the electric field,  $E_o(x_{no})$ , is the sum of the electric field,  $E_o(x)$ , at the point x, and the contribution due to the charge between x and  $x_{no}$ , found by Gauss's law:

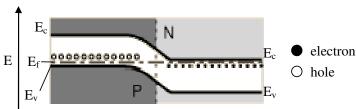

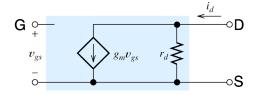

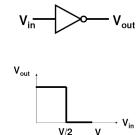

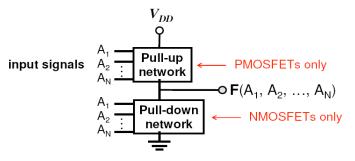

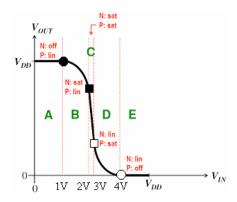

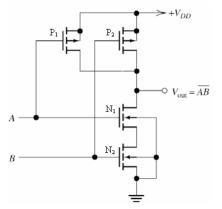

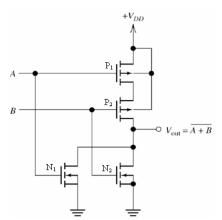

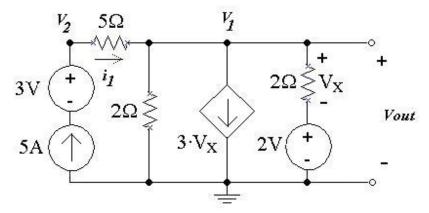

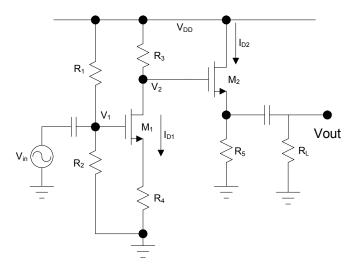

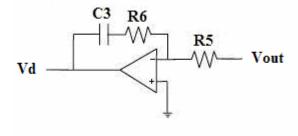

$$E_0(x_{no}) = E_0(x) + \int_x^{x_{no}} \frac{\rho_0(x)}{\mathcal{E}_s} dx = 0$$