Lecture 11: October 8, 2001

# **Physical Limitations of Logic Circuits A)**Synthesis Recap **B)** General Limitations for Digital **C)**Gate Delay Causes and Model **D)**Timing Example: XOR for EE 43 **E)** Timing Example: Logic Function The following slides were derived from those prepared by Professor **Reading: Oldham For EE 40 in Fall 01** Schwarz and Oldham 11.3-11.4 pp. 403-422

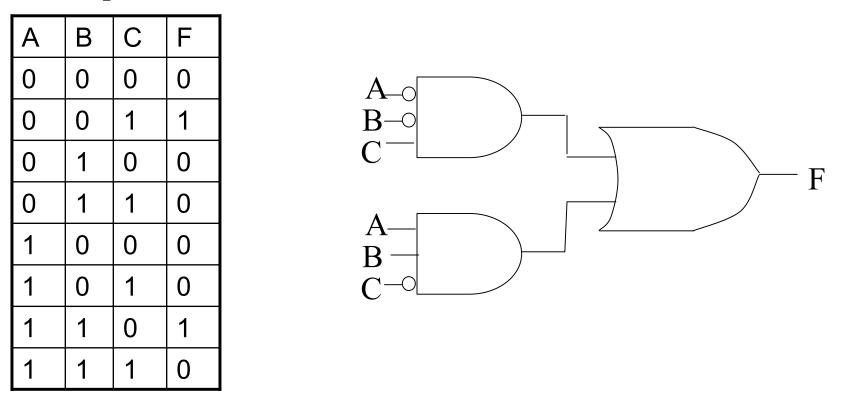

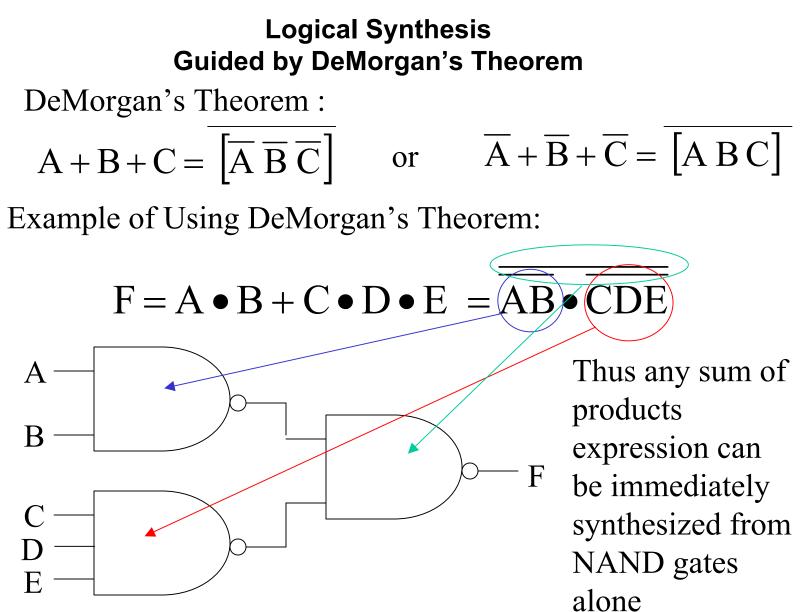

## How to Combine Gate to Produce a Desired Logic Function? (More basic Logical Synthesis)

Example:

$F = \overline{A} \overline{B}C + AB\overline{C}$

#### What Are Some Limitations of Digital?

It takes a lot of bits to represent even simple audio signals and if we convert a real-time audio signal to digital, we need to transmit a lot of bits every second.

**Example:** An ordinary audio signal is sampled every 50µs (to achieve 10KHz frequency performance) and evaluated (converted to digital form) to an accuracy of 1 part in 10,000. Every sample requires how many bits?

$2^{13}$  = 8,192 and  $2^{14}$  = 16,384 so we need 14 bits for each sample. Now we need to transmit these bits 20,000 times per second. The bit rate is 280,000 baud!

The transmission of digital signals as pulses through circuits and over transmission media leads to pulse degradation, just as analog signals are degraded. As a consequence, we must (a) detect and regenerate the signal before it gets "buried in the noise," and (b) accept that propagation delays are intrinsic to signal flow, and take these delays into account in our design (e.g., to avoid making a control decision based on a piece of information that has not yet arrived!). The RC transient lectures treated pulse degradation in real circuits quantitatively.

## Version Date 10/08/01 PHYSICAL LIMITATIONS OF LOGIC GATES

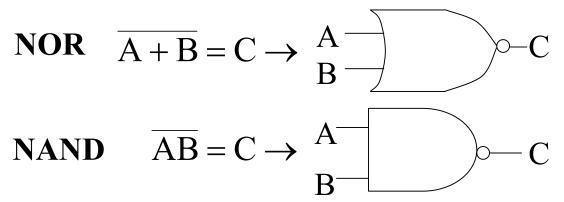

- Computer Datapath: Boolean algebraic functions using binary variables

- Symbolic representation of functions using logic gates

## However:

• Every node has capacitance and interconnects have resistance. It takes time to charge these capacitances.

Thus, output of all circuits, including logic gates is **delayed** from input.

## Version Date 10/08/01 PHYSICAL LIMITATIONS OF LOGIC GATES

Computer Datapath: Connected logic gates

Every node in any circuit (such as the internal circuit of a NAND gate) has capacitance and all interconnects have resistance. Thus it takes time to charge these capacitances.

Thus, output of all circuits, including logic gates is **delayed** from input.

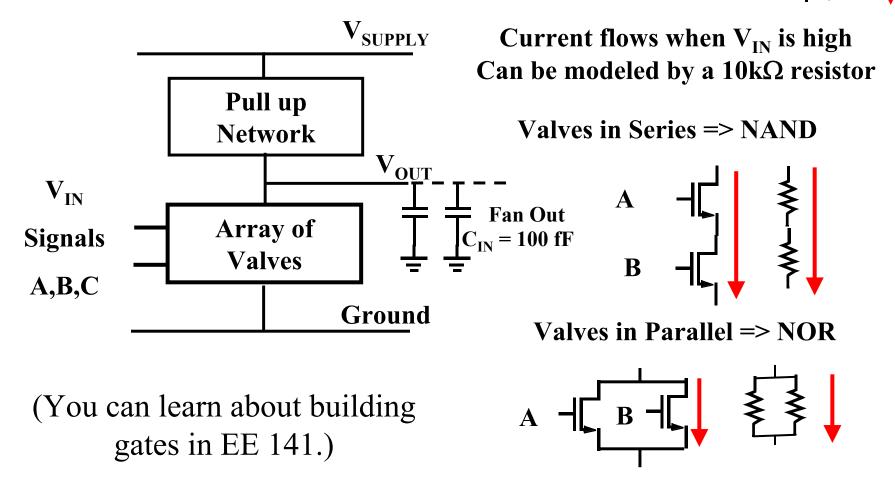

## Logic Gates – How are they built in practice?

A Valve is a Transistor

$$V_{IN} - \begin{bmatrix} 1 \\ 1 \end{bmatrix}$$

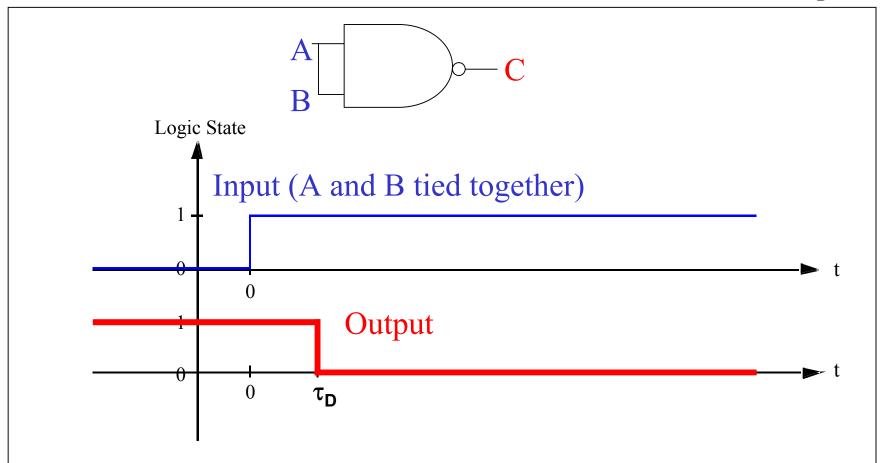

## UNIT GATE DELAY $\tau_{\text{D}}$

Time delay  $\tau_{\rm D}$  occurs between input and output: "computation" is not instantaneous

Value of input at t = 0<sup>+</sup> determines value of output at later time t =  $\tau_{D}$

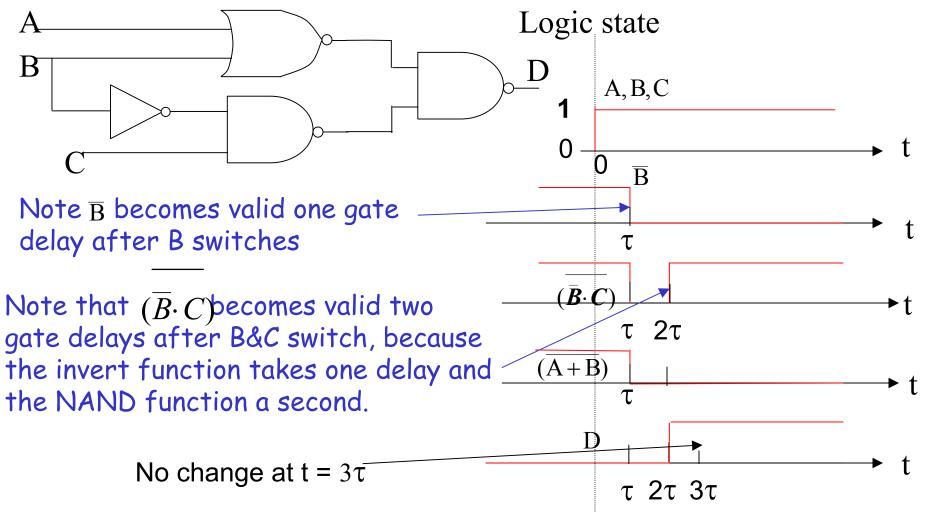

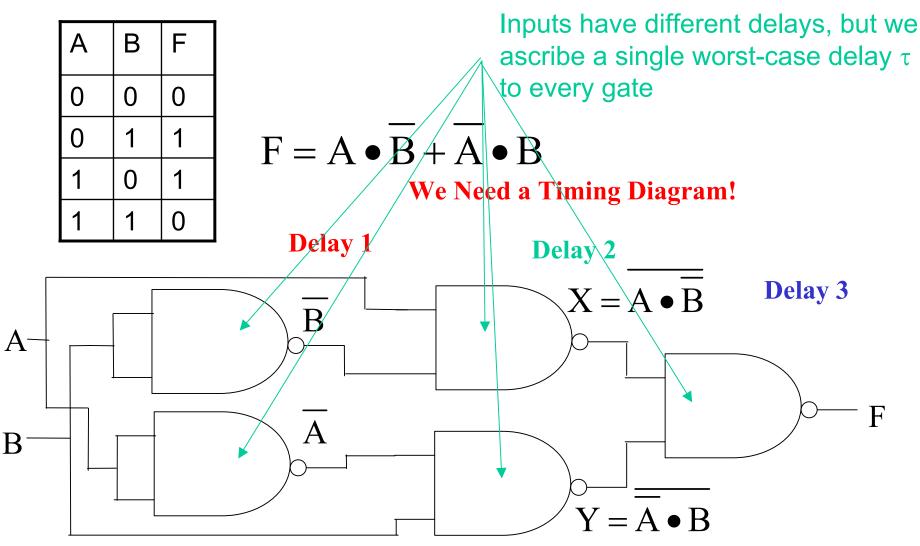

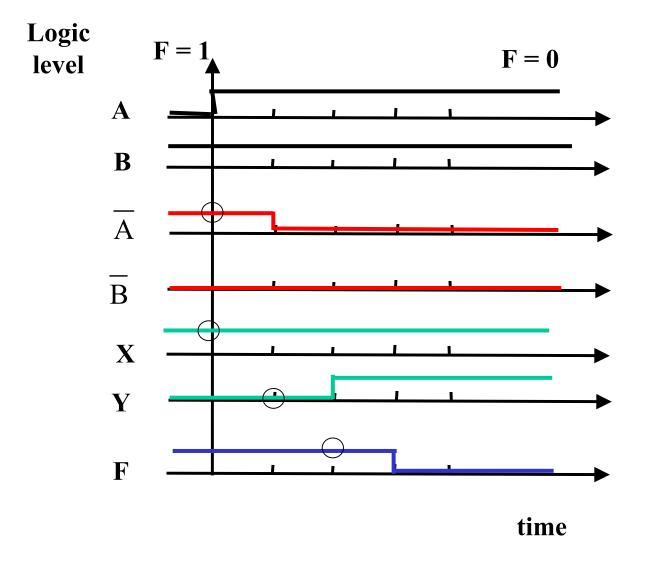

### **Timing Diagram for Delays in Logic**

## **EFFECT OF GATE DELAY**

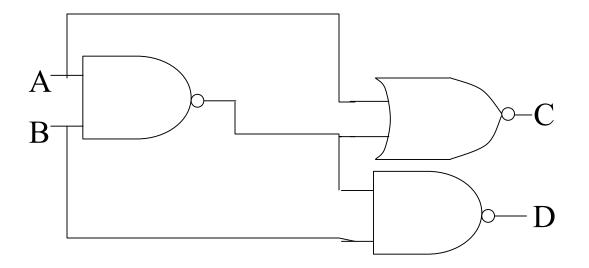

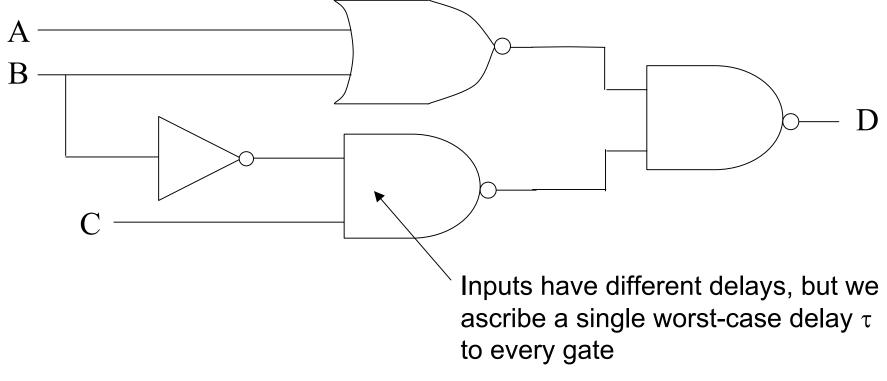

Cascade of Logic Gates

How many "gate delays for shortest path? ANSWER : 2

How many gate delays for longest path? ANSWER : 3 Copyright 2001, Regents of University of California

## TIMING DIAGRAMS

Version Date 10/08/01

Show transitions of variables vs time