Lecture 25: 12/3/01 A.R. Neureuther

Version Date 12/01/01

# Lecture 25

# **Integrated Circuit Layout and Fabrication**

- A) Assistance on HW #13

- **B)** CMOS Layout

- **C)** Process Flow

- **D)** Device Structure Evolution in Process Flow

### **Reading: Schwarz and Oldham, pp. 527-532**

# CMOS Device Parameters at 0.25µm

Lecture 23

Gate length is  $0.25 \,\mu m = 250 \,nm$

$$V_{\rm DD} = 2.5 V$$

|      | V <sub>T</sub> (V) | $V_{OUT-SAT}(V)$ | k' ( $\mu$ A/V <sup>2</sup> ) |

|------|--------------------|------------------|-------------------------------|

| NMOS | 0.43               | 0.63             | 100                           |

| PMOS | 0.4                | 1                | 25                            |

These parameters are from re-fitting I vs. V data in Chapter 3 of the EECS 141 Text Book by Rabaey with saturation current model we are using in EE42. Here  $V_{IN} = V_{DD}$   $I_{OUT-SAT-D} = k_D (V_{IN} - V_{TD}) V_{OUT-SAT-D}$  estimate the maximum  $I_{DS}$  $I_{OUT-SAT-D} = (100 \mu A / V^2) (\frac{0.375}{0.25})(2.5V - 0.43V)(0.63V) = 196 \mu A$

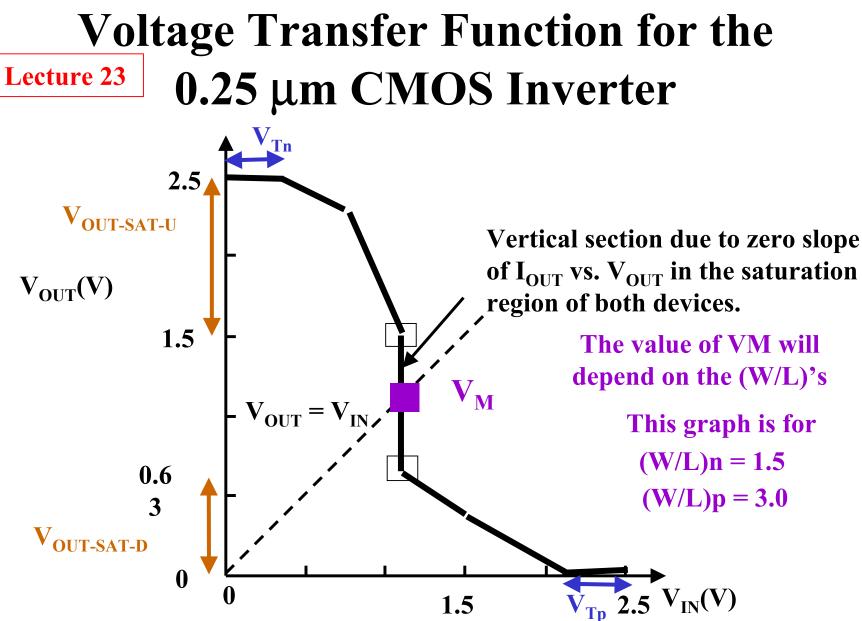

Copyright 2001, Regents of University of California

# **Version Date 12/01/01** Lecture 23 Finding $V_M$ for 0.25 $\mu$ m Inverter At V<sub>M</sub>, 1) $V_{OUT} = V_{IN} = V_M$ 2) Both devices are in saturation **Result will depend on** 3) $I_{OUT-SAT-n} = I_{OUT-SAT-p}$ (W/L) ratios. $I_{OUT-SAT-n} = k'_n \left(\frac{W}{L}\right)_n \left(V_{IN} - V_{Tn}\right) V_{OUT-SAT-n} =$ $I_{OUT-SAT-p} = k'_p \left(\frac{W}{L}\right)_p \left(V_{DD} - V_{Tp}\right) V_{OUT-SAT-p}$ Substitute<sup>V</sup><sub>M</sub> Solve for V<sub>M</sub> For $(W/L)_n = 1.5$ and $(W/L)_p = 3.0 V_M$ is 1.17V

#### Lecture 23

Version Date 12/01/01

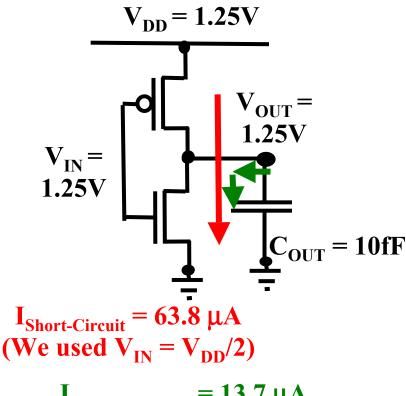

# **CMOS Inverter in Short-Circuit Condition**

Assume the CMOS inverter from above with  $V_{IN} = 1.25V$  and  $V_{OUT} = 1.25V$  driving a 10 fF capacitor

What happens to the output signal?

The capacitor slowly discharges to try to find an output voltage that balances the NMOS and PMOS currents for the given value of  $V_{IN}$ .

$$\frac{\partial V}{\partial t} = \frac{I}{C} = \frac{13.7\,\mu A}{10\,fF} = 1.37 \left( V \,/\, ns \right)$$

$$\begin{split} I_{Discharge\_Load} &= 13.7 \ \mu A \\ (We \ Used \ V_{IN} = V_{DD}/2) \\ & Copyright \ 2001, \ Regents \ of \ University \ of \ California \end{split}$$

Copyright 2001, Regents of University of California

Vorsian Data 17/01/01

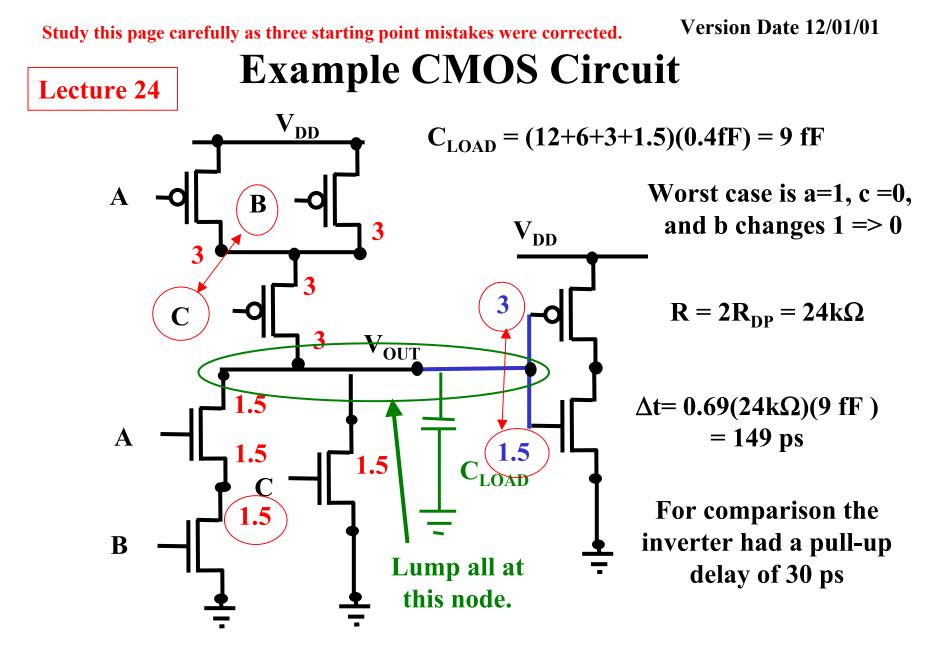

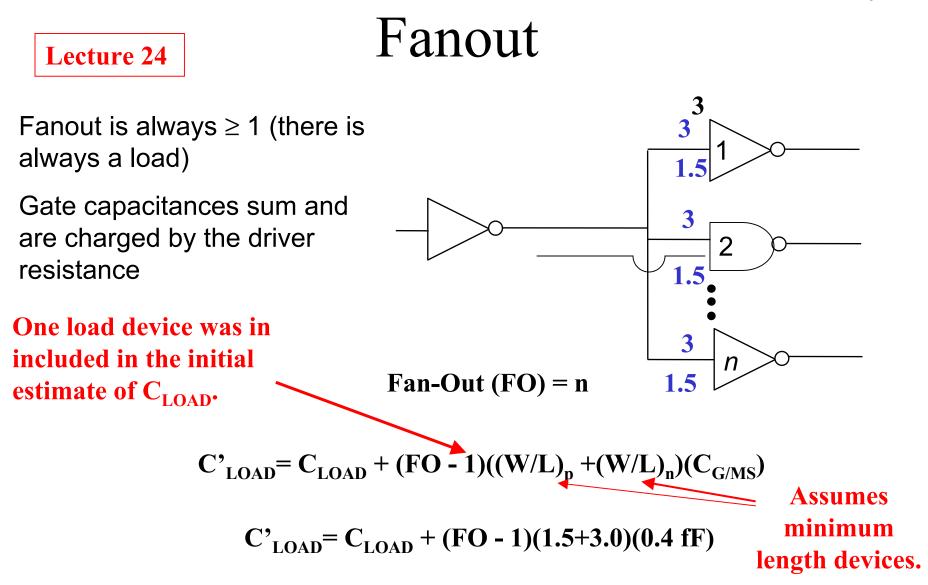

Lecture 24

Version Date 12/01/01

# **Coping with Power Consumption**

**D.C. POWER**

a.c. POWER

Tube:  $300V \times 20 \text{ mA} = 6W$

**Bipolar Transistor: 5V x 20 mA = 200 mW**

NMOS Transistor:  $5V \ge 200 \ \mu A = 1 \ mW$

**True of every gate!**

CMOS Transistors: 5V x 100 nA =  $0.5 \mu W$

$P_{SHORT-CIRCUIT} = (1/2) I_{SHORT-CIRCUIT} V_{DD} \tau_{30-70} f_{CLOCK}$ Assumes ½ of the gates change state  $P_{DYNAMIC} = (1/2) (60 \ \mu\text{A}) 2.5V (0.1ns) (10^9) = 7.5 \ \mu\text{W}$   $P_{DYNAMIC} = (1/2) (1/2) C V_{DD}^2 f_{CLOCK}$ Only the L =>H  $= (1/2) (1/2) (10 \ \text{fF}) (2.5)^2 10^9 = 15.6 \ \mu\text{W}$ True for only active gates. Copyright 2001, Regents of University of California

Lecture 25: 12/3/01 A.R. Neureuther

Version Date 12/01/01

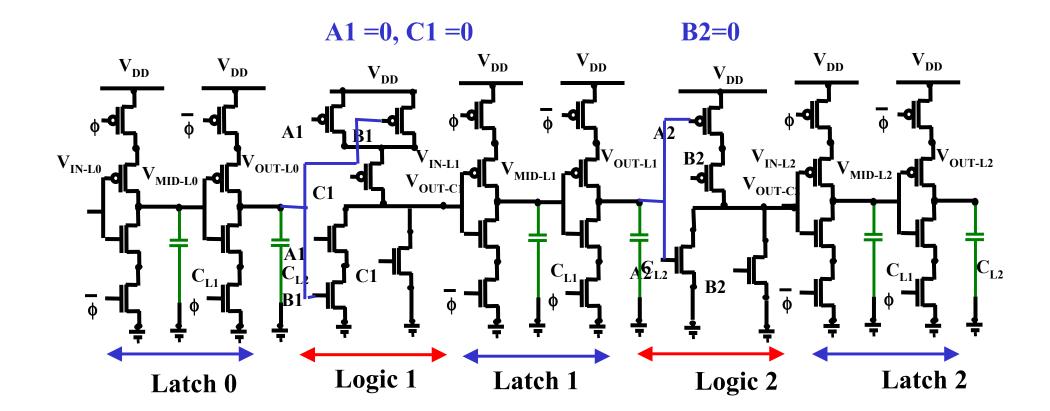

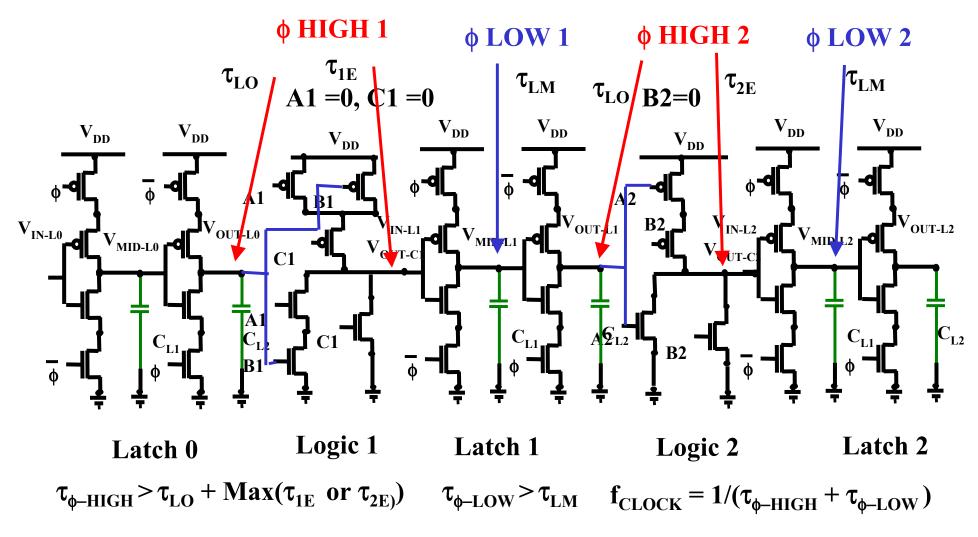

## **Combinatorial Logic and Clocked Latches: Wiring**

# Combinatorial Logic and Clocked Latches: Signal Flow

Copyright 2001, Regents of University of California

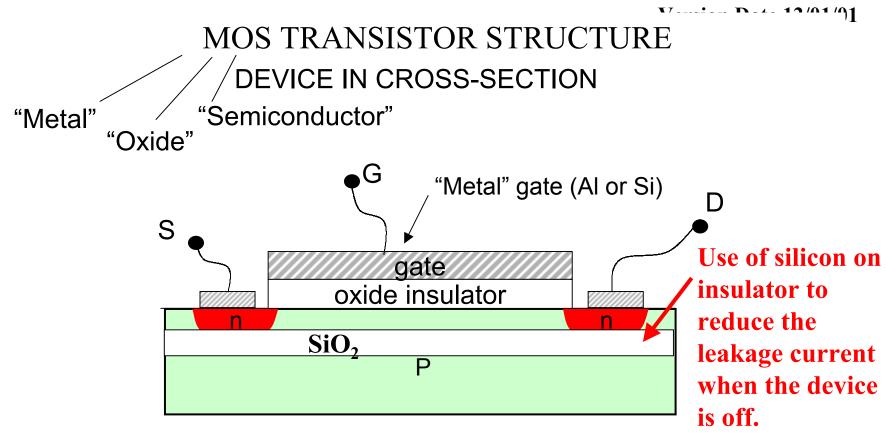

- In the absence of gate voltage, no current can flow between S and D.

- Above a certain gate to source voltage  $V_t$  (the "threshold"), electrons are induced at the surface beneath the oxide. (Think of it as a capacitor.)

- These electrons can carry current between S and D if a voltage is applied.

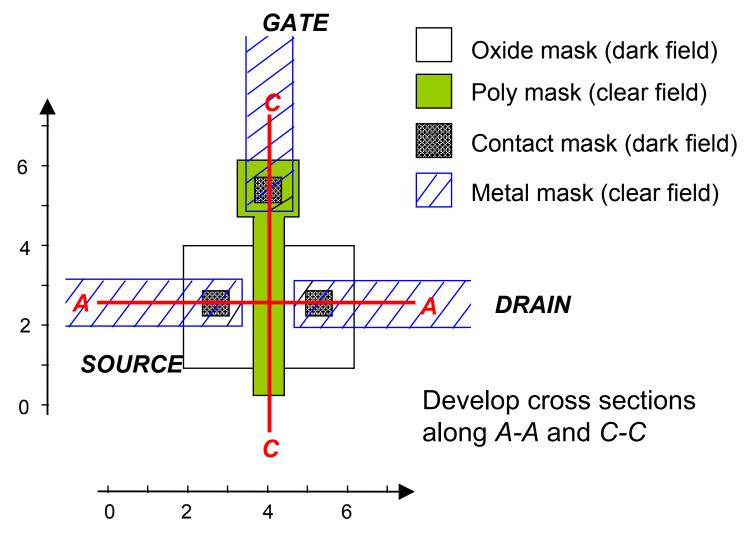

#### Drain contact W What are device dimensions? Gate (over oxide) Gate Length = L Source contact Thick oxide Gate Width = W on silicon Thin Gate Area (for oxide capacitance) is W x L (because that is the thin oxide area covered by the gate)

**MOS LAYOUT**

### **Basic CMOS Inverter**

Version Date 12/01/01

01

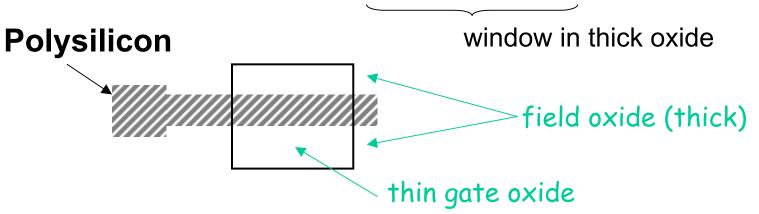

# **MOSFET "Identification"**

Poly line crossing a thin oxide region  $\rightarrow$  MOSFET

# Is oxide region inside the n-well? If Yes, then PMOS; If No, then NMOS

### **NMOS Transistor Layout**

("CAD View" = top view and 'Cut-Lines'))

Copyright 2001, Regents of University of California

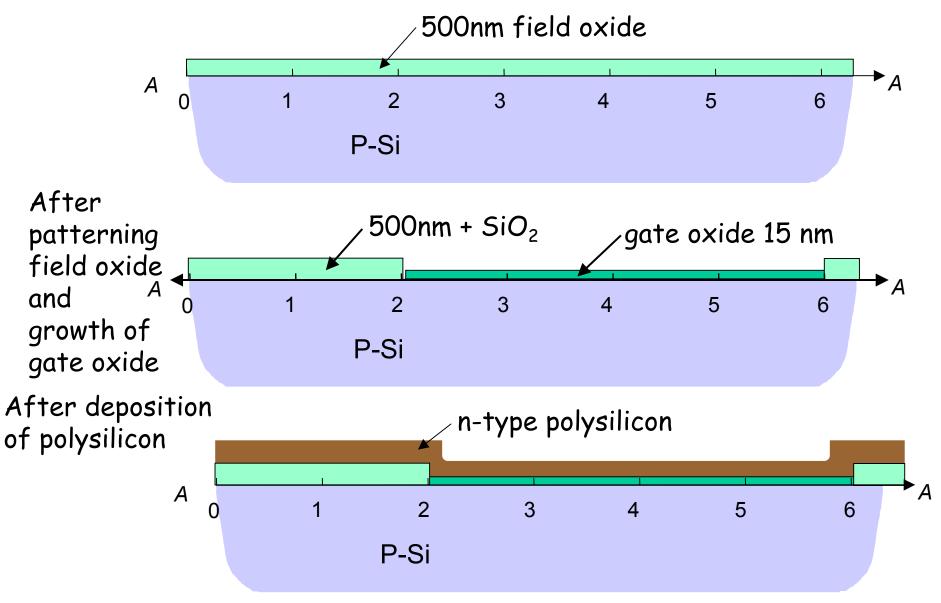

# **EXAMPLE NMOS Process Sequence**

- 1. Starting material: p-type silicon. Grow 500 nm (5000 Å) of "field"  $SiO_2$

- 2. Pattern oxide using the oxide mask

- 3. Grow 15 nm of "gate" SiO<sub>2</sub>

- 4. Deposit 500 nm of n-type polysilicon

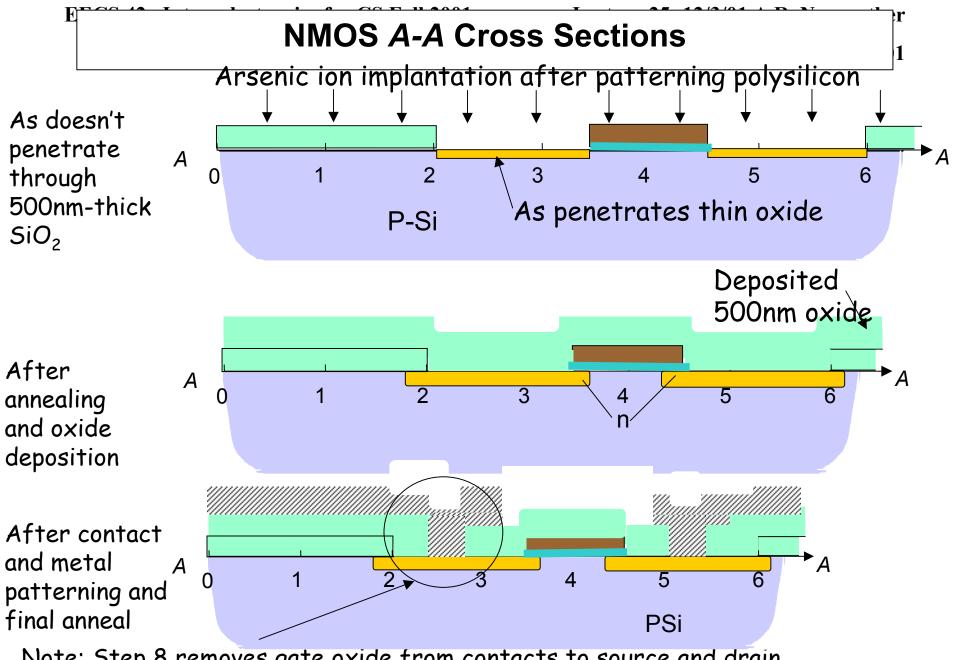

- 5. Pattern poly using the polysilicon mask

- 6. Implant arsenic (penetrates gate oxide, but not poly or field oxide) and anneal to form source and drain regions

- 7. Deposit 500 nm of SiO<sub>2</sub>

- 8. Pattern oxide using contact mask (etch sufficiently long to clear oxide from all contact windows)

- 9. Deposit 1  $\mu$ m of aluminum

- 10. Pattern aluminum with metal mask

- 11. Anneal at 450 °C to heal gate oxide damage and make good Si-Al contacts

# EECS 42Intro. electronics for CS Fall 2001Lecture 25: 12/3/01 A.R. NeureutherNMOS A-A Cross SectionsVersion Date 12/01/01

Copyright 2001, Regents of University of California

Note: Step 8 removes gate oxide from contacts to source and drain regions...otherwise, there's no current! (Al must touch n-type silicon!) Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001 Lecture 25: 12/3/01 A.R. Neureuther SIMPLer - D × File Options Step Number 10 Mask Key pattern metal • Step 5, poly field mask. Use the color • and the pattern with a clear 🔻 cyan. clearfield tep 8, oxide X's ▼ to display this mask. The current draw mode is: Idraw dark field Step 10, metal 🔵 erase 💥 clear field XXXXX XXXXX • F Delete Step Add Step Restart Calculate Cross-Section Materials Key N-type Si Neutral Si Oxide Polysilicor Metal Width:Height ratio is ~1:2

Copyright 2001, Regents of University of California

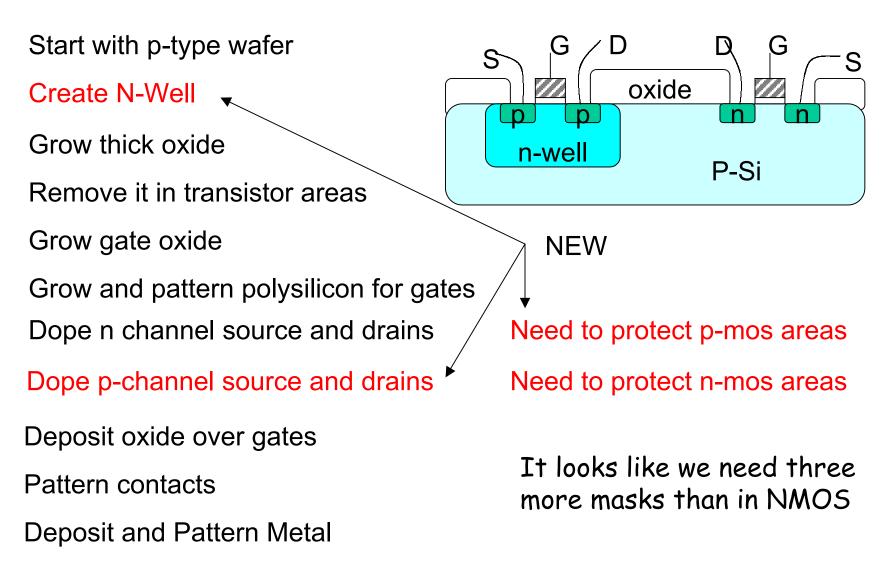

# **Conceptual CMOS Process**