**Lecture Review**

Lecture 25: 12/5/01 A.R. Neureuther

Version Date 12/04/01

#### **Review For Final**

#### FINAL EXAM

## 12:30-3:30 Friday, December 14<sup>th</sup>, F0295 Haas Closed Book, Device Equations Provided Bring calculator, Paper Provided

**Review Sessions:**

Proposed 5-6:30 PM Mon Dec 10

Proposed 5-6:30 PM Wed Dec 12

#### **Office hours:**

Professor Neureuther: 11 M,Tu, W, Th, F but 10-11 on F Dec 14th

TA's: TBA on web

# Congratulations Jason Gatt and Kevin Ha "Best in Show" in Tutbot/Calbot Contest

## EE 42 Final Exam: Design Guidelines

- Cover Material Since Midterm 2 at 2X compared to material on Midterms 1 and 2.

- About 100 of 200 points on material since Midterm 2 and about 100 points on material prior to Midterm 2

- Change to an accomplishment basis instead of B- average standard normal distribution.

- about 60 points of B level material

- about 60 points of A level material

- as a consequence exam average will be 120/200

- Results on 3 exams will be weighted by relative spread before merging to prevent large variation on final from wiping out Midterms.

## Key Material Since Midterm #2

- CMOS Static Type Analysis (big)

- Current given voltage, V<sub>OUT</sub> vs. V<sub>IN</sub>, Short Circuit Current, D.C.

power

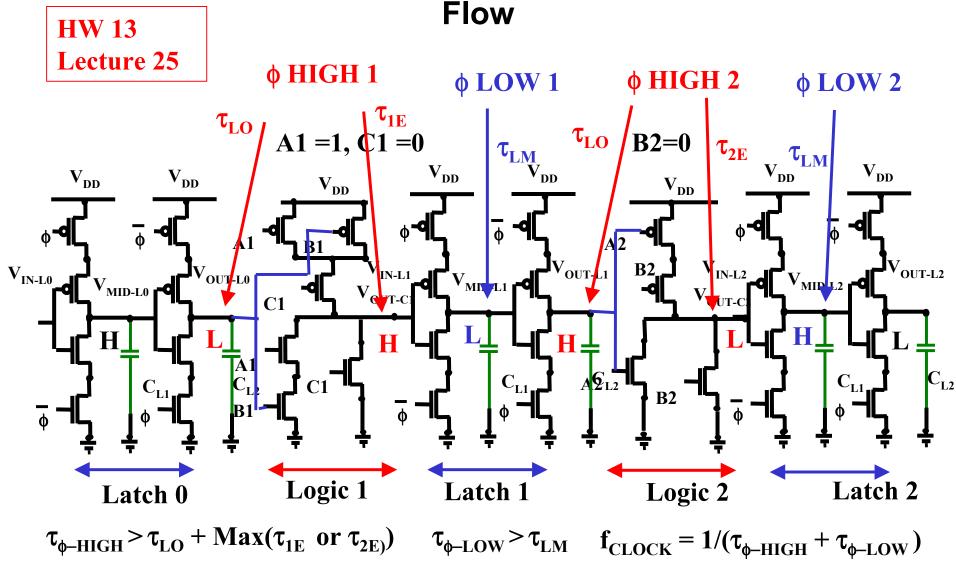

- CMOS Transient Analysis (big)

- Sources and amount of capacitance, propagation delay, a.c. power, clocked latches

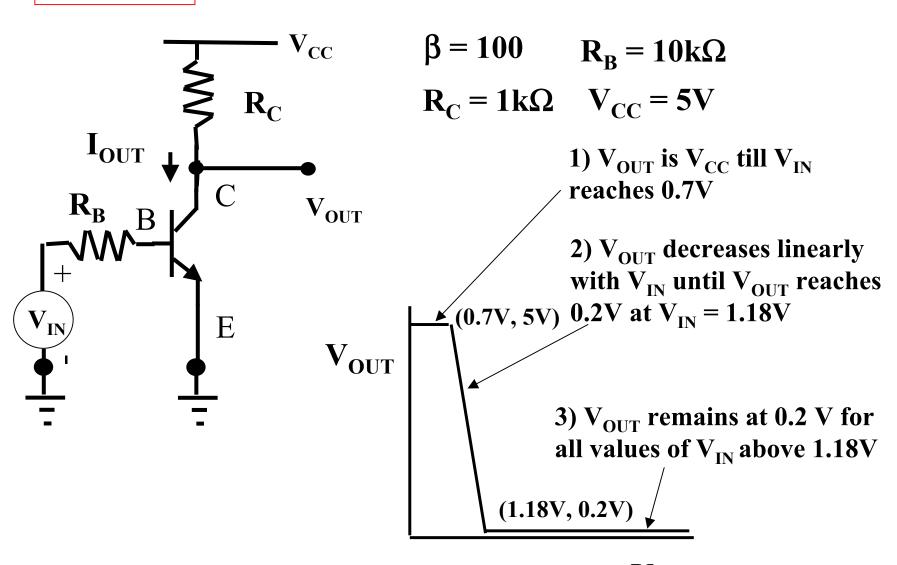

- Diode and Bipolar Transistor (medium)

- No physics but large signal analysis

- Physics (small)

- Resistance from carrier motion, field effect carriers and resistance

About 100 pts with about

10-20 pts C, 20-30 pts B, and 40-50 pts A.

Lecture 25: 12/5/01 A.R. Neureuther

Version Date 12/04/01

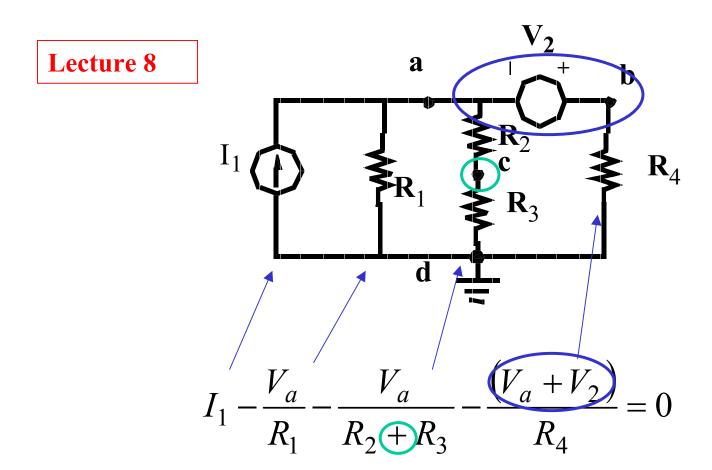

## Key Material Before Midterm #2

- Equivalent Circuits and Load Lines

- Simplify load circuits, find V<sub>OUT</sub> vs. VIN

- Dependent Sources

- Gain, input and output resistance

- Ideal Op-Amps

- Transients

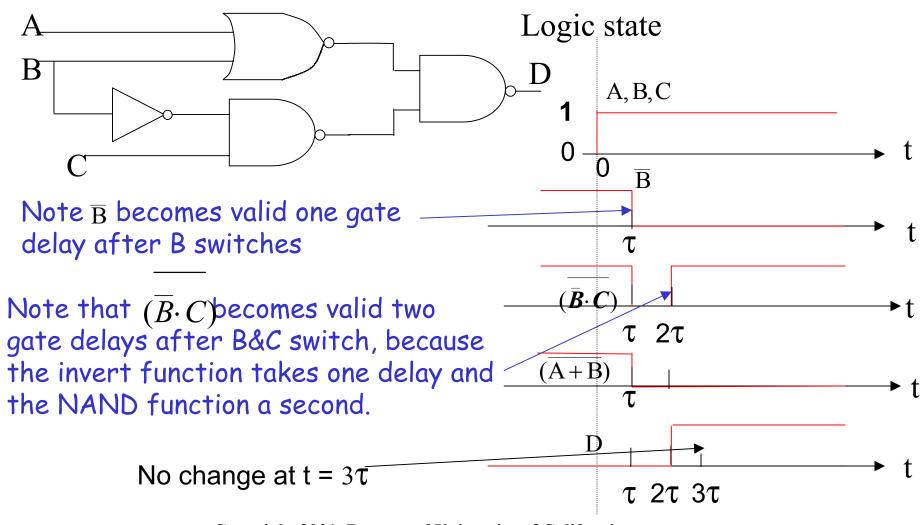

- Gates

- Logic function and timing diagrams

Total of about 100 Pts with about

50-60 pts C,

30-40 pts B, and

10-20 pts A.

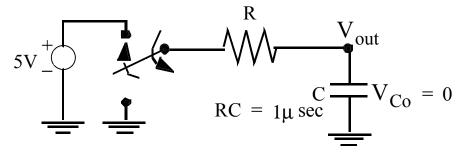

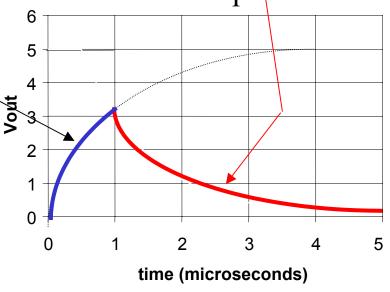

## PULSE: Output is Rising exponential then Falling exponential

#### Lecture 7

Example: Switch rises at t =0, falls at t = 0.1, 1 or 10μsec (Do 1μsec case)

Solution: for RC =  $1\mu$ sec: during the first rise V obeys:

$$V = 5[1 - e^{\frac{-t}{10^{-6}}}]$$

Thus at  $t = 1\mu sec$ , rising voltage reaches

$$5[1-e^{-1}] = 3.16V$$

Now starting at 1µsec we are discharging the capacitor so the form is a falling exponential with initial value 3.16 V:

What is equation?

Lecture 25: 12/5/01 A.R. Neureuther

**Version Date 12/04/01**

#### **EXAMPLE WITH BOTH SPECIAL CASES**

#### Lecture 10

Version Date 12/04/01

## How to Combine Gate to Produce a Desired Logic Function? (More basic Logical Synthesis)

#### Example:

| Α | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

$$\begin{array}{c} A - \circ \\ B - \circ \\ C \end{array} \qquad F$$

$$\begin{array}{c} A - \circ \\ A - \circ \\ B - \circ \\ C - \circ \end{array}$$

$$F = \overline{A} \overline{B} C + AB \overline{C}$$

Lecture 25: 12/5/01 A.R. Neureuther

Version Date 12/04/01

#### **Lecture 11**

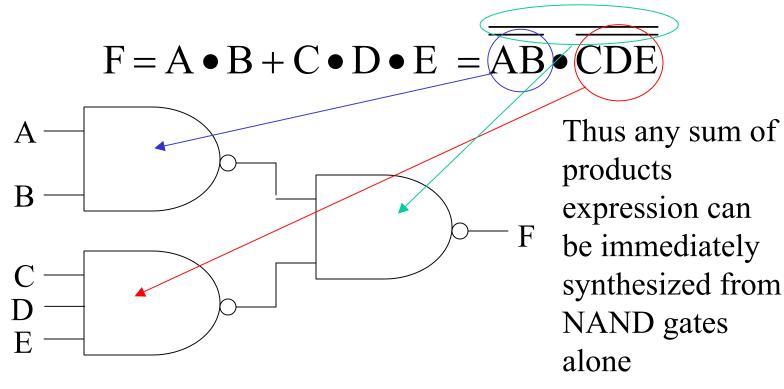

## Logical Synthesis Guided by DeMorgan's Theorem

DeMorgan's Theorem:

$$A + B + C = \overline{A \overline{B} \overline{C}}$$

or  $\overline{A} + \overline{B} + \overline{C} = \overline{A \overline{B} \overline{C}}$

Example of Using DeMorgan's Theorem:

Copyright 2001, Regents of University of California

#### **Lecture 11**

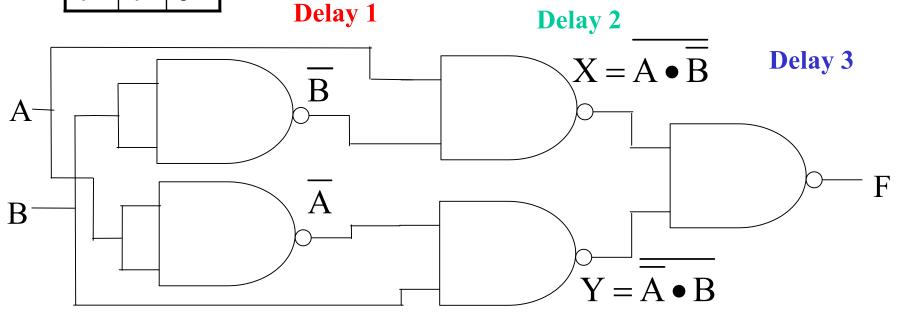

#### **Logical Synthesis of XOR**

| Α | В | F |  |

|---|---|---|--|

| 0 | 0 | 0 |  |

| 0 | 1 | 1 |  |

| 1 | 0 | 1 |  |

| 1 | 1 | 0 |  |

$$F = A \bullet \overline{B} + \overline{A} \bullet B$$

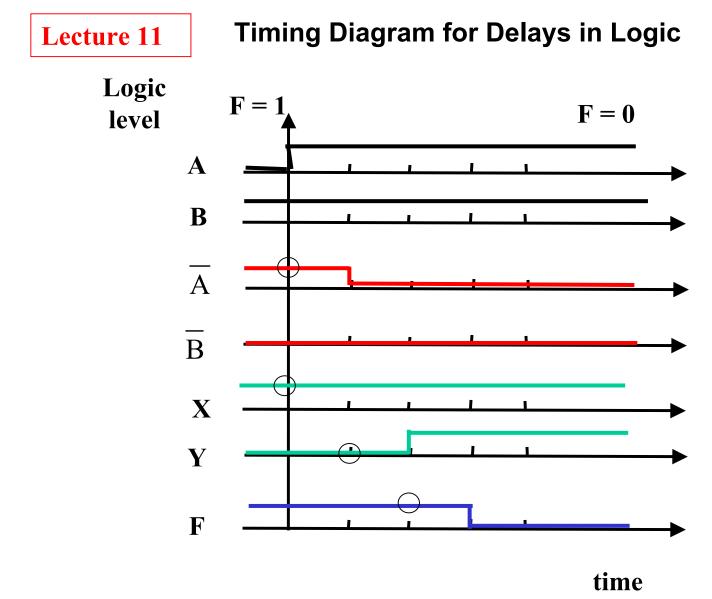

We Need a Timing Diagram!

Copyright 2001, Regents of University of California

Lecture 11

#### **TIMING DIAGRAMS**

Show transitions of variables vs time

Lecture 25: 12/5/01 A.R. Neureuther

Version Date 12/04/01

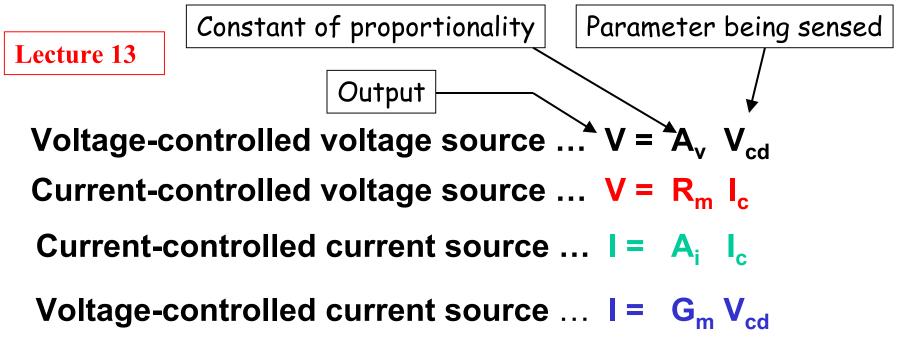

### The 4 Basic Linear Dependent Sources

Lecture 13

**Version Date 12/04/01**

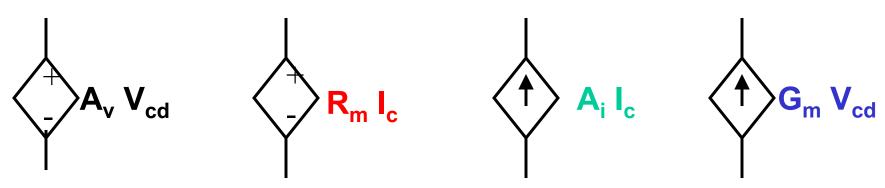

#### **EXAMPLE CIRCUIT: INCREASED OUTPUT RESISTANCE**

Intuitive Explanation:  $GmV_{IN}$  burps current which has to also go through  $R_0$ . This raises  $v_{TEST}$  and the output impedance  $v_{TEST}/i_{TEST}$

Finish this in the homework

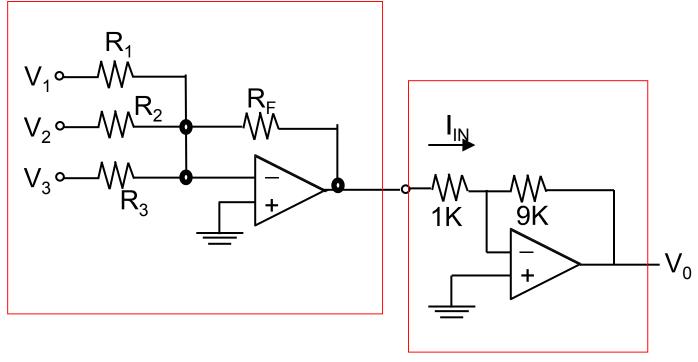

**Lecture 14**

#### **CASCADE OP-AMP CIRCUITS**

How do you get started on finding  $V_0$ ?

**Hint: Identify Stages**

Hint: I<sub>IN</sub> does not affect V<sub>O1</sub>

See the further examples of op-amp circuits in the reader Copyright 2001, Regents of University of California

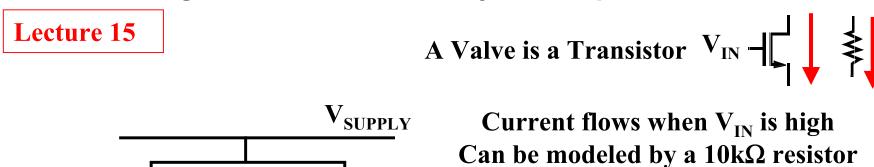

#### **Logic Gates – How are they built in practice?**

Pull up

Network

Valves in Series => NAND

**Valves in Parallel => NOR**

What goes in this box?

How does it affect digital performance?

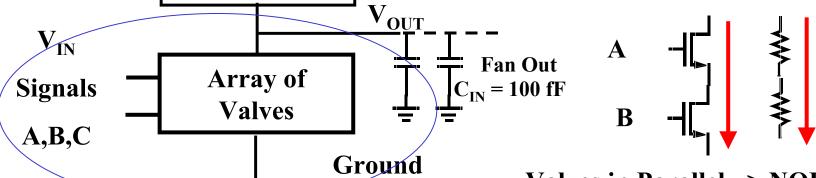

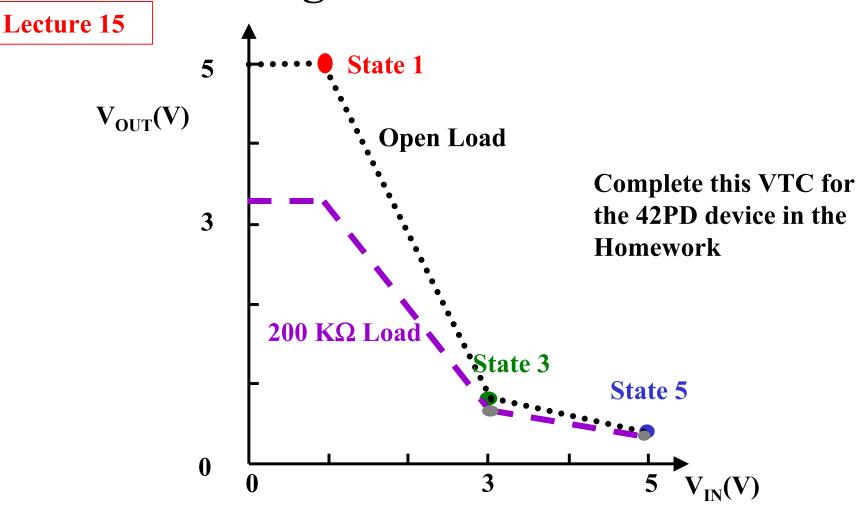

## Composite Current Plot for the 42PD Circuit with 200kΩ Load to Ground

#### Lecture 15

Copyright 2001, Regents of University of California

# Voltage Transfer Function for the 42PD Logic Circuit w/wo Load

Copyright 2001, Regents of University of California

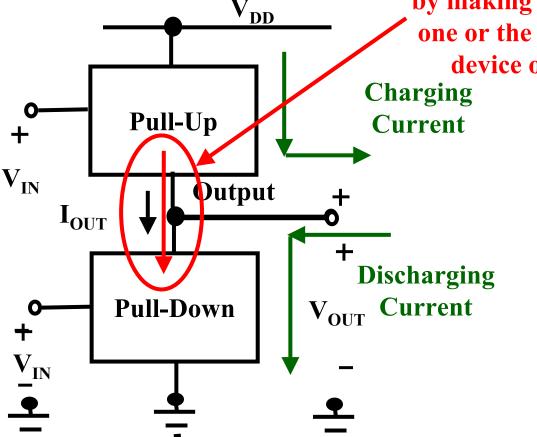

# Pull-Down and Pull-Up Must Complement Rather Than Fight Each Other Reduce the Short-

Lecture 16

Rather Than Fight Each Other Reduce the Short-Circuit Current by making either one or the other device off.

Input for State Control Signal

**Share Same Signal**

**Input for State Control Signal**

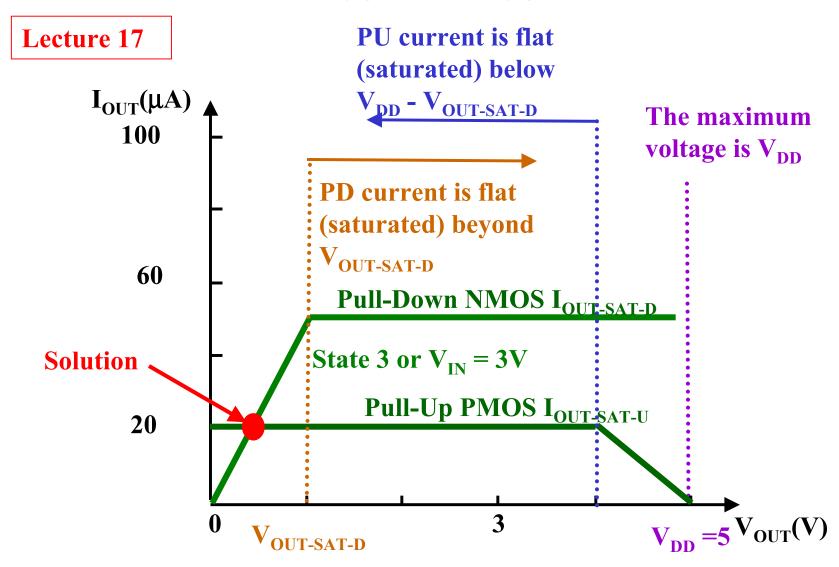

## Composite I<sub>OUT</sub> vs. V<sub>OUT</sub> for CMOS

Copyright 2001, Regents of University of California

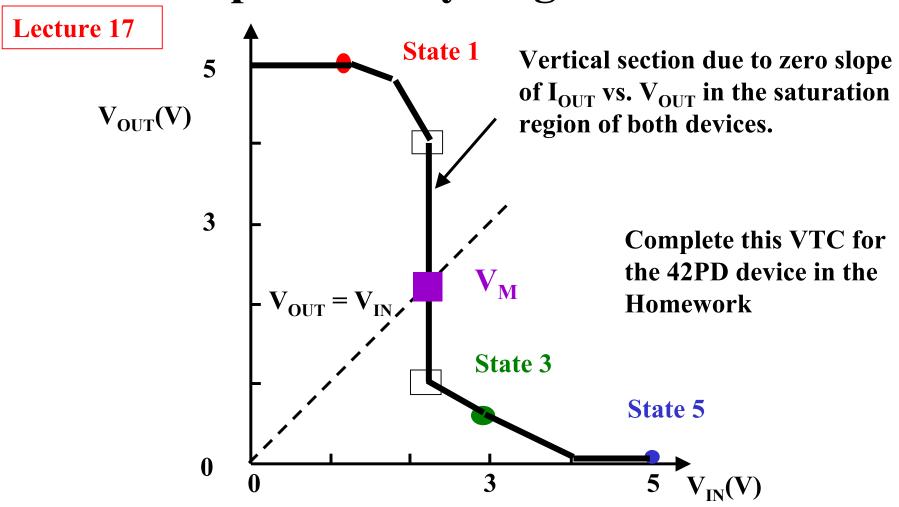

# Voltage Transfer Function for the Complementary Logic Circuit

Copyright 2001, Regents of University of California

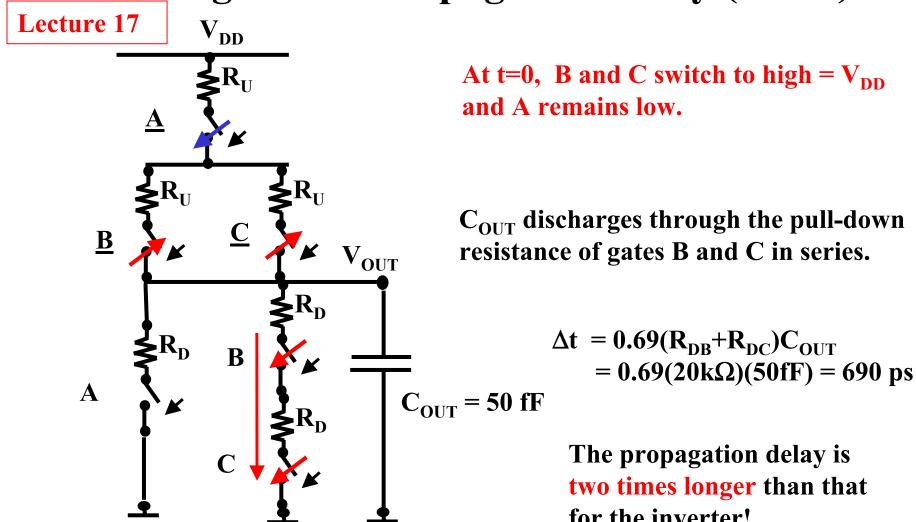

#### Lecture 17

## Method for Finding V<sub>M</sub>

At  $V_{M}$ ,

- $1) \quad \mathbf{V_{OUT}} = \mathbf{V_{IN}} = \mathbf{V_{M}}$

- 2) Both devices are in saturation

- $\mathbf{3)} \quad \mathbf{I}_{\mathbf{OUT\ PD}} = \mathbf{I}_{\mathbf{OUT\ PU}}$

$$I_{OUT-PD} = k_D (V_{IN} - V_{TD}) V_{TD} = I_{OUT-PU} = k_U (V_{DD} - V_{IN}) - V_{TU}) V_{TU}$$

Substitute  $V_{M}$

**Solve for V**<sub>M</sub>

Example Result: When  $k_D = k_P$  and  $V_{TD} = V_{TU}$ ,  $V_M = V_{DD}/2$

## Switched Equivalent Resistance Model

#### Lecture 17

The above model assumes the device is an ideal constant current source.

- 1) This is not true below  $V_{OUT-SAT-D}$  and leads to in accuracies.

- 2) Combining ideal current sources in networks with series and parallel connections is problematic.

Instead define an equivalent resistance for the device by setting  $0.69R_DC$  equal to the  $\Delta t$  found above

$\Delta t = \frac{C_{OUT}V_{DD}}{2I_{OUT-SAT-D}} = 0.69R_DC_{OUT}$

This gives

$$R_D = \frac{V_{DD}}{2 \cdot (0.69) I_{OUT-SAT-D}} \approx \frac{3}{4} \frac{V_{DD}}{I_{OUT-SAT-D}} = \frac{3}{4} \frac{5V}{100 \mu A} = 37.5 k\Omega$$

Each device can now be replaced by this equivalent resistor.

## **Logic Gate Propagation Delay (Cont.)**

The propagation delay is two times longer than that for the inverter!

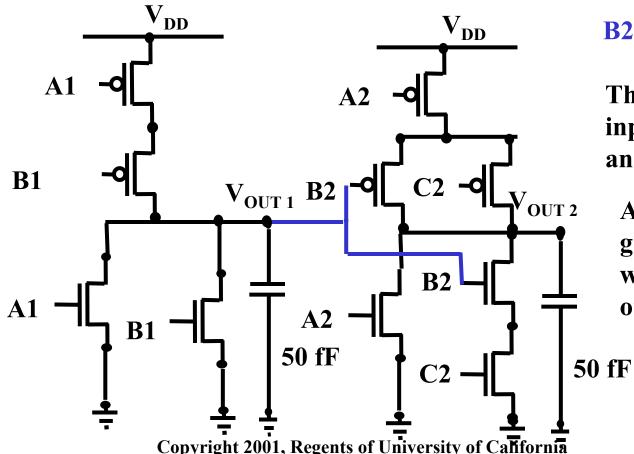

#### **Lecture 18**

## Logic Gate Cascade

To avoid large resistance due to many gates in series, logic functions with 4 or more inputs are usually made from cascading two or more 2-4 input blocks.

$$B2 = V_{OUT 1}$$

The four independent input are A1, B1, A2 and C2.

A2 high discharges gate 2 without even waiting for the output of gate 1.

C2 high and A2 low makes gate 2 wait for Gate 1 output

#### Lecture 18

**Version Date 12/04/01**

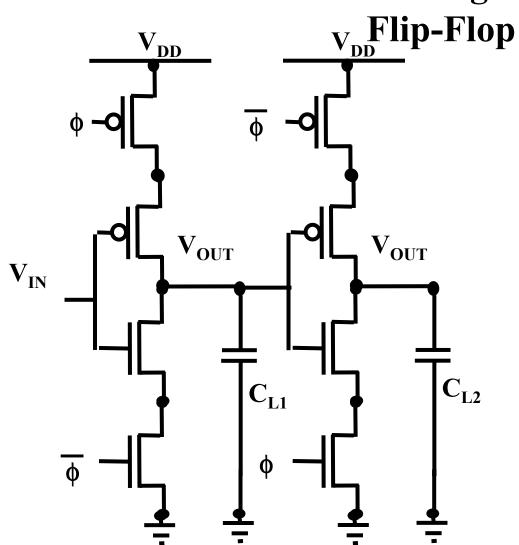

### A Double Latch is an Edge-Triggered D Type

During the low part of the clock cycle this circuit records the input value and when the clock goes high drives  $V_{OUT\,2}$  to the voltage level that arrived. (This is the classic function of a D flip-flop.)

Note that this circuit is not fooled by noise on the input and makes its decision on the rising edge of the clock (edge-triggered).

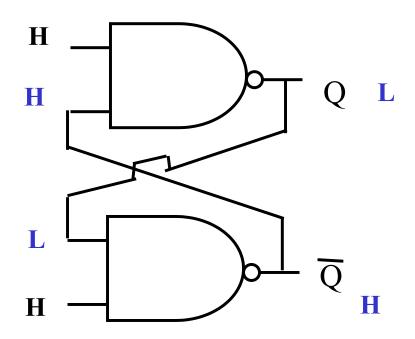

## **Feedback Can Provide Memory**

**Lecture 19**

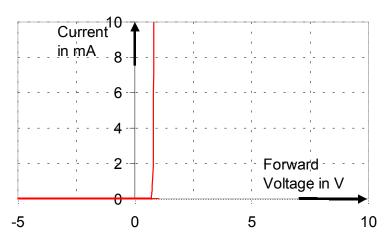

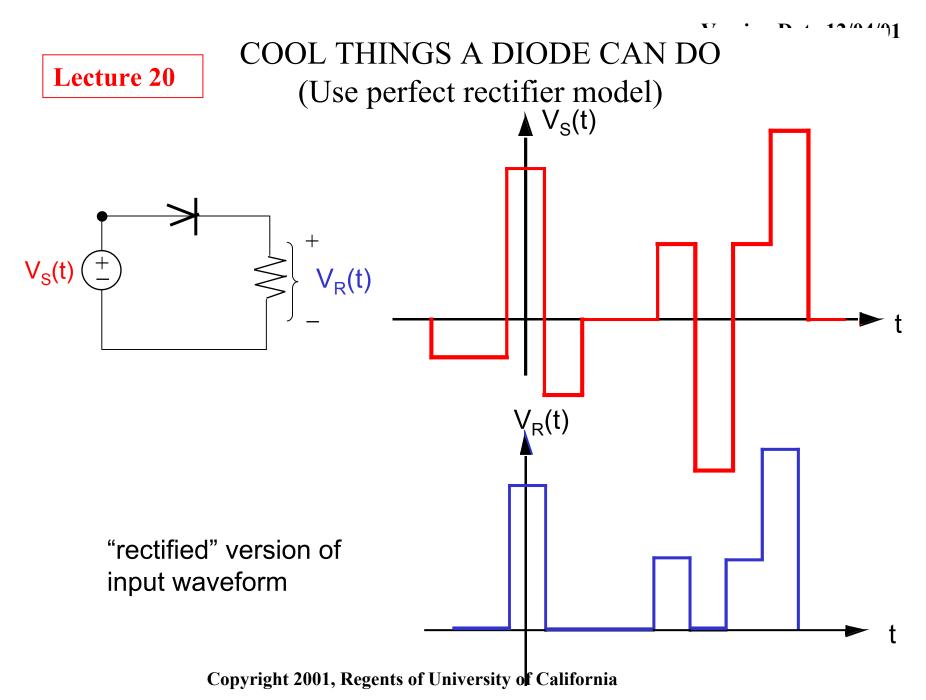

## Lecture 20 DIODE I-V CHARACTERISTICS AND MODELS 12/04/01

The equation  $I = I_0 exp({}^{qV}/kT - 1)$  is graphed below for  $I_0 = 10^{-15} A$

The characteristic is described as a "rectifier" – that is, a device that permits current to pass in only one direction. (The hydraulic analog is a "check value".) Hence the symbol:

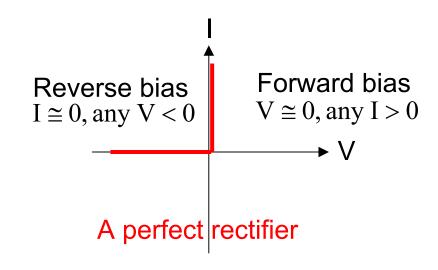

#### Simple "Perfect Rectifier" Model

If we can ignore the small forwardbias voltage drop of a diode, a simple effective model is the "perfect rectifier," whose I-V characteristic is given below:

### Lecture 21 ppn Bipolar Transistor: V<sub>OUT</sub> vs. V<sub>IN</sub>

2/04/01

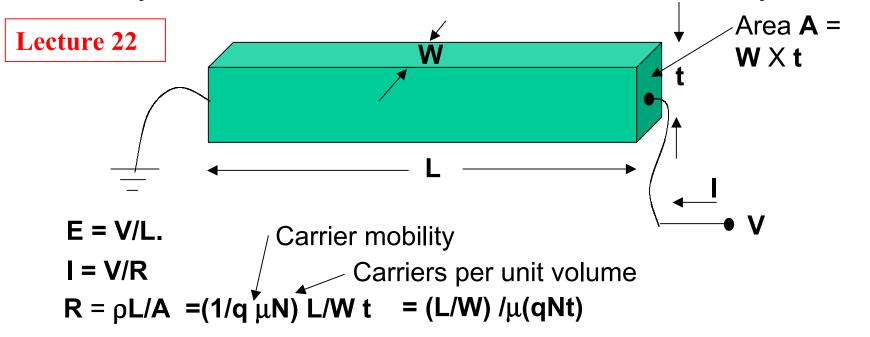

Physics of Current Flow, Resistance, Resistivity

But **q N t** has the dimensions of charge per unit area and represents the charge per unit area in a film of thickness **t** when the film has **N** carriers/cm<sup>3</sup> and is **t** units thick. Thus we call **q N t** the "**Q**" and

$$R = (L/W)/ \mu Q = L/W R_{\square}$$

Where  $\mathbf{R}_{\square}$  is the resistance of a "square" of the film. Clearly if L is four times W, then R = 4  $\mathbf{R}_{\square}$ .

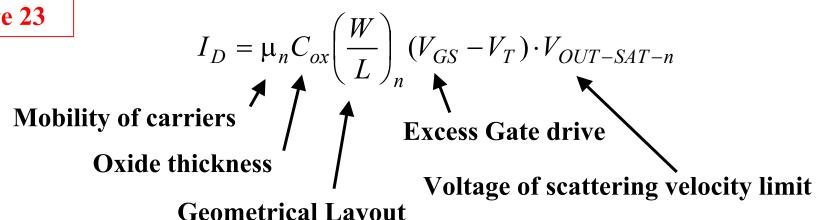

#### Relation of Current to Physical Parameters

#### Lecture 23

**Geometrical Layout**

$$\mu_n = 500 \left( \frac{cm^2}{V_S} \right) \qquad \mu_p = 150 \left( \frac{cm^2}{V_S} \right)$$

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} = \frac{\left( 8.85x10^{-14} F/cm \right) \left( 3.9 \right)}{6x10^{-7} cm} = 5.75x10^{-7} F/cm^2$$

$$V_{OUT-SAT-n} = E_{Crit} \cdot L = 10^4 \left( \frac{V}{cm} \right) \cdot 0.25x10^{-4} cm = 0.25V$$

Lecture 25: 12/5/01 A.R. Neureuther

**Version Date 12/04/01**

## CMOS Device Parameters at 0.25µm

Lecture 23

Gate length is  $0.25 \mu m = 250 nm$

$$V_{DD} = 2.5V$$

|      | $V_{T}(V)$ | $V_{OUT\text{-}SAT}(V)$ | k' (μΑ/V <sup>2</sup> ) |

|------|------------|-------------------------|-------------------------|

| NMOS | 0.43       | 0.63                    | 100                     |

| PMOS | 0.4        | 1                       | 25                      |

These parameters are from re-fitting I vs. V data in Chapter 3 of the EECS 141 Text Book by Rabaey with saturation current model we are using in EE42. Here  $V_{IN} = V_{DD}$

$$I_{OUT-SAT-D} = k_D (V_{IN} - V_{TD}) V_{OUT-SAT-D}$$

is used to maximum I<sub>DS</sub>

$$I_{OUT-SAT-D} = \left(100 \,\mu A/V^2\right) \left(\frac{0.375}{0.25}\right) (2.5V - 0.43V)(0.63V) = 196 \,\mu A$$

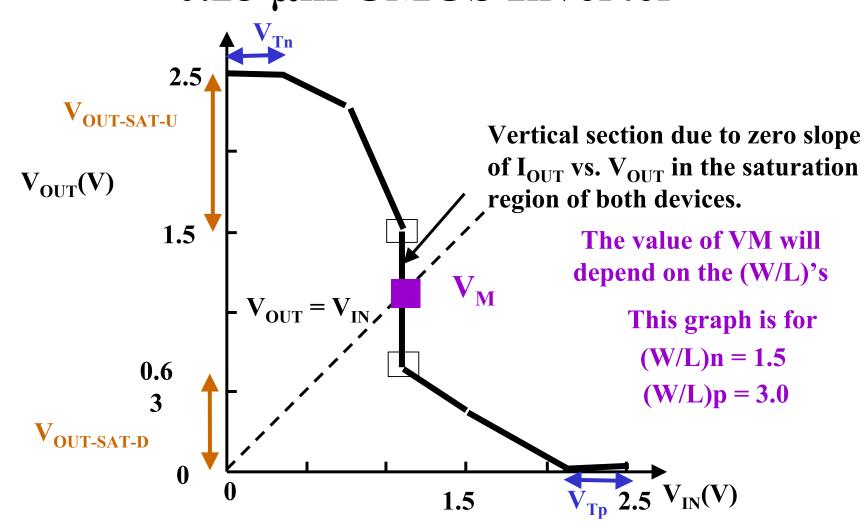

## Voltage Transfer Function for the Lecture 23 0.25 µm CMOS Inverter

Copyright 2001, Regents of University of California

Lecture 23

**Version Date 12/04/01**

## Finding $V_M$ for 0.25 $\mu m$ Inverter

At  $V_{M}$ ,

- $1) \quad \mathbf{V}_{\mathbf{OUT}} = \mathbf{V}_{\mathbf{IN}} = \mathbf{V}_{\mathbf{M}}$

- 2) Both devices are in saturation

- 3)  $I_{OUT-SAT-n} = I_{OUT-SAT-p}$  Result will depend on (W/L) ratios.  $I_{OUT-SAT-n} = k'_n \left(\frac{W}{L}\right)_n (V_{IN} V_{Tn}) V_{OUT-SAT-n} = I_{OUT-SAT-p} = k'_p \left(\frac{W}{L}\right)_p (V_{DD} V_{IN}) V_{Tp}) V_{OUT-SAT-p}$ Substitute  $V_{M}$  Solve for  $V_{M}$

For  $(W/L)_n = 1.5$  and  $(W/L)_p = 3.0 V_M$  is 1.17V

Lecture 23

Version Date 12/04/01

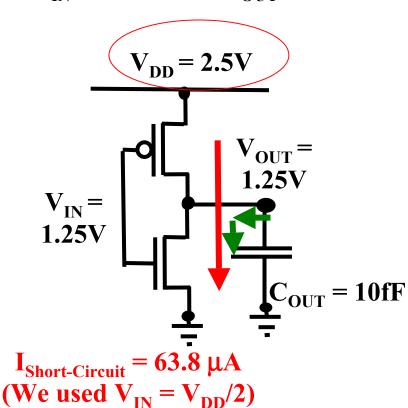

#### **CMOS Inverter in Short-Circuit Condition**

Assume the CMOS inverter from above with  $V_{IN} = 1.25V$  and  $V_{OUT} = 1.25V$  driving a 10 fF capacitor

What happens to the output signal?

The capacitor slowly discharges to try to find an output voltage that balances the NMOS and PMOS currents for the given value of  $V_{\rm IN}$ .

$$\frac{\partial V}{\partial t} = \frac{I}{C} = \frac{13.7 \,\mu A}{10 \, fF} = 1.37 \big( V / ns \big)$$

$$I_{Discharge\_Load} = 13.7 \mu A$$

(We Used  $V_{IN} = V_{DD}/2$ )

Study this page carefully as three starting point mistakes were corrected.

**Version Date 12/04/01**

#### Lecture 24

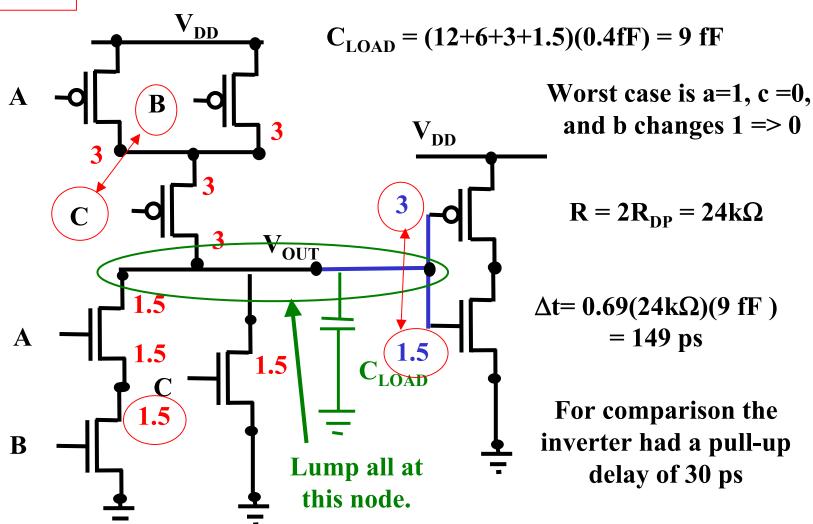

### **Example CMOS Circuit**

Varsian Data 17/04/01

#### Lecture 24

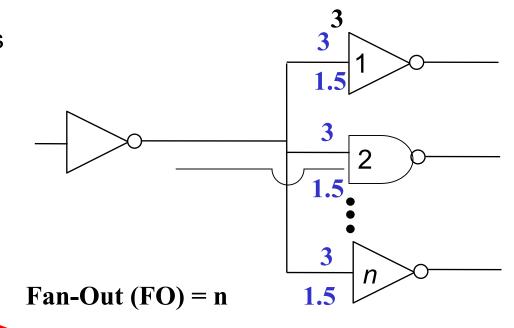

## Fanout

Fanout is always ≥ 1 (there is always a load)

Gate capacitances sum and are charged by the driver resistance

One load device was in included in the initial estimate of  $C_{LOAD}$ .

$$C'_{LOAD} = C_{LOAD} + (FO - 1)((W/L)_p + (W/L)_n)(C_{G/MS})$$

$$C'_{LOAD} = C_{LOAD} + (FO - 1)(1.5 + 3.0)(0.4 \text{ fF})$$

Assumes minimum length devices.

Lecture 25: 12/5/01 A.R. Neureuther

Lecture 24

**Version Date 12/04/01**

## **Coping with Power Consumption**

**D.C. POWER**

a.c. POWER

Tube:  $300V \times 20 \text{ mA} = 6W$

Bipolar Transistor:  $5V \times 20 \text{ mA} = 200 \text{ mW}$

NMOS Transistor:  $5V \times 200 \mu A = 1 \text{ mW}$

True of every gate!

CMOS Transistors:  $5V \times 100 \text{ nA} = 0.5 \mu W$

P<sub>SHORT-CIRCUIT</sub> = (1/2)  $I_{SHORT-CIRCUIT}$   $V_{DD}$   $\tau_{30-70}$   $f_{CLOCK}$  Assumes ½ of the gates  $= (1/2) (60 \ \mu A) \ 2.5 V (0.1 ns) (10^9) = 7.5 \ \mu W$  change state  $P_{DYNAMIC} = (1/2)(1/2) \ C \ V_{DD}^2 \ f_{CLOCK}$  Only the L =>H  $= (1/2) (1/2)(10 \ fF) (2.5)^2 \ 10^9 = 15.6 \ \mu W$  takes energy from  $V_{DD}$

## Combinatorial Logic and Clocked Latches: Signal Flow