| EECS 42 Intro. Digital Electronics Fall 2003 Lecture 10: 09//25/03 A.R. Neureuth |

|----------------------------------------------------------------------------------|

| Version Date 09/14/                                                              |

| EECS 42 Introduction to Digital Electronics                                      |

| Andrew R. Neureuther                                                             |

| Lecture # 10 Prof. King: Basic Digital Blocks                                    |

| • 20 Min Quiz                                                                    |

| <b>Basic Circuit Analysis and Transients</b>                                     |

| Logic Functions, Truth Tables                                                    |

| Circuit Symbols, Logic from Circuit                                              |

| Schwarz and Oldham 11.1, 11.2 393-402                                            |

| Midterm 10/2: Lectures # 1-9: 4 Topics – See slide 2<br>Length/Credit Review TBA |

| http://inst.EECS.Berkeley.EDU/~ee42/                                             |

|                                                                                  |

| EECS 42 Intro. Digital Electronics Fall 2003                                                                      | Lecture 10: 09//25/03 A.R. Neureuther |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                                                                                                                   | Version Date 09/14/03                 |

| Logical Expre                                                                                                     | ssions                                |

|                                                                                                                   |                                       |

| Standard logic notation :                                                                                         |                                       |

| AND: "dot" Examples: X = A ·                                                                                      | $B ; Y = A \cdot B \cdot C$           |

| OR : "+ sign" Examples: W = A                                                                                     | +B ; Z = A+B+C                        |

| NOT: "bar over symbol for comple                                                                                  | ment" Example: $Z = \overline{A}$     |

| With these basic operations we can expression.                                                                    | construct any logical                 |

| Order of operation: NOT, AND, OR<br>expression is performed after the ex<br>there is an implied parenthesis, e.g. | pression is evaluated, so             |

# EECS 42 Intro. Digital Electronics Fall 2003 Lecture 10: 09//25/03 A.R. Neureuther Version Date 09/14/03 First Midterm Exam: Topics

- Basic Circuit Analysis (KVL, KCL)

- Equivalent Circuits and Graphical Solutions for Nonlinear Loads

- Transients in Single Capacitor Circuits

- Node Analysis Technique and Checking Solutions

Exam is in class 9:40-10:45 AM, Closed book, Closed notes, Bring a calculator, Paper provided

### EECS 42 Intro. Digital Electronics Fall 2003 Lecture 10: 09//25/03 A.R. Neureuther Version Date 09/14/03

## Logic Function Example

• Boolean Expression:  $H = (A \cdot B \cdot C) + T$

This can be read H=1 if (A and B and C are 1) or T is 1, or H is true if all of A,B,and C are true, or T is true, or The voltage at node H will be high if the input voltages at nodes A, B and C are high or the input voltage at node T is high

| EECS 42 Intro. Digital Electronics Fall 2003                                                                                                                                     | Lecture 10: 09//25/03 A.R. Neureuther |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

| Logic Func                                                                                                                                                                       | Version Date 09/14/03                 |  |  |  |

| Logic Expression : To create logic values we will define "True" , as<br>Boolean 1 and "False" , as Boolean 0.                                                                    |                                       |  |  |  |

| Moreover we can associate a logic variable with a circuit node. Typically we<br>associate logic 1 with a high voltage (e.g. 2V) and and logic 0 with a low<br>voltage (e.g. 0V). |                                       |  |  |  |

| Example: The logic variable H is true (H=1) if (A and B and C are 1) or T is true (logic 1), where all of A,B,C and T are also logical variables.                                |                                       |  |  |  |

| Logic Statement: H = 1 if A and                                                                                                                                                  | B and C are 1 or T is 1.              |  |  |  |

| We use "dot" to designate logical "and" and "+" to designate logical or in<br>switching algebra. So how can we express this as a Boolean<br>Expression?                          |                                       |  |  |  |

| Boolean Expression: $H = (A \cdot B \cdot G)$                                                                                                                                    | C) + ⊤                                |  |  |  |

| Note that there is an order of operation performed before OR. Thus the parentl                                                                                                   |                                       |  |  |  |

| Convright 2003. Reseases of University of California                                                                                                                             |                                       |  |  |  |

| EECS 42 Intro. Digital Electronics Fall 2003                                                   | Lecture 10: 09//25/03 A.R. Neureuther |  |  |  |  |

|------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

|                                                                                                | Version Date 09/14/03                 |  |  |  |  |

| Logic Function Example 2                                                                       |                                       |  |  |  |  |

| You wish to express under which conditions your burglar alarm goes off (B=1):                  |                                       |  |  |  |  |

| If the "Alarm Test" button is pressed (A=1)                                                    |                                       |  |  |  |  |

| OR if the Alarm is Set (S=1) AND { the door is opened (D=1) OR the trunk is opened (T=1)}      |                                       |  |  |  |  |

| Boolean Expression: B = A + S(D +                                                              | Τ)                                    |  |  |  |  |

| This can be read B=1 if A = 1 or S=1 AN                                                        | D (D OR T =1), i.e.                   |  |  |  |  |

| B=1 if {A = 1} or {S=1 AND (D OR T =1)}                                                        |                                       |  |  |  |  |

| or                                                                                             |                                       |  |  |  |  |

| B is true IF {A is true} OR {S is true AND D                                                   | OR T is true}                         |  |  |  |  |

| or                                                                                             |                                       |  |  |  |  |

| The voltage at node H will be high if {the in<br>{the input voltage at S is high and the volta |                                       |  |  |  |  |

| Copyright 2003, Regents of University of California                                            |                                       |  |  |  |  |

|                                                                                                |                                       |  |  |  |  |

| EECS 42 Intro. Digital Electronics Fal | I 2003 Lecture 10: 09//25/03 A.R. Neureuther                               |  |  |  |

|----------------------------------------|----------------------------------------------------------------------------|--|--|--|

|                                        | Version Date 09/14/03                                                      |  |  |  |

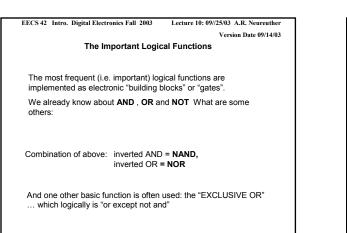

| Some Important Logical Functions       |                                                                            |  |  |  |

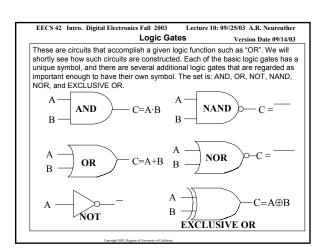

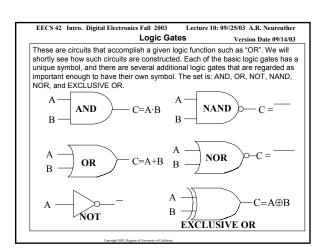

| • "AND"                                | $A \cdot B$ (or $A \cdot B \cdot C$ )                                      |  |  |  |

| ». "OR"                                | A+B (or $A+B+C+D$ )                                                        |  |  |  |

| • "INVERT" or "NOT"                    | not A (or $\overline{A}$ )                                                 |  |  |  |

| • "not AND" = NAND                     | $\overline{AB}$ (only 0 when A and B=1)                                    |  |  |  |

| • "not OR" = NOR                       | $\overline{A+B}$ (only 1 when $A=B=0$ )                                    |  |  |  |

| • exclusive OR = XOR                   | $A \oplus B$ (only 1 when A, B differ)<br>i.e., $A + B$ except $A \cdot B$ |  |  |  |

| Conversite 2003. Research of Unive     | arvity of California                                                       |  |  |  |

| EECS 42 Intro. Digital Electro | onics Fall 20              | 03 Lectu   | re 10: 09//25 | 03 A.R. Neureuther    |

|--------------------------------|----------------------------|------------|---------------|-----------------------|

|                                |                            |            |               | Version Date 09/14/03 |

| Evaluation of Log              | ical Expr                  | essions wi | ith "Truth    | n Tables"             |

| Truth Table for                | or Logic E                 | xpression  | H = (A ·      | B · C) + T            |

| А                              | В                          | С          | Т             | Н                     |

| 0                              | 0                          | 0          | 0             | 0                     |

| 0                              | 0                          | 1          | 0             | 0                     |

| 0                              | 1                          | 0          | 0             | 0                     |

| 0                              | 1                          | 1          | 0             | 0                     |

| 1                              | 0                          | 0          | 0             | 0                     |

| 1                              | 0                          | 1          | 0             | 0                     |

| 1                              | 1                          | 0          | 0             | 0                     |

| 1                              | 1                          | 1          | 0             | 1                     |

| 0                              | 0                          | 0          | 1             | 1                     |

| 0                              | 0                          | 1          | 1             | i i                   |

| 0                              | 1                          | 0          | 1             | 1                     |

| 0                              | 1                          | 1          | 1             | 1                     |

| 1                              | 0                          | 0          | 1             | 1                     |

| 1                              | 0                          | 1          | 1             | 1                     |

| 1                              | 1                          | 0          | 1             | 1                     |

| 1                              | 1                          | 1          | 1             | 1                     |

| Copyright 2003,                | Regents of University of C | alifornia  |               |                       |

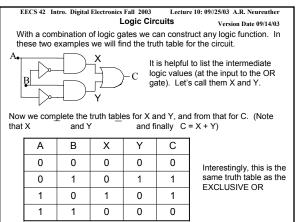

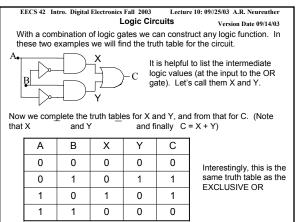

Evaluation of Logical Expressions with "Truth Tables"

The Truth Table completely describes a logic expression

In fact, we will use the Truth Table as the fundamental

Two logic expressions are equal if their truth tables are the

Lecture 10: 09//25/03 A.R. Neureuther

Version Date 09/14/03

EECS 42 Intro. Digital Electronics Fall 2003

meaning of a logic expression.

same

| EECS 42 Intro. Digital Electronics Fall 2003 Lecture 10: 09//25/03 A.R. Neureuth |

|----------------------------------------------------------------------------------|

| Version Date 09/14/                                                              |

| EECS 42 Introduction to Digital Electronics                                      |

| Andrew R. Neureuther                                                             |

| Lecture # 10 Prof. King: Basic Digital Blocks                                    |

| • 20 Min Quiz                                                                    |

| <b>Basic Circuit Analysis and Transients</b>                                     |

| Logic Functions, Truth Tables                                                    |

| Circuit Symbols, Logic from Circuit                                              |

| Schwarz and Oldham 11.1, 11.2 393-402                                            |

| Midterm 10/2: Lectures # 1-9: 4 Topics – See slide 2<br>Length/Credit Review TBA |

| http://inst.EECS.Berkeley.EDU/~ee42/                                             |

|                                                                                  |

| EECS 42 Intro. Digital Electronics Fall 2003                                                                      | Lecture 10: 09//25/03 A.R. Neureuther |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                                                                                                                   | Version Date 09/14/03                 |

| Logical Expre                                                                                                     | ssions                                |

|                                                                                                                   |                                       |

| Standard logic notation :                                                                                         |                                       |

| AND: "dot" Examples: X = A ·                                                                                      | $B ; Y = A \cdot B \cdot C$           |

| OR : "+ sign" Examples: W = A                                                                                     | +B ; Z = A+B+C                        |

| NOT: "bar over symbol for comple                                                                                  | ment" Example: $Z = \overline{A}$     |

| With these basic operations we can expression.                                                                    | construct any logical                 |

| Order of operation: NOT, AND, OR<br>expression is performed after the ex<br>there is an implied parenthesis, e.g. | pression is evaluated, so             |

# EECS 42 Intro. Digital Electronics Fall 2003 Lecture 10: 09//25/03 A.R. Neureuther Version Date 09/14/03 First Midterm Exam: Topics

- Basic Circuit Analysis (KVL, KCL)

- Equivalent Circuits and Graphical Solutions for Nonlinear Loads

- Transients in Single Capacitor Circuits

- Node Analysis Technique and Checking Solutions

Exam is in class 9:40-10:45 AM, Closed book, Closed notes, Bring a calculator, Paper provided

### EECS 42 Intro. Digital Electronics Fall 2003 Lecture 10: 09//25/03 A.R. Neureuther Version Date 09/14/03

## Logic Function Example

• Boolean Expression:  $H = (A \cdot B \cdot C) + T$

This can be read H=1 if (A and B and C are 1) or T is 1, or H is true if all of A,B,and C are true, or T is true, or The voltage at node H will be high if the input voltages at nodes A, B and C are high or the input voltage at node T is high

| EECS 42 Intro. Digital Electronics Fall 2003                                                                                                                                     | Lecture 10: 09//25/03 A.R. Neureuther |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

| Logic Func                                                                                                                                                                       | Version Date 09/14/03                 |  |  |  |

| Logic Expression : To create logic values we will define "True" , as<br>Boolean 1 and "False" , as Boolean 0.                                                                    |                                       |  |  |  |

| Moreover we can associate a logic variable with a circuit node. Typically we<br>associate logic 1 with a high voltage (e.g. 2V) and and logic 0 with a low<br>voltage (e.g. 0V). |                                       |  |  |  |

| Example: The logic variable H is true (H=1) if (A and B and C are 1) or T is true (logic 1), where all of A,B,C and T are also logical variables.                                |                                       |  |  |  |

| Logic Statement: H = 1 if A and                                                                                                                                                  | B and C are 1 or T is 1.              |  |  |  |

| We use "dot" to designate logical "and" and "+" to designate logical or in<br>switching algebra. So how can we express this as a Boolean<br>Expression?                          |                                       |  |  |  |

| Boolean Expression: $H = (A \cdot B \cdot G)$                                                                                                                                    | C) + ⊤                                |  |  |  |

| Note that there is an order of operation performed before OR. Thus the parentl                                                                                                   |                                       |  |  |  |

| Convright 2003. Reseases of University of California                                                                                                                             |                                       |  |  |  |

| EECS 42 Intro. Digital Electronics Fall 2003                                                   | Lecture 10: 09//25/03 A.R. Neureuther |  |  |  |  |

|------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

|                                                                                                | Version Date 09/14/03                 |  |  |  |  |

| Logic Function Example 2                                                                       |                                       |  |  |  |  |

| You wish to express under which conditions your burglar alarm goes off (B=1):                  |                                       |  |  |  |  |

| If the "Alarm Test" button is pressed (A=1)                                                    |                                       |  |  |  |  |

| OR if the Alarm is Set (S=1) AND { the door is opened (D=1) OR the trunk is opened (T=1)}      |                                       |  |  |  |  |

| Boolean Expression: B = A + S(D +                                                              | Τ)                                    |  |  |  |  |

| This can be read B=1 if A = 1 or S=1 AN                                                        | D (D OR T =1), i.e.                   |  |  |  |  |

| B=1 if {A = 1} or {S=1 AND (D OR T =1)}                                                        |                                       |  |  |  |  |

| or                                                                                             |                                       |  |  |  |  |

| B is true IF {A is true} OR {S is true AND D                                                   | OR T is true}                         |  |  |  |  |

| or                                                                                             |                                       |  |  |  |  |

| The voltage at node H will be high if {the in<br>{the input voltage at S is high and the volta |                                       |  |  |  |  |

| Copyright 2003, Regents of University of California                                            |                                       |  |  |  |  |

|                                                                                                |                                       |  |  |  |  |

| EECS 42 Intro. Digital Electronics Fal | I 2003 Lecture 10: 09//25/03 A.R. Neureuther                               |  |  |  |

|----------------------------------------|----------------------------------------------------------------------------|--|--|--|

|                                        | Version Date 09/14/03                                                      |  |  |  |

| Some Important Logical Functions       |                                                                            |  |  |  |

| • "AND"                                | $A \cdot B$ (or $A \cdot B \cdot C$ )                                      |  |  |  |

| ». "OR"                                | A+B (or $A+B+C+D$ )                                                        |  |  |  |

| • "INVERT" or "NOT"                    | not A (or $\overline{A}$ )                                                 |  |  |  |

| • "not AND" = NAND                     | $\overline{AB}$ (only 0 when A and B=1)                                    |  |  |  |

| • "not OR" = NOR                       | $\overline{A+B}$ (only 1 when $A=B=0$ )                                    |  |  |  |

| • exclusive OR = XOR                   | $A \oplus B$ (only 1 when A, B differ)<br>i.e., $A + B$ except $A \cdot B$ |  |  |  |

| Conversite 2003. Research of Unive     | arvity of California                                                       |  |  |  |

| EECS 42 Intro. Digital Electro | onics Fall 20              | 03 Lectu   | re 10: 09//25 | 03 A.R. Neureuther    |

|--------------------------------|----------------------------|------------|---------------|-----------------------|

|                                |                            |            |               | Version Date 09/14/03 |

| Evaluation of Log              | ical Expr                  | essions wi | ith "Truth    | n Tables"             |

| Truth Table for                | or Logic E                 | xpression  | H = (A ·      | B · C) + T            |

| А                              | В                          | С          | Т             | Н                     |

| 0                              | 0                          | 0          | 0             | 0                     |

| 0                              | 0                          | 1          | 0             | 0                     |

| 0                              | 1                          | 0          | 0             | 0                     |

| 0                              | 1                          | 1          | 0             | 0                     |

| 1                              | 0                          | 0          | 0             | 0                     |

| 1                              | 0                          | 1          | 0             | 0                     |

| 1                              | 1                          | 0          | 0             | 0                     |

| 1                              | 1                          | 1          | 0             | 1                     |

| 0                              | 0                          | 0          | 1             | 1                     |

| 0                              | 0                          | 1          | 1             | i i                   |

| 0                              | 1                          | 0          | 1             | 1                     |

| 0                              | 1                          | 1          | 1             | 1                     |

| 1                              | 0                          | 0          | 1             | 1                     |

| 1                              | 0                          | 1          | 1             | 1                     |

| 1                              | 1                          | 0          | 1             | 1                     |

| 1                              | 1                          | 1          | 1             | 1                     |

| Copyright 2003,                | Regents of University of C | alifornia  |               |                       |

Evaluation of Logical Expressions with "Truth Tables"

The Truth Table completely describes a logic expression

In fact, we will use the Truth Table as the fundamental

Two logic expressions are equal if their truth tables are the

Lecture 10: 09//25/03 A.R. Neureuther

Version Date 09/14/03

EECS 42 Intro. Digital Electronics Fall 2003

meaning of a logic expression.

same