EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 16: 10/21/03 A.R. Neureuther

Version Date 10/18/03

# EECS 42 Introduction to Digital Electronics Andrew R. Neureuther

These viewgraphs will be handed out in class 10/21/03

#### Lecture # 16 Logic with a State Dependent Device

S&O pp. 593-595, 604-606 (read for graphs and not physics or equations), plus Handout of these viewgraphs.

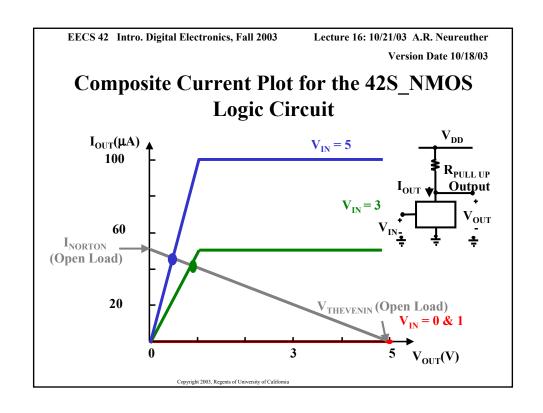

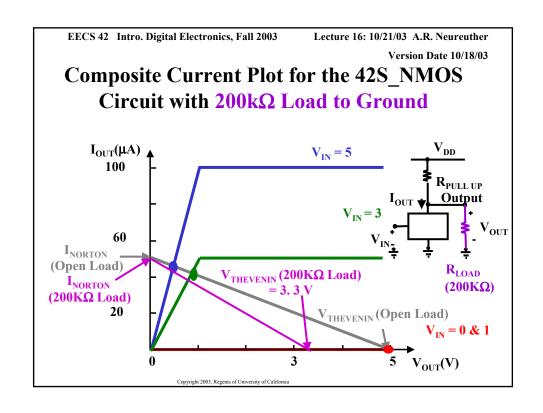

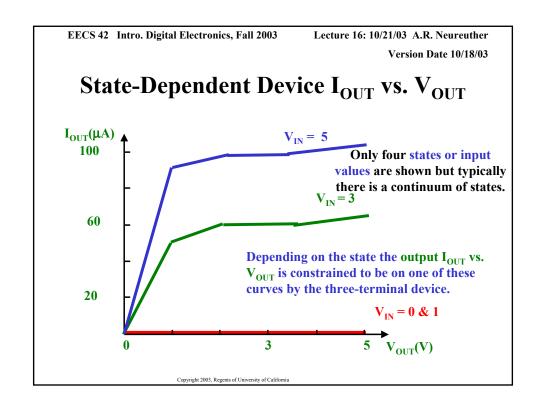

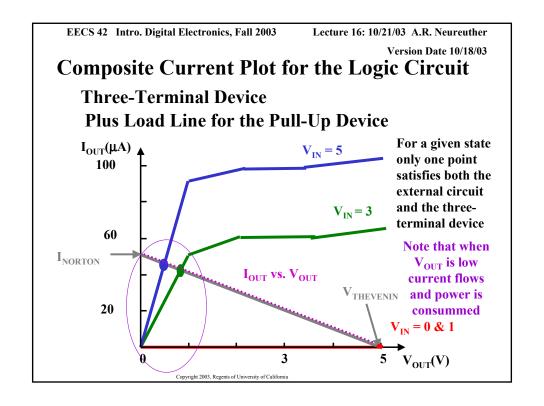

- A) State Dependent Device  $I_{OUT}$  vs.  $V_{OUT}$

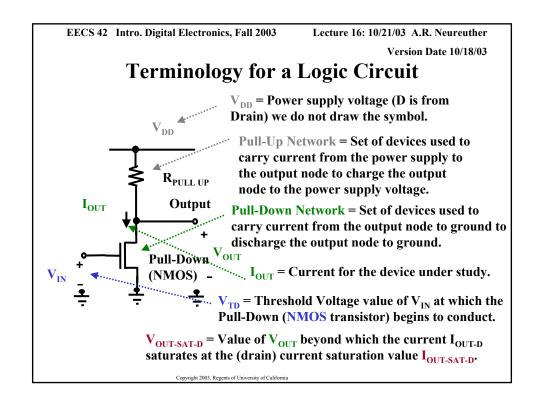

- B) Load Line Analysis for Logic Levels

- C) Voltage Transfer Characteristics  $VTC = plot of V_{OUT} vs. V_{IN}$

- D) 42S\_NMOS Pull-Down Device and Logic http://inst.EECS.Berkeley.EDU/~ee42/

Copyright 2003, Regents of University of California

Lecture 16: 10/21/03 A.R. Neureuther

Version Date 10/18/03

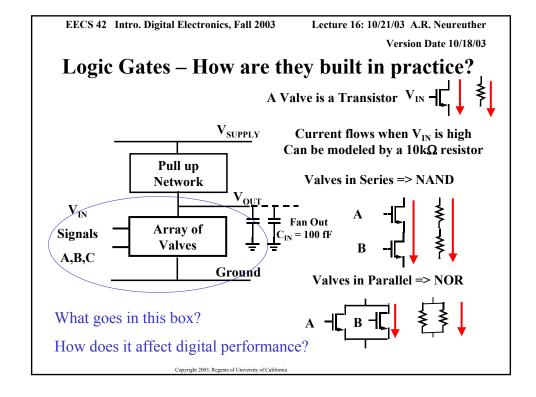

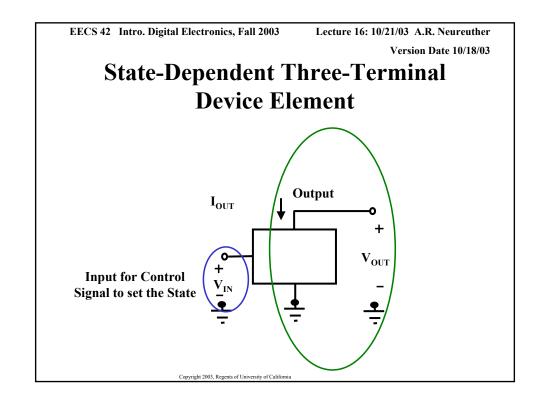

## Digital Logic from State-Dependent Three-Terminal Devices

Three-terminal devices such as MOS transistors have output characteristics (such as  $I_{OUT}$  vs.  $V_{OUT}$  curves) on the output side that can be programmed by changing signals on the input side (such as the input voltage).

The input voltage  $V_{\rm IN}$  can thus be viewed as changing or programming the 'State' of the output of the device.

Three-terminal devices whose input voltage  $V_{\rm IN}$  or 'State' can be programmed can be used to make digital logic devices for computers whose outputs respond to input signals.

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 16: 10/21/03 A.R. Neureuther

Version Date 10/18/03

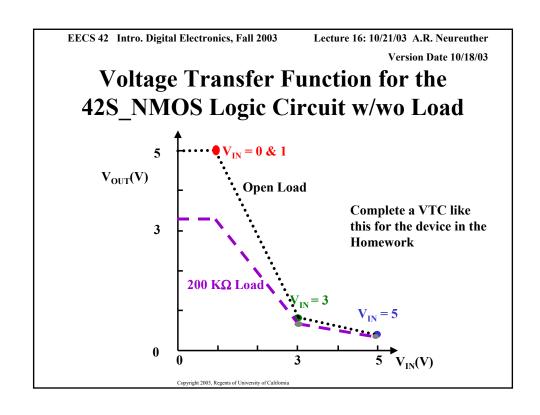

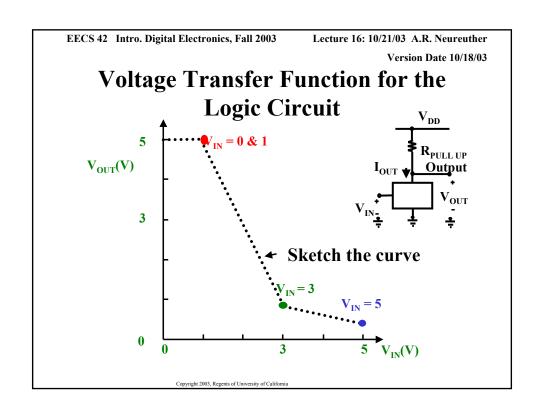

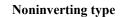

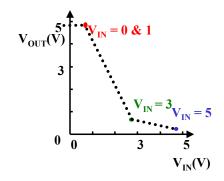

## **Voltage Transfer Function: V<sub>OUT</sub> vs. V<sub>IN</sub>**

The  $V_{OUT}$  vs.  $V_{IN}$  characteristic is another view of the logic gate that is used to determine the inverting and noninverting nature of a gate.

**Inverting type**

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 16: 10/21/03 A.R. Neureuther

Version Date 10/18/03

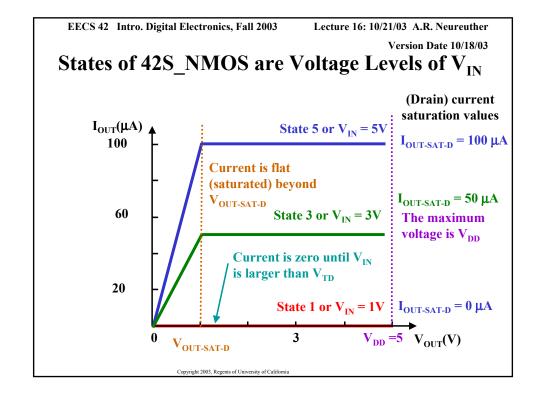

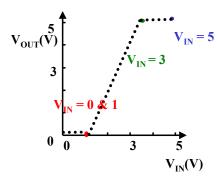

### **Saturation Current 42S NMOS Model**

Current  $I_{OUT}$  only flows when  $V_{IN}$  is larger than the threshold value  $V_{TD}$  and the current is proportional to  $V_{OUT}$  up to  $V_{OUT\text{-}SAT\text{-}D}$  where it reaches the saturation current

$$I_{OUT-SAT-D} = k_D \big( V_{IN} - V_{TD} \big) V_{OUT-SAT-D}$$

Note that we have added an extra parameter to distinguish between threshold ( $V_{TD}$ ) and saturation ( $V_{OUT\text{-}SAT\text{-}D}$ ).

**Example:**

$k_D = 25 \mu A/V^2$   $V_{TD} = 1V$

$V_{OUT-SAT-D} = 1V$

Use these values in the homework.

$I_{OUT-SAT-PD} = 25 \frac{\mu A}{V^2} (3V - 1V) 1V = 50 \mu A$  20

100 State 3  $V_{IN} = 3V$ 60 Saturation (with  $V_{OUT}$ )

Linear (with  $V_{OUT}$ )  $V_{OUT-SAT-D}$   $V_{OUT}$

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003 Lecture 16: 10/21/03 A.R. Neureuther Version Date 10/18/03 Drawing I<sub>OUT</sub> as function of V<sub>IN</sub> and V<sub>OUT</sub> for the 42S NMOS Pull-Down Device The equations are expressly designed for EE42 to make it very simple to draw  $I_{OUT}$  vs.  $V_{OUT}$ 100 **↑**I<sub>OUT</sub>(µA) 1) For  $V_{IN} < V_{TD}$ , the current is zero. State 3  $V_{IN} = 3V$ 2) For  $V_{IN} > V_{TD}$ , first evaluate the Saturation (with V<sub>OUT</sub>) 60 current  $I_{OUT}$  at  $V_{OUT} = V_{OUT-SAT-D}$ and plot the single point  $(I_{OUT}, V_{OUT})$ Linear (with  $V_{OUT}$ ) 2 3) Draw a line from this point to the 0 origin to create the linear region. 4) Draw a horizontal line from this point to create the saturation region Copyright 2003, Regents of University of California