EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 17: 10/23/03 A.R. Neureuther

Version Date 10/18/03

# EECS 42 Introduction Digital Electronics Andrew R. Neureuther

These viewgraphs will be handed out in class.

Lecture # 17 Logic with Complementary Devices S&O pp. 607-611 (read for graphs and not physics or equations), plus Handout of Wed Lectures.

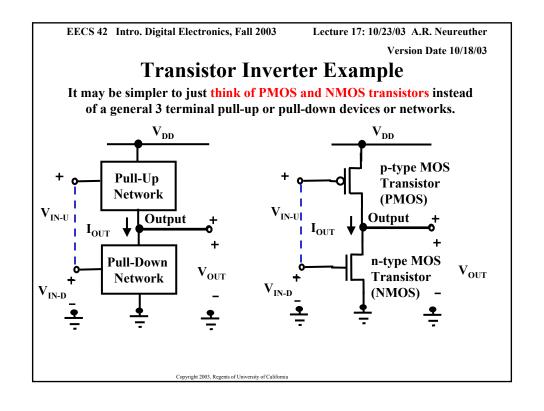

- A) Discovering a Pull-Up Device

- B) Designing a Pull-Up Device

- C) EE 42 Pull-Up Device Model (42S\_PMOS)

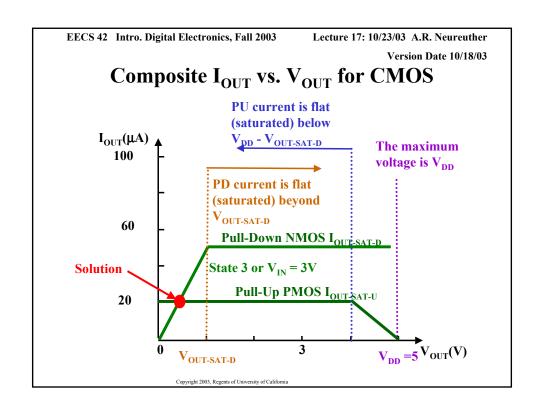

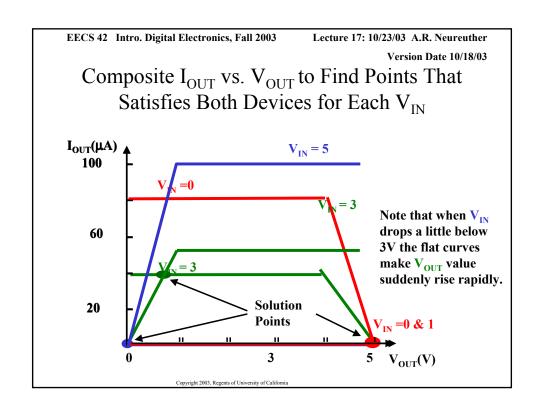

- D) Composite I<sub>OUT</sub> vs. V<sub>OUT</sub>

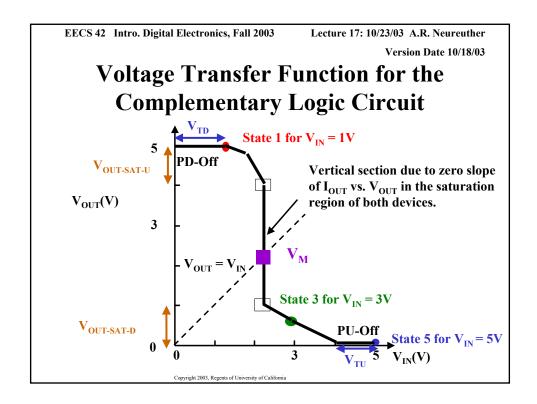

- E) Voltage Transfer Function and  $V_{MID}$  http://inst.EECS.Berkeley.EDU/~ee42/

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 17: 10/23/03 A.R. Neureuther

Version Date 10/18/03

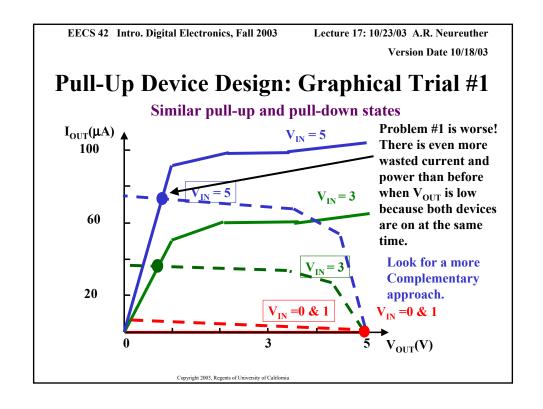

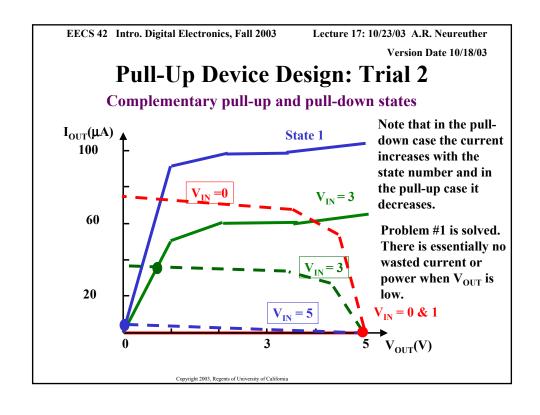

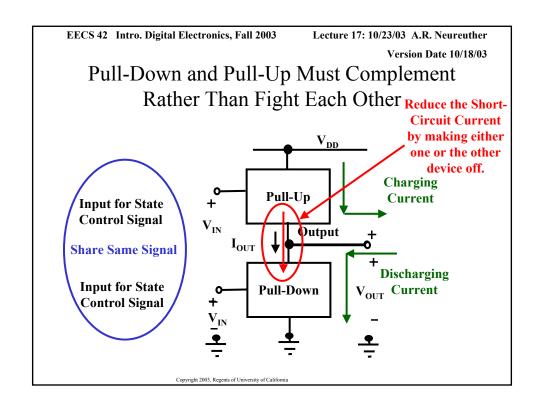

## Problems and Opportunities in Logic Circuit Design

Problem #1: Significant wasted current and

power when V<sub>OUT</sub> is low.

Problem #2: High value of  $V_{OUT}$  is adversely

affected by a load resistor.

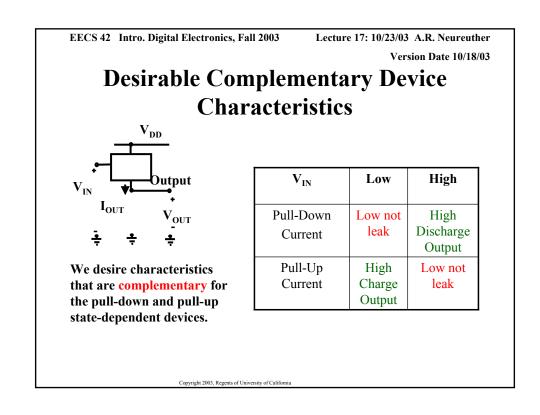

Missed Opportunity: The value of the input control signal is not used to adjust the state of the pull-up device.

What if: If the pull-up device could be a state-dependent device what kind of device would we want?

Copyright 2003, Regents of University of California

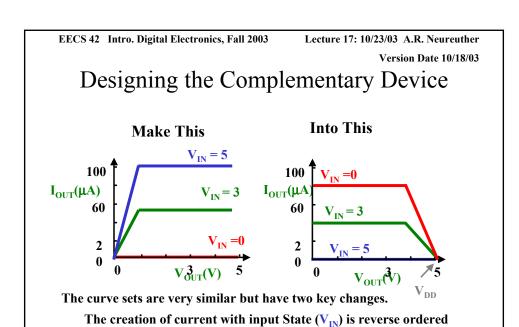

The dependence on  $V_{OUT}$  is reversed in sign and shifted by  $V_{DD}$

Copyright 2003, Regents of University of California

(and also shifted).

Pull-Up Can be viewed as Complementary by using Device rather than Circuit voltages V<sub>DD</sub>-V<sub>X</sub>

V'<sub>IN</sub>=V<sub>DD</sub>-V<sub>IN</sub>

V'<sub>IN</sub>=V<sub>DD</sub>-V<sub>IN</sub>

V'<sub>IN</sub>=V<sub>DD</sub>-V<sub>IN</sub>

Pull-Up

V'<sub>OUT</sub>=V<sub>DD</sub>-V<sub>OUT</sub>

V'<sub>IN</sub>=V<sub>DD</sub>-V<sub>IN</sub>

V'<sub>IN</sub>=V<sub>DD</sub>-V<sub>IN</sub>

Copyright 2003. Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 17: 10/23/03 A.R. Neureuther

Version Date 10/18/03

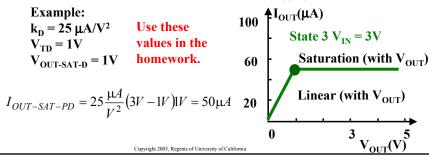

#### **Saturation Current NMOS Model**

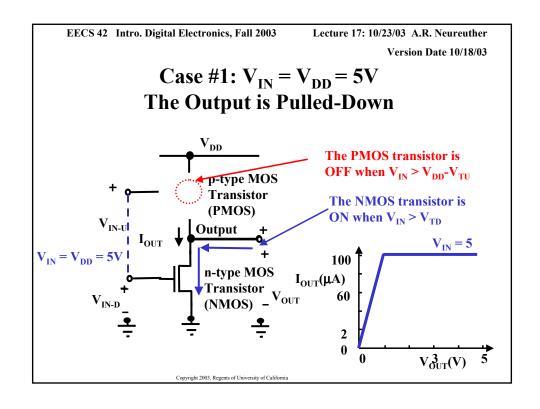

Current  $I_{OUT}$  only flows when  $V_{IN}$  is larger than the threshold value  $V_{TD}$  and the current is proportional to  $V_{OUT}$  up to  $V_{OUT\text{-}SAT\text{-}D}$  where it reaches the saturation current

$$I_{OUT-SAT-D} = k_D (V_{IN} - V_{TD}) V_{OUT-SAT-D}$$

Note that we have added an extra parameter to distinguish between threshold ( $V_{TD}$ ) and saturation ( $V_{OUT\text{-}SAT\text{-}D}$ ).

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 17: 10/23/03 A.R. Neureuther

Version Date 10/18/03

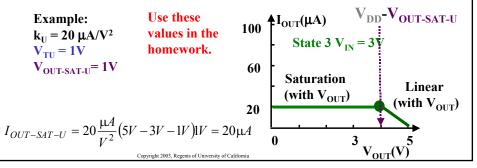

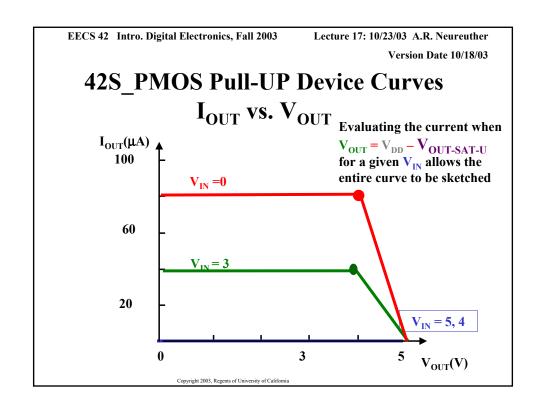

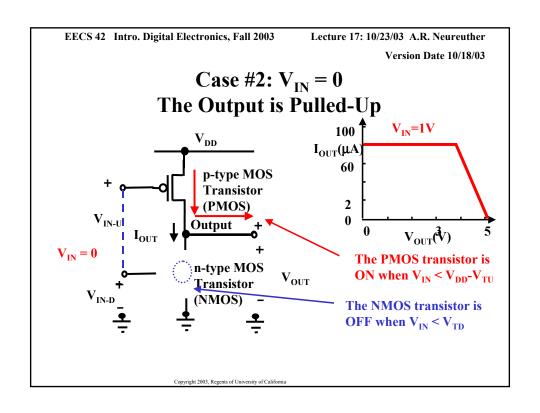

### **Saturation Current 42S PMOS Model**

Current  $I_{OUT}$  only flows when  $V_{IN}$  is smaller than  $V_{DD}$  by the threshold value  $V_{TU}$  (that is  $V_{DD}$ - $V_{IN}$  >  $V_{TU}$ ) and the current is proportional to the excess gate voltage  $(V_{DD}$ - $V_{IN}$  -  $V_{TU}$ ) and is also proportional to  $(V_{DD}$ - $V_{OUT}$ ) above  $(V_{DD}$ - $V_{OUT}$ -SAT-U) where it has its maximum saturated value.

$$I_{OUT-SAT-U} = k_U (V_{DD} - V_{IN} - V_{TU}) V_{OUT-SAT-U}$$

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 17: 10/23/03 A.R. Neureuther

Version Date 10/18/03

## Method for Finding $\boldsymbol{V}_{\boldsymbol{M}}$

At V<sub>M</sub>,

1)

$$V_{OUT} = V_{IN} = V_{M}$$

2) Both devices are in saturation

$$\mathbf{3)} \quad \mathbf{I}_{\mathbf{OUT\text{-}SAT\text{-}D}} = \mathbf{I}_{\mathbf{OUT\text{-}SAT\text{-}U}}$$

$$I_{OUT-SAT-D} = k_D (V_{IN} - V_{TD}) V_{OUT-SAT-D}$$

$$= I_{OUT-SAT-U} = k_U (V_{DQ} - (V_{IN}) - V_{TU}) V_{OUT-SAT-U}$$

Substitute  $V_M$

Solve for  $V_{\boldsymbol{M}}$

Example Result: When  $k_D=k_P$  ,  $V_{OUT\text{-}SAT\text{-}D}=V_{OUT\text{-}SAT\text{-}U}$  and  $V_{TD}=V_{TU}$  , then  $V_M=V_{DD}/2$

Copyright 2003, Regents of University of Californi