EECS 42 Intro. Digital Electronics Fall 2003 Lect

Lecture 18: 10/28/03 A.R. Neureuther

Version Date 10/28/03

## EECS 42 Introduction Digital Electronics Andrew R. Neureuther

Quiz 10/30 and Midterm 10/6

**Lecture # 18 Logic Transients (Handout)**

- A) Review: Quiz 10/30 and Midterm 11/6

- B) Transient as Capacitor Charging

- C) Equivalent Resistance for MOS

- D) Inverter Propagation Delay

- E) Complementary MOS Operation

http://inst.EECS.Berkeley.EDU/~ee42/

EECS 42 Intro. Digital Electronics Fall 2003

Lecture 18: 10/28/03 A.R. Neureuther

Version Date 10/28/03

## Midterm #2 Coverage

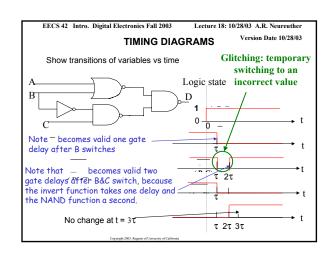

- Logic Functions and Timing Diagrams Quiz 10/30

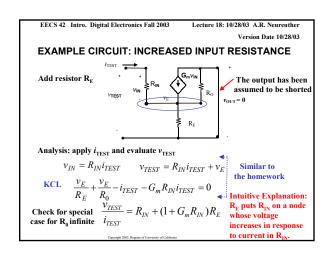

- Analysis of vanilla circuits with dependent sources

- · Ideal Op-Amps

- Analysis of circuits using dependent sources to improve characteristics

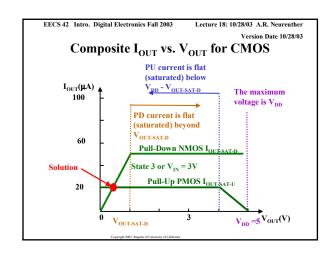

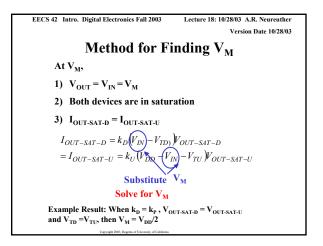

- · Static analysis of logic gates

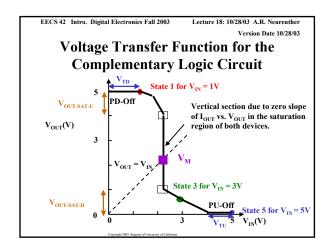

|      | V <sub>T</sub> (V) | V <sub>OUT-SAT</sub> (V) | k'(µA/V²) |

|------|--------------------|--------------------------|-----------|

| NMOS | 0.43               | 0.63                     | 100       |

| PMOS | 0.4                | 1                        | 25        |

$I_{OUT-SAT-n} = k_n \left(\frac{W}{L}\right)_n \left(V_{IN} - V_{Tn}\right) V_{OUT-SAT-n}$

linimum sized devices have W/L = 2

$I_{OUT-SAT-p} = k_p^{'} \left(\frac{W}{L}\right)_p^{'} \left(V_{DD} - V_{IN} - \mid V_{Tp}\mid\right) V_{OUT-SAT-p}$

Consticht 2003. Reports of University of California

EECS 42 Intro. Digital Electronics Fall 2003

Lecture 18: 10/28/03 A.R. Neureuther

Version Date 10/28/03

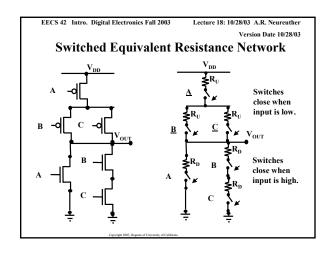

## **Switched Equivalent Resistance Model**

The above model assumes the device is an ideal constant current source.

- 1) This is not true below  $\boldsymbol{V}_{\text{OUT-SAT-D}}$  and leads to in accuracies.

- 2) Combining ideal current sources in networks with series and parallel connections is problematic.

Instead define an equivalent resistance for the device by setting  $0.69R_{\rm D}{\rm C}$ equal to the  $\Delta t$  found above

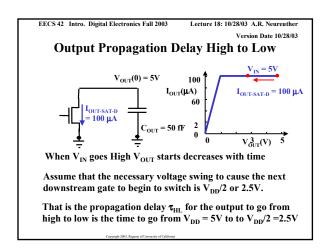

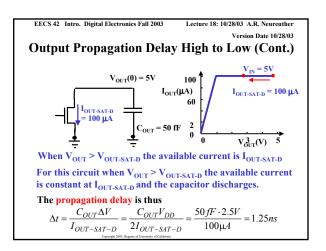

$$\Delta t = \frac{C_{OUT}V_{DD}}{2I_{OUT-SAT-D}} = 0.69R_DC_{OUT}$$

$$R_D = \frac{V_{DD}}{2 \cdot \left(0.69\right) I_{OUT-SAT-D}} \approx \frac{3}{4} \frac{V_{DD}}{I_{OUT-SAT-D}} = \frac{3}{4} \frac{5V}{100 \mu A} = 37.5 k\Omega$$

Each device can now be replaced by this equivalent resistor.

EECS 42 Intro. Digital Electronics Fall 2003 Lecture 18: 10/28/03 A.R. Neureuther  $R_D = \frac{3}{4} V_{DD} / I_{SAT}$  has a Physical Interpretation

$^{3}\!\!/_{4}\,V_{DD}$  is the average value of  $\,V_{OUT}$

Approximate the NMOS device curve by a straight line from (0,0) to ( $I_{OUT\text{-SAT-D}}$ ,  $^3\!\!/_4\,V_{DD}$  ).

Interpret the straight line as a resistor with

slope =

$$1/R = \frac{3}{4} V_{DD}/I_{SAT}$$

EECS 42 Intro. Digital Electronics Fall 2003

Version Date 10/28/03

## **Switched Equivalent Resistance Values**

The resistor values depend on the properties of silicon, geometrical layout, design style and technology node.

n-type silicon has a carrier mobility that is 2 to 3 times higher than p-type.

The resistance is inversely proportion to the gate width/length in the geometrical layout.

Design styles may restrict all NMOS and PMOS to be of a predetermined fixed size.

The current per unit width of the gate increases nearly inversely with the linewidth.

> For convenience in EE 42 we assume  $R_D \equiv R_U \equiv 10~\text{k}\Omega$  for  $V_{DD} \equiv 5V$  and  $R_D = R_U = 10 \text{ k}\Omega \text{ for } V_{DD} = 5V$

EECS 42 Intro. Digital Electronics Fall 2003 Version Date 10/28/03 **Inverter Propagation Delay** Discharge (pull-down)  $\Delta t = 0.69 R_D C_{OUT} = 0.69 (10 k\Omega) (50 fF) = 345 ps$ Discharge (pull-up)  $\Delta t = 0.69 R_U C_{OUT} = 0.69 (10 k\Omega) (50 fF) = 345 ps$

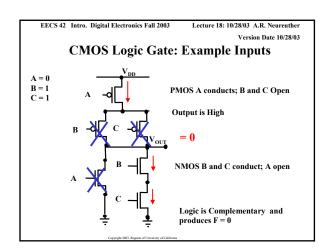

EECS 42 Intro. Digital Electronics Fall 2003 Lecture 18: 10/28/03 A.R. Neureuther Version Date 10/28/03 NMOS and **CMOS Logic Gate** PMOS use the same set of PMOS only in pull-up input signals PMOS conduct when input is low PMOS do not conduct when A +(BC) NMOS only in pull-down NMOS conduct when input is high. NMOS conduct for A + (BC) Logic is Complementary and produces  $F = \overline{A + (BC)}$

EECS 42 Intro. Digital Electronics Fall 2003 Lecture 18: 10/28/03 A.R. Neureuther **CMOS Logic Gate: Example Inputs** A = 0B = 0C = 0PMOS all conduct **Output** is High NMOS do not conduct Logic is Complementary and produces F = 1