Lecture 21: 11/13/03 A.R. Neureuther

Version Date 11/12/03

# EECS 42 Introduction Digital Electronics Andrew R. Neureuther

#### **Lecture # 21 Clock Operation of Latches**

Handout of This Lecture.

- A) 2<sup>nd</sup> Midterm Returned

- **B) CMOS Propagation Delays**

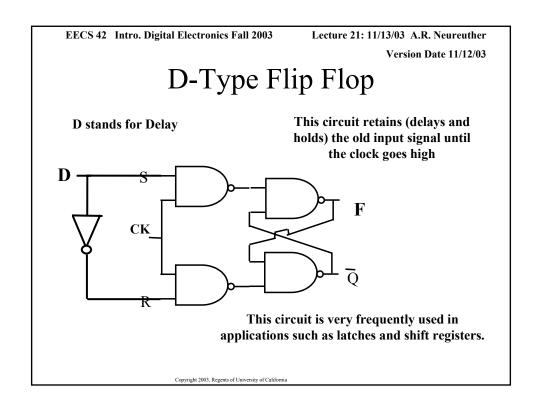

- C) Latch circuit to hold/release signals

- D) Cascade CMOS elements with latches

http://inst.EECS.Berkeley.EDU/~ee42/

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics Fall 2003

Lecture 21: 11/13/03 A.R. Neureuther

Version Date 11/12/03

#### Results Midterm #2

|           | P1   | P2   | Р3   | P4   | Tot  |

|-----------|------|------|------|------|------|

|           | 25   | 25   | 28   | 22   | 100  |

| Ave       | 22.4 | 15   | 18.8 | 14.3 | 70.4 |

| Ave/Max   | 0.90 | 0.60 | 0.67 | 0.65 | 0.70 |

| StDev     | 4.9  | 8.6  | 7.7  | 6.3  | 20.1 |

| StDev/Max | 0.20 | 0.35 | 0.28 | 0.29 | 0.20 |

High 100 (2), Low 12, Median 74

Approximate Scale:

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics Fall 2003

Lecture 21: 11/13/03 A.R. Neureuther

Version Date 11/12/03

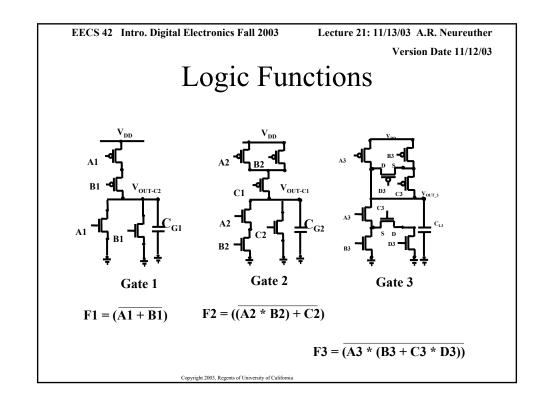

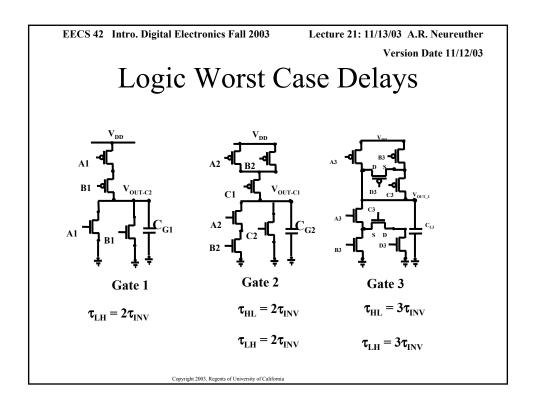

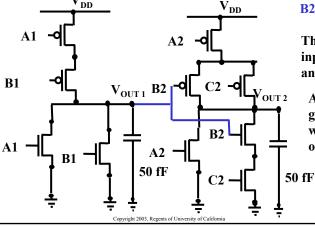

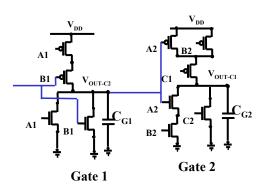

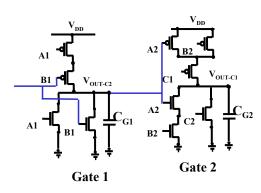

# Logic Gate Cascade

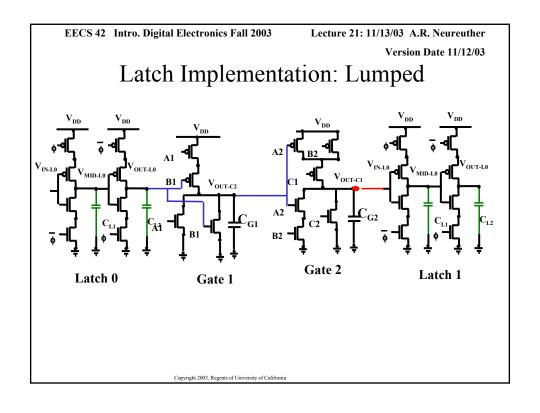

To avoid large resistance due to many gates in series, logic functions with 4 or more inputs are usually made from cascading two or more 2-4 input blocks.

$B2 = V_{OUT 1}$

The four independent input are A1, B1, A2 and C2.

A2 high discharges gate 2 without even waiting for the output of gate 1.

C2 high and A2 low makes gate 2 wait for Gate 1 output

Lecture 21: 11/13/03 A.R. Neureuther

Version Date 11/12/03

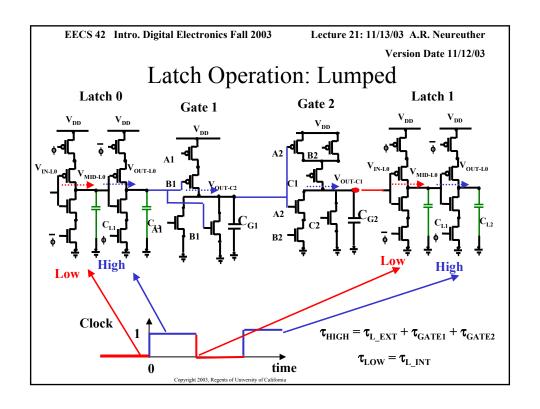

## Propagation Delays Add in Cascade

$$\tau_{PD\_CASCADE} = \tau_{PD\_1} + \tau_{PD\_2}$$

Copyright 2003, Regents of University of California

**EECS 42** Intro. Digital Electronics Fall 2003

Lecture 21: 11/13/03 A.R. Neureuther

Version Date 11/12/03

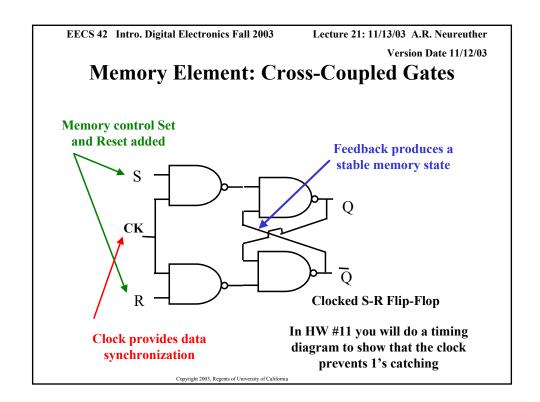

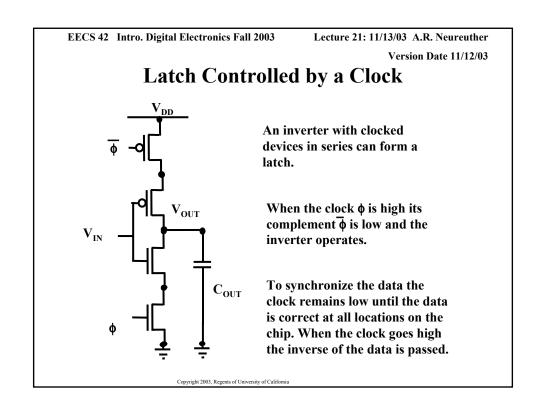

## Data Synchronization problem

- Combinatorial logic gates can give incorrect answers prematurely and may take several gate propagation delays produce an answer.

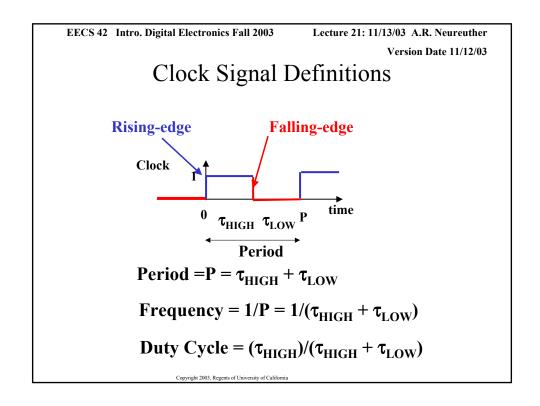

- Clocks (signals as to when to proceed) and latches (which capture and hold the correct outputs) can provide synchronization.

Copyright 2003, Regents of University of California

Lecture 21: 11/13/03 A.R. Neureuther

Version Date 11/12/03

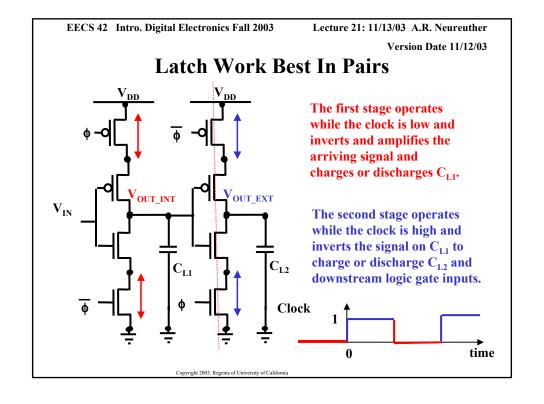

#### A Double Latch is an Edge-Triggered D Type Flip-Flop

During the low part of the clock cycle this circuit records the input value and when the clock goes high drives  $V_{OUT\,2}$  to the voltage level that arrived. (This is the classic function of a D flip-flop.)

Note that this circuit is not fooled by noise on the input and makes its decision on the rising edge of the clock (edge-triggered).

EECS 42 Intro. Digital Electronics Fall 2003

Lecture 21: 11/13/03 A.R. Neureuther

Version Date 11/12/03

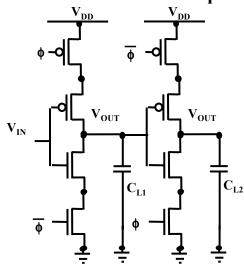

## Example of Circuits to Integrate with Latches

$$\tau_{PD\_CASCADE} = \tau_{PD\_1} + \tau_{PD\_2}$$

Copyright 2003, Regents of University of California