Lecture 24: 11/25/03 A.R. Neureuther

Version Date 11/18/03

### **EECS 42 Introduction Digital Electronics**

# Lecture # 24 Current Flow in Silicon and N-MOS Devices

Physics of current flow, resistance, resistivity

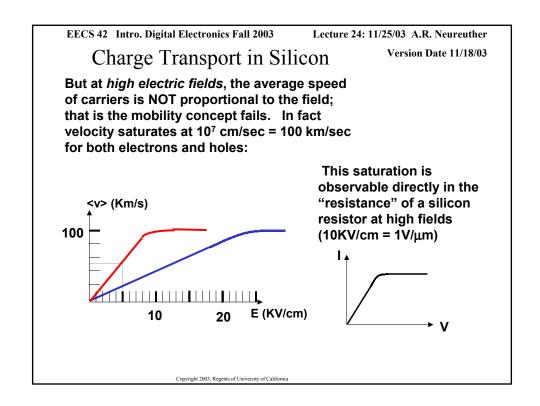

- A) Charge transport in a sheet and velocity saturation

- B) N-MOS Device Structure and Voltage Control

- C) N-MOS I vs. V at low and high drain voltage Reading: Schwarz and Oldham, pp. 518-526

http://inst.EECS.Berkeley.EDU/~ee42/

Copyright 2003, Regents of University of California

**EECS 42** Intro. Digital Electronics Fall 2003

Lecture 24: 11/25/03 A.R. Neureuther

Version Date 11/18/03

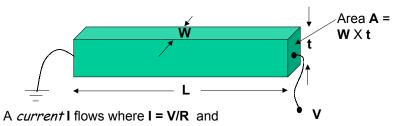

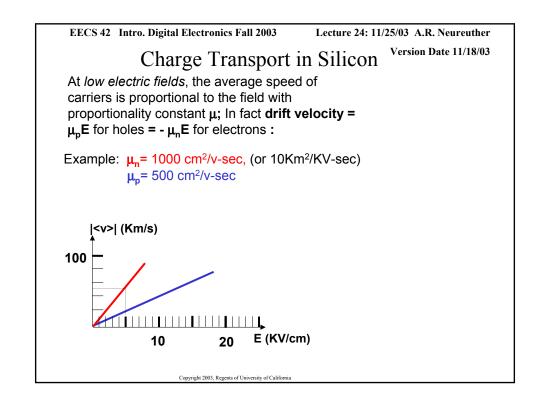

Physics of Current Flow, Resistance, Resistivity A *voltage* **V** applied across the *length* **L** of a homogeneous material produces an *electric field* **E** where **E** = **V/L**.

The *resistance* **R** is given by the resistor formula **R** =  $\rho$ **L/A** in which the resistivity,  $\rho$ , is *inversely* proportional to the *concentration of free carriers*, **N**, and the *mobility* of those carriers,  $\mu$ . ( $\mu$  is often defined by: |drift velocity| =  $\mu$ **E** =  $\mu$ **V/L**)

In fact  $\rho$  = 1/  $\sigma$  , where the *conductivity* ,  $\sigma$  , is defined by  $q~\mu~N$ , in which q is the *electronic charge* (q = 1.6 x 10<sup>-19</sup> Coulomb).

Lecture 24: 11/25/03 A.R. Neureuther

/18/03

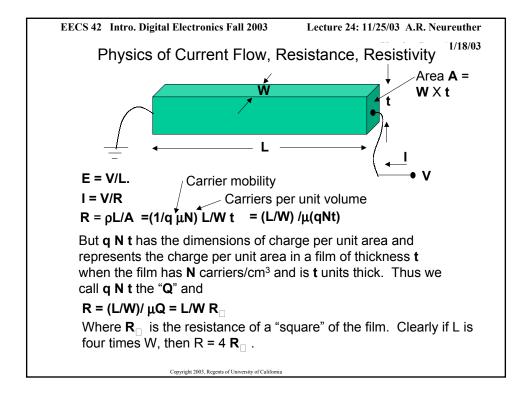

### Resistance of Silicon Films (at low E fields)

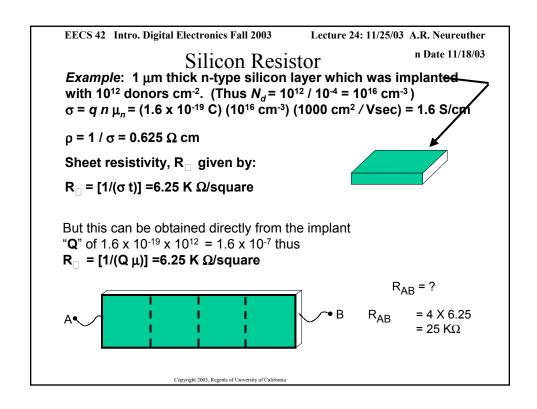

at low fields  $\sigma = q N \mu$  where N = n or p and  $\mu = \mu_n$  or  $\mu_p$

So  $\sigma = q n \mu_n$  for electrons in n-type Si and  $\sigma = q p \mu_p$  for holes in p-type Si

In other words  $R_{\square}$  =1/  $\mu_N(qN_Dt)$  = 1/  $\mu_N(Q_D)$  in N-type Silicon

Where  $(N_D t)$  is the number of donors implanted per unit area, and multiplying by q, we have the donor charge implanted per unit area.  $(\mu_N)$  is the mobility of the electrons).

Similarly  $R_{\Box}$  =1/  $\mu_{P}(qN_{A}t)$  = 1/  $\mu_{P}(Q_{A})$  in P-type Silicon

Where  $(N_A t)$  is the number of acceptors implanted per unit area, and multiplying by  $\mathbf{q}$ , we have the acceptor charge implanted per unit area.

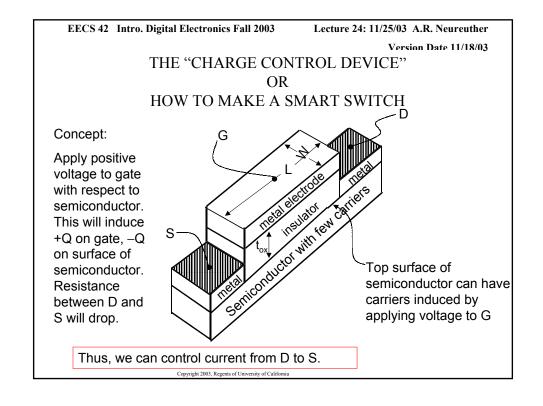

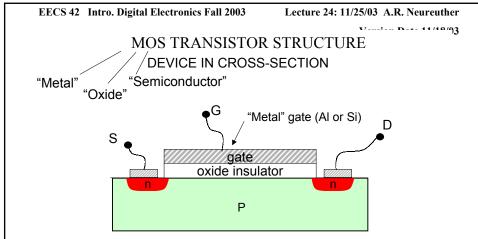

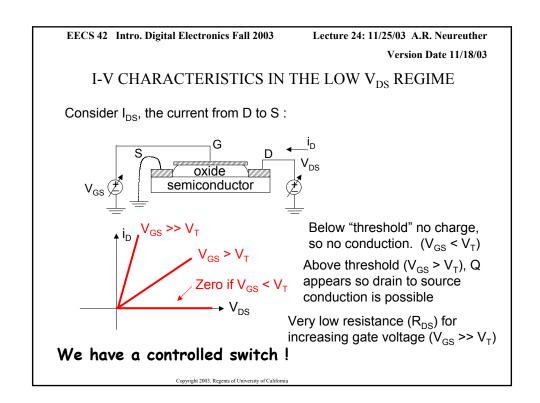

- In the absence of gate voltage, no current can flow between S and D.

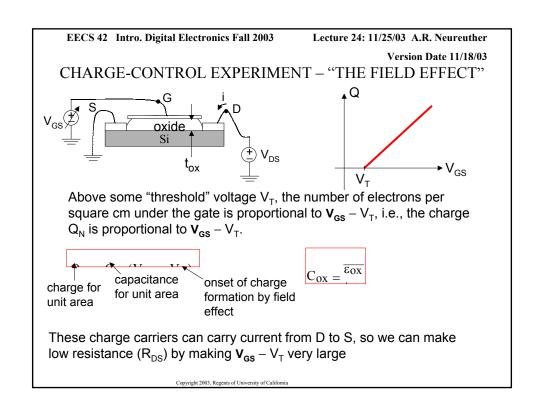

- Above a certain gate to source voltage V<sub>t</sub> (the "threshold"), electrons are induced at the surface beneath the oxide. (Think of it as a capacitor.)

- These electrons can carry current between S and D if a voltage is applied.

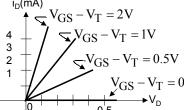

# Lecture 24: 11/25/03 A.R. Neureuther Version Date 11/18/03 I-V CHARACTERISTICS IN THE LOW V<sub>DS</sub> REGIME Consider first gate current and drain current versus GATE voltage Oxide semiconductor The gate is insulated, so there can never be any gate current. Always zero! Copyright 2003, Regents of University of California

Lecture 24: 11/25/03 A.R. Neureuther

Version Date 11/18/03

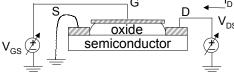

### I-V CHARACTERISTICS IN LOW V<sub>DS</sub> REGIME (cont.)

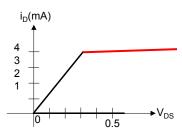

The drain current is a linear function of drain voltage at low drain voltages

MOS is just a (linear) controlled resistor in the low  $V_{DS}$  regime with the drain-to-source resistance depending on how much voltage is applied to the gate (compared to threshold).

Example of a device characteristic for low V<sub>DS</sub>

CLEARLY A "CONTROLLED SWITCH"

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics Fall 2003

Lecture 24: 11/25/03 A.R. Neureuther

### **N-MOS I-V Characteristics**

Version Date 11/18/03

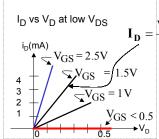

At low V<sub>DS</sub> we have:

$I_D = \frac{W}{L} \frac{V_{DS}}{R_{\square}} = \frac{W}{L} \mu_n C_{ox} (V_{GS} - V_T) \cdot V_{DS}$

[ Note that this also follows from our previous analysis where we had :

I = q W t  $\mu_n$  n V/L =  $Q_n \mu_n$  W/L V because Q=  $C_{OX}$  ( $V_{GS} - V_T$ )

And of course already know what happens to the I-V characteristics of short-channel MOS devices at higher values of  $V_{DS}$ : We know that the curves "bend over" because of velocity saturation.

Lecture 24: 11/25/03 A.R. Neureuther

Version Date 11/18/03

## What about Larger Drain-Source Voltages -- What Happens?

In digital circuits we always use the "shortest" gate length devices possible for reasons of speed. Fortunately this makes the answer to the question above very simple:

For such short-channel devices the drain current saturates because the carriers can only move at a limited speed

We can approximate the I-V characteristics as two straight lines:

- a) the linear "resistance" region at low V<sub>DS</sub> and

- b) the velocity saturation region (almost horizontal) at larger V<sub>DS</sub>.

Copyright 2003, Regents of University of California

**EECS 42** Intro. Digital Electronics Fall 2003

Lecture 24: 11/25/03 A.R. Neureuther

Version Date 11/18/03

### **Saturation Current NMOS Model**

Current  $I_{OUT}$  only flows when  $V_{IN}$  is larger than the threshold value  $V_{TD}$  and the current is proportional to  $V_{OUT}$  up to  $V_{OUT\text{-}SAT\text{-}D}$  where it reaches the saturation current

$$I_{OUT-SAT-D} = k_D \big( V_{IN} - V_{TD} \big) V_{OUT-SAT-D}$$

Note that we have added an extra parameter to distinguish between threshold ( $V_{TD}$ ) and saturation ( $V_{OUT\text{-}SAT\text{-}D}$ ).

**Example:**

$$\begin{split} k_D &= 25 \; \mu A/V^2 & Use \; these \\ V_{TD} &= 1V & values \; in \; the \\ V_{OUT\text{-}SAT\text{-}D} &= 1V & homework. \end{split}$$

$I_{OUT-SAT-PD} = 25 \frac{\mu A}{V^2} (3V - 1V) 1V = 50 \mu A$  20

100  $I_{OUT}(\mu A)$ State 3  $V_{IN} = 3V$ 60 Saturation (with  $V_{OUT}$ )

Linear (with  $V_{OUT}$ )

0 3  $V_{IN} = 3V_{OUT}$