Lecture 26: 12/04/03 A.R. Neureuther

Version Date 11/30/03

### **Review for the Final Exam**

**Likely 7 Problems**

\* Possible Bonus = 2/3 best +1/3 worst

Midterm Bonus = 2/3 best +1/3 worst

Transients\*

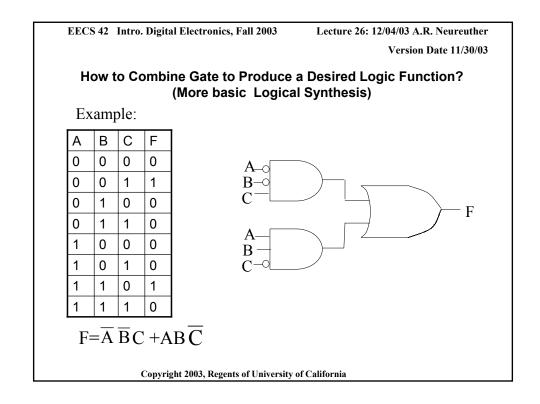

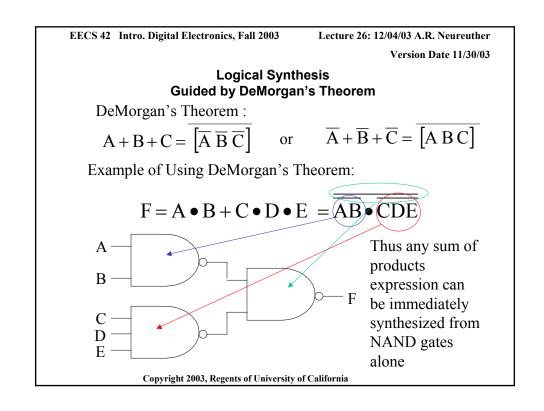

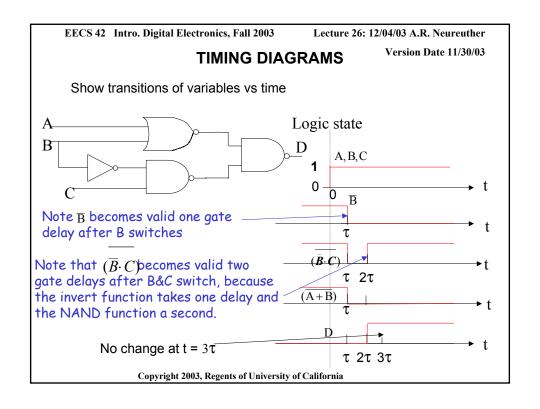

**Logic Functions and Timing Diagrams**

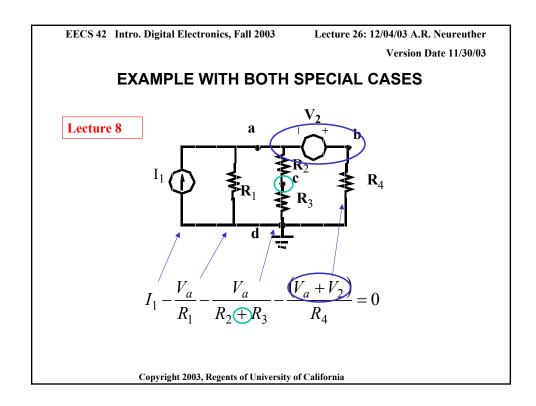

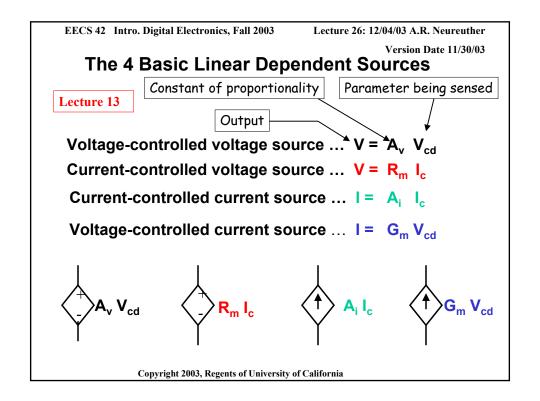

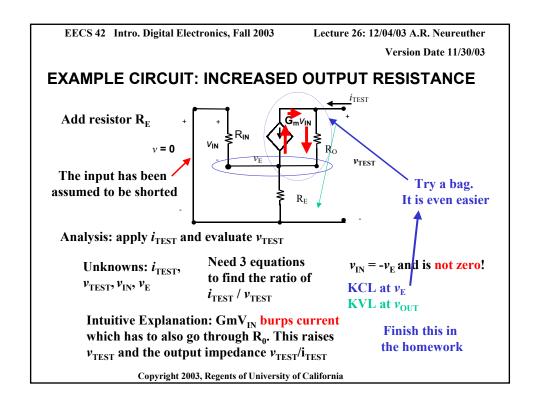

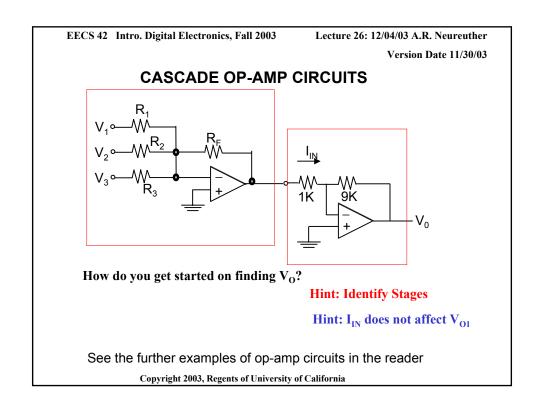

**Circuit Analysis with dependent Sources**

Op-Amps\*

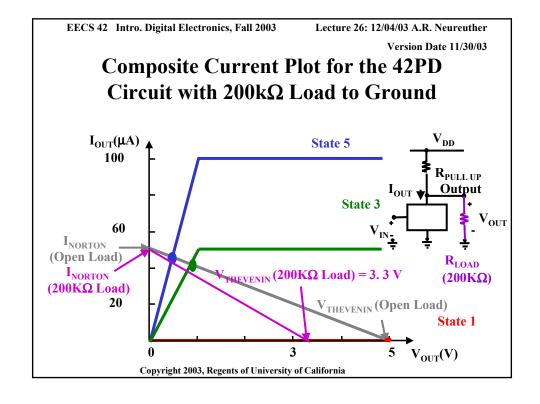

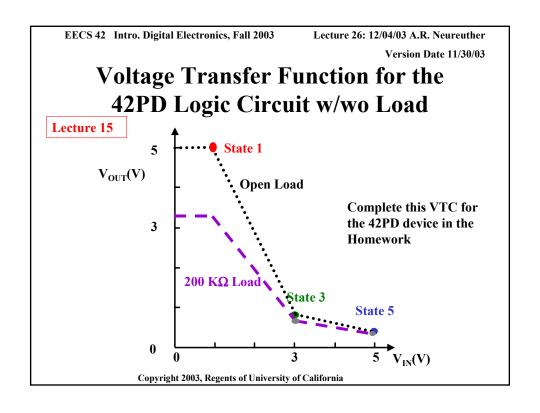

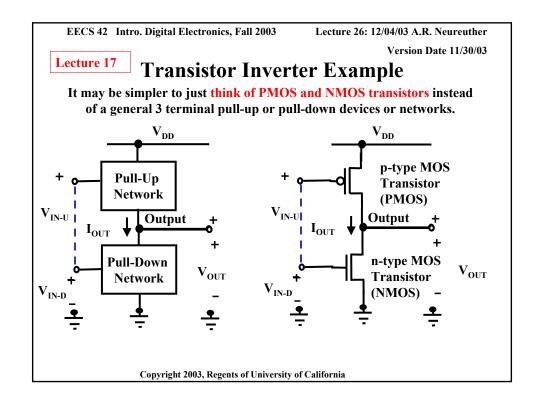

Load Line and Static Analysis of Logic Gates

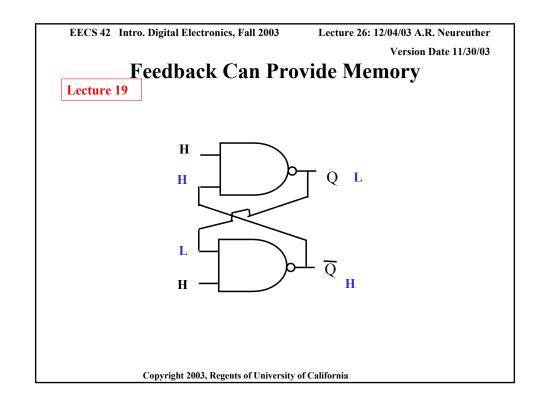

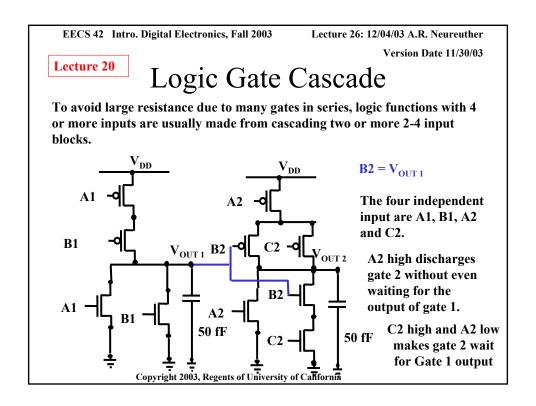

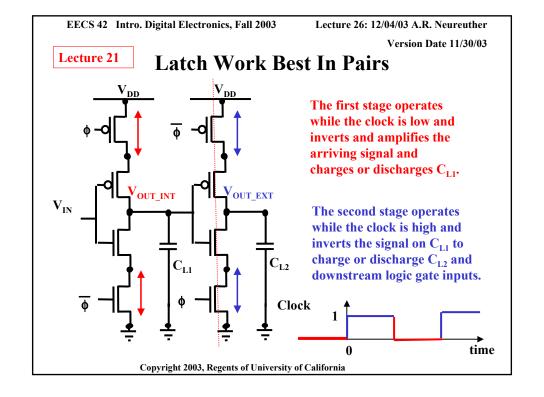

**CMOS Logic Functions, Delay, Latches**

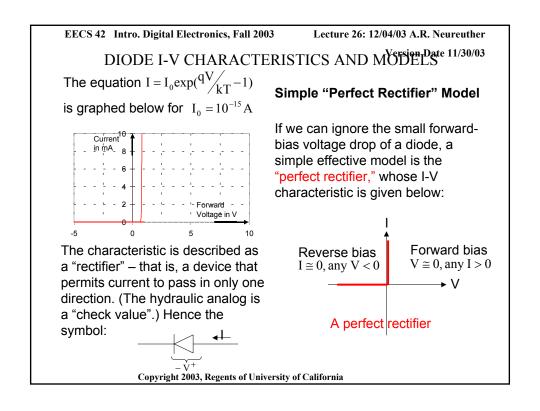

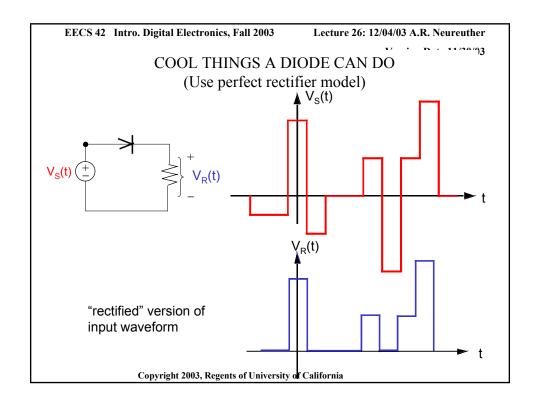

Diode Circuit Analysis, Voltage Controlled R

See Web Site under Exams for Coverage, Review Sessions and Office Hours

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 26: 12/04/03 A.R. Neureuther

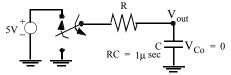

### Lecture 7

PULSE: Output is Rising exponential exponential

Example: Switch rises at t =0, falls at t = 0.1, 1 or 10µsec (Do 1µsec case)

Now starting at 1μsec we are discharging the capacitor so the form is a falling exponential with initial value 3.16 V:

Solution: for RC =  $1\mu$ sec: during the first rise V obeys:

$$V = 5[1 - e^{\frac{-t}{10^{-6}}}]$$

What is equation?

What is equation?

The state of the st

Thus at  $t = 1\mu sec$ , rising voltage reaches

$$5[1-e^{-1}] = 3.16V$$

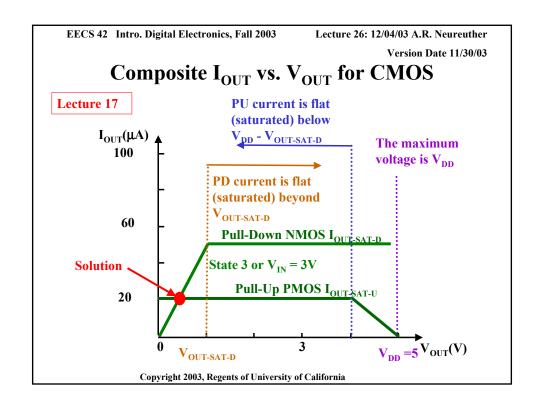

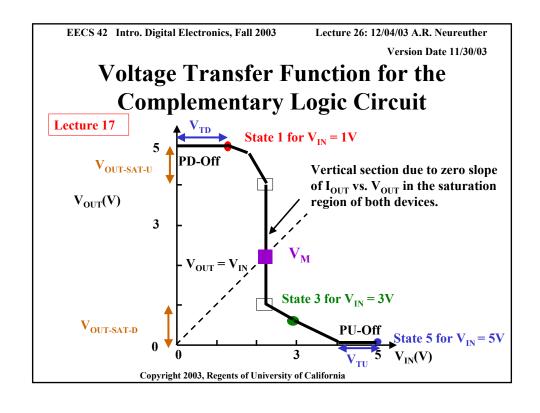

EECS 42 Intro. Digital Electronics, Fall 2003 Lecture 26: 12/04/03 A.R. Neureuther Version Date 11/30/03 Lecture 17 Saturation Current NMOS Model Current  $I_{OUT}$  only flows when  $V_{IN}$  is larger than the threshold value  $V_{TD}$  and the current is proportional to  $V_{OUT}$  up to  $V_{OUT\text{-SAT-D}}$  where it reaches the saturation current  $I_{OUT-SAT-D} = k_D (V_{IN} - V_{TD}) V_{OUT-SAT-D}$ Note that we have added an extra parameter to distinguish between threshold ( $V_{TD}\!)$  and saturation ( $V_{OUT\text{-}SAT\text{-}D}\!)$  . 100 **†**I<sub>OUT</sub>(µA) Example: Use these  $k_D=25~\mu A/V^2$ State 3  $V_{IN} = 3V$  $V_{TD} = 1V$ values in the Saturation (with V<sub>OUT</sub>) homework.  $V_{OUT-SAT-D} = 1V$ 60 Linear (with  $V_{OUT}$ )  $I_{OUT-SAT-PD} = 25 \frac{\mu A}{V^2} (3V - 1V) 1V = 50 \mu A$  20 Copyright 2003, Regents of University of California

$\frac{3}{4}$  V<sub>DD</sub> is the average value of V<sub>OUT</sub>

Approximate the NMOS device curve by a straight line from (0,0) to ( $I_{OUT\text{-}SAT\text{-}D}, {}^3\!\!/_4 \, V_{DD}$  ).

Interpret the straight line as a resistor with

slope =

$$1/R = \frac{3}{4} V_{DD}/I_{SAT}$$

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 26: 12/04/03 A.R. Neureuther

Version Date 11/30/03

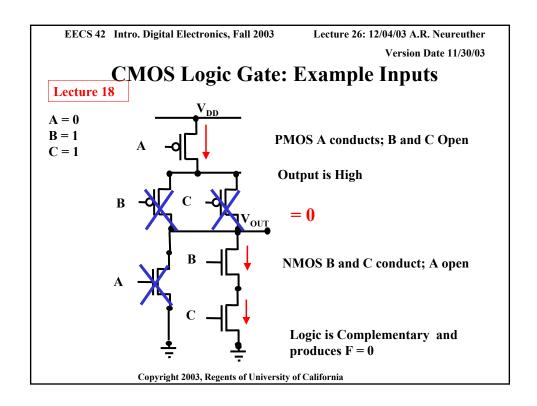

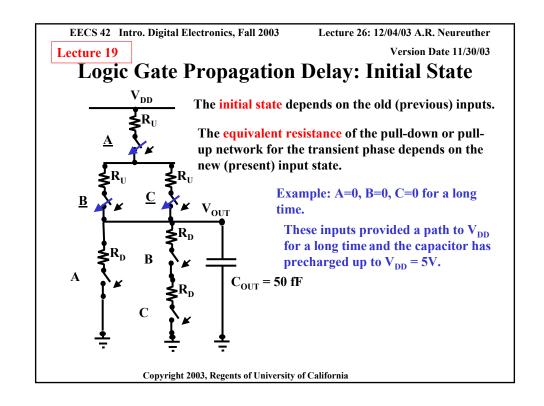

### Lecture 18

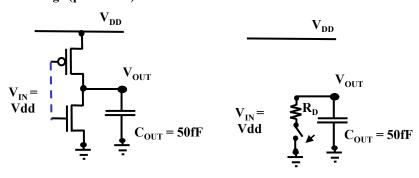

## **Inverter Propagation Delay**

Discharge (pull-down)

$\Delta t = 0.69 R_D C_{OUT} = 0.69 (10 k\Omega) (50 fF) = 345 ps$

Discharge (pull-up)

$$\Delta t = 0.69 R_U C_{OUT} = 0.69 (10 k\Omega) (50 fF) = 345 ps$$

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 26: 12/04/03 A.R. Neureuther

Version Date 11/30/03

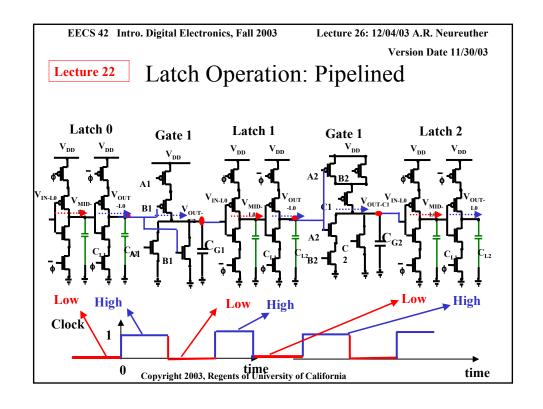

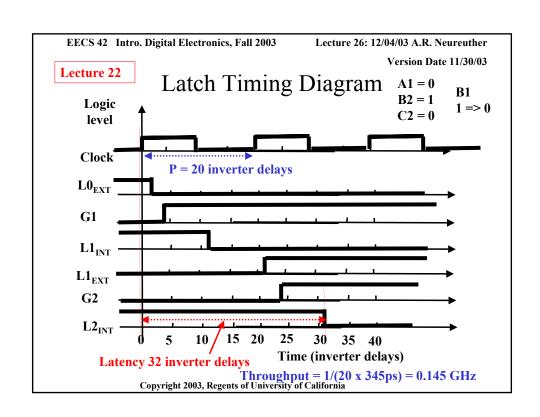

Lecture 22

# Latency and Throughput

Latency L is the delay between the rising edge of the clock on L0 and the data being valid internally in the last latch.

$$\begin{split} L_{LUMPED} &= \tau_{L\_EXT} + \tau_{GATE1} + \tau_{GATE2} + \tau_{L\_INT} \\ &= 2\tau_{INV} + 2\tau_{INV} + 2\tau_{INV} + 2\tau_{INV} = 8\tau_{INV} \end{split}$$

$$\begin{split} L_{PIPLINED} &= \tau_{L\_EXT} + \tau_{GATE1} + \tau_{L\_INT} + \tau_{L\_EXT} + \tau_{GATE2} + \tau_{L\_INT} \\ &= 2\tau_{INV} + 2\tau_{INV} + 2\tau_{INV} + 2\tau_{INV} + 2\tau_{INV} + 2\tau_{INV} = 12\tau_{INV} \end{split}$$

Throughput T is the bits per second through the latches and is the maximum clock frequency.

$$\begin{aligned} \mathbf{P}_{\text{LUMPED}} &= \mathbf{\tau}_{\text{L\_EXT}} + \mathbf{\tau}_{\text{GATE1}} + \mathbf{\tau}_{\text{GATE2}} + \mathbf{\tau}_{\text{L\_INT}} \\ &= 2\mathbf{\tau}_{\text{INV}} + 2\mathbf{\tau}_{\text{INV}} + 2\mathbf{\tau}_{\text{INV}} + 2\mathbf{\tau}_{\text{INV}} = 8\mathbf{\tau}_{\text{INV}} \end{aligned}$$

$$F_{LUMPED} = 1/8(345ps) = 0.36 \text{ GHz}$$

$$\begin{split} P_{PIPELINED} &= \tau_{L\_EXT} + MAX(\tau_{GATE1}, \tau_{GATE2}) + \tau_{L\_INT} \\ &= 2\tau_{INV} + 2\tau_{INV} + 2\tau_{INV} = 6\tau_{INV} \quad F_{PIPLINED} = 1/6(345ps) = 0.48 \text{ GHz} \end{split}$$

Copyright 2003, Regents of University of California

EECS 42 Intro. Digital Electronics, Fall 2003

Lecture 26: 12/04/03 A.R. Neureuther

Lecture 25: on blackboard

Version Date 11/30/03

## **Limitations of Power Consumption**

- The resistive load of NMOS results in D.C. current and hence static power consumption given by the product of current times voltage.

- CMOS avoids this static loss as the pull-up device shuts off the current completely.

- CMOS still suffers a.c. power consumption that is proportional to the switching frequency.

- $\, \cdot \,$  The energy expended per cycle of in charging and discharging can never be less than  $CV^2$

EECS 42 Intro. Digital Electronics, Fall 2003

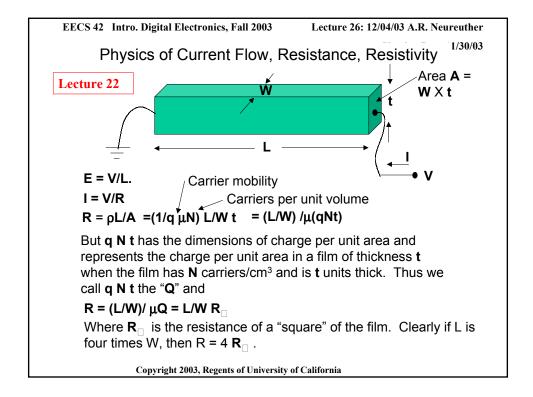

Relation of Current to Physical Parameters  $I_D = \mu_n C_{ox} \left(\frac{W}{L}\right)_n (V_{GS} - V_T) \cdot V_{OUT-SAT-n}$ Mobility of carriers

Oxide thickness

Oxide thickness  $\mu_n = 500 \left(cm^2 / V_S\right)$   $\mu_p = 150 \left(cm^2 / V_S\right)$   $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} = \frac{\left(8.85x10^{-14} F / cm\right)(3.9)}{6x10^{-7} cm} = 5.75x10^{-7} F / cm^2$   $V_{OUT-SAT-n} = E_{Crit} \cdot L = 10^4 \left(V / cm\right) \cdot 0.25x10^{-4} cm = 0.25V$