#### UNIVERSITY OF CALIFORNIA

College of Engineering Department of Electrical Engineering and Computer Sciences

Professor Oldham

Fall 2002

### EECS 42 — Final Exam

SOLUTIONS

Friday, 13 December 2002, 12:30-3:30 p.m.

| Name:      |       | Student ID: |  |  |

|------------|-------|-------------|--|--|

| Last,      | First |             |  |  |

| Signature: |       |             |  |  |

#### Guidelines:

- 1. Closed book. A summary with formulas is provided at the end of the exam.

- 2. Show all your work and reasoning on the exam in order to receive credit.

- 3. Warning: Some problems will be graded with no partial credit, so check your answers and be sure to put answers in boxes provided.

- 4. You may use a calculator.

- 5. Do not unstaple the exam. There are 2 blank pages at the end if you need more workspace.

- **6.** This exam contains 8 problems and corresponding worksheets plus the cover page and the 4-page summary with formulas.

- 7. Please do not ask questions except to point out possible errors or typographical mistakes.

| Problem | Points<br>Possible | Your<br>Score | Problem        | Points<br>Possible | Your<br>Score |

|---------|--------------------|---------------|----------------|--------------------|---------------|

| 1       | 25                 |               | 5              | 25                 |               |

| 2       | 30                 |               | 6              | 20                 |               |

| 3       | 25                 |               | 7              | 25                 |               |

| 4       | 25                 |               | 8              | 25                 |               |

|         |                    |               | Grand<br>Total | 200                |               |

|   |   | 1.5        |

|---|---|------------|

| f | = | $10^{-15}$ |

|   | = |            |

|   |   | $10^{-9}$  |

| μ | = | $10^{-6}$  |

| m | = | $10^{-3}$  |

| K | = | 103        |

| M | = | 106        |

|   |   |            |

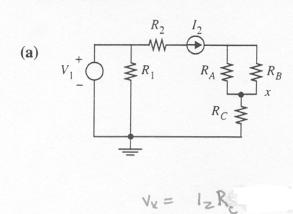

### Problem 1 (25 points)

Check "Yes" or "No" for each item in the following

|                  |           | Yes | No |

|------------------|-----------|-----|----|

| $V_x$ depends on | $V_1$ ?   |     | /  |

| "                | $R_1$ ?   |     | /  |

|                  | $R_2$ ?   |     | V  |

| н                | $R_A$ ?   |     | V  |

| n n              | $R_B$ ?   |     | 1  |

|                  | $R_{C}$ ? | ./  |    |

Find  $V_x$ .

$$V_x =$$

$\sim$  (V)

(c)

$$\begin{array}{c} + V_y \\ - \\ 3V \\ + \end{array}$$

Find  $V_y$ .

$$V_y = - \square$$

(V)

(d)

$$V_{\text{in}} + V_{a} - V_{a} + V_{a} - V_{a} + V_{a} + V_{a} - V_{a} + V_{a$$

$$V_0 = 5 V_A$$

$V_A = Vin - V_0$

$$= \frac{1}{6} Vin$$

$$V_0 = \frac{5}{6} \text{ Vin}$$

### Problem 2 (30 points)

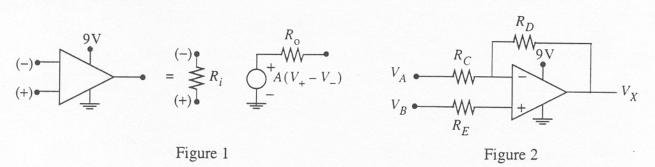

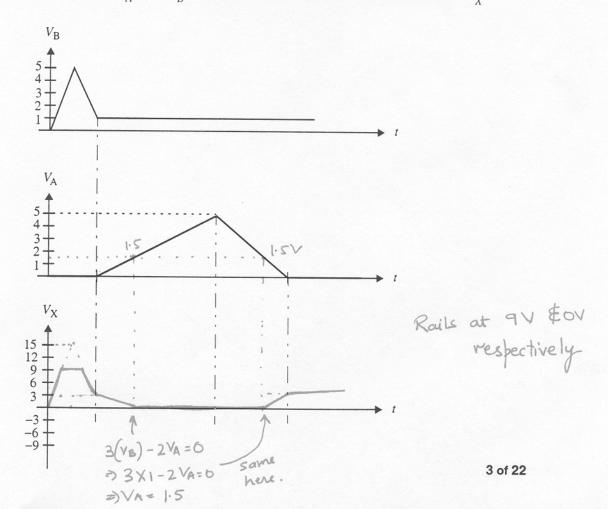

We are going to analyze the circuit of Figure 2. The op-amp model, valid in the linear region, is given in Figure 1. The linear region is bounded by the rails at 0V, 9V.

(a) For the op-amp circuit of Figure 2, derive the equation relating  $V_X$  to  $V_A$  and  $V_B$  in the linear region. Assume  $R_0 = 0$ ,  $R_i = \infty$ . You must show your work (use page 4).

$$V_X = \frac{A \cdot \left( V_B(R_C + R_D) - V_A R_D \right)}{R_C + R_D + A_R_C}$$

$$V_X = \frac{V_B + \frac{R_D}{R_C} \left( V_B - V_A \right)}{R_C}$$

(b) What does this become in the limit  $A \to \infty$ ?

$$V_X = \frac{V_B + \frac{R_D}{R_C} (V_B - V_A)}{R_C}$$

(c) Assume that for some values of  $R_C$ ,  $R_D$  and  $R_E$ , the equation for  $V_X$  is  $V_X = 3V_B - 2V_A$  (which need not be correct for the circuit given). Given  $V_A$  and  $V_B$  waveforms below, show the waveform for  $V_X$ .

## **Problem 2 Worksheet**

part (a)

$$V_{X} = A(V_{+} - V_{-})$$

- . . . (i)

$$V+=YB$$

. . . . (ii)

$$V_{-} = V_A + \frac{(V_X - V_A)Rc}{Rc + RD}$$

... (iii)

from (i), (ii) & (iii), we get.

$$V_{X} = A \left( V_{B} - \left( V_{A} + \frac{(V_{X} - V_{A})R_{C}}{R_{C} + R_{D}} \right) \right)$$

$$\Rightarrow \forall x \left( \frac{\bot}{A} + \frac{Rc}{Rc + RD} \right) = \forall B - \forall A + \frac{\forall ARc}{Rc + RD}$$

=)

$$V_X \left( \frac{R_C + R_D + AR_C}{A \left( R_C + R_D \right)} \right) = \frac{V_B \left( R_C + R_D \right)}{\left( R_C + R_D \right)}$$

$$=) \qquad \forall x = A. \left[ \frac{V_B(R_C + R_D) - V_A R_D}{R_C + R_D + AR_C} \right] \xrightarrow{An}$$

pont (b)

$$\lim_{A \to \infty} Vx = \lim_{A \to \infty} \frac{A \left( V_B(Rc+R_D) - V_A R_D \right)}{Rc+R_D + ARC}$$

$$= \lim_{A \to \infty} \frac{V_B(Rc+R_D) - V_A R_D}{\frac{(Rc+R_D)}{A} + RC}$$

$$\Rightarrow Vx = \frac{V_B(R_C + R_D) - V_A R_D}{R_C}$$

$$\Rightarrow V_X = V_B + \frac{R_D}{R_C} (V_B - V_A) A_{MS}$$

### Problem 3 (25 points)

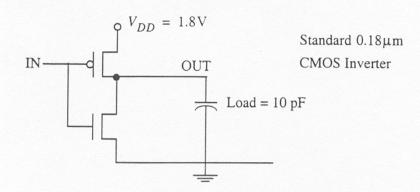

The CMOS inverter shown must drive a load (which is a very long line on the chip) with a capacitance of 10 pF. We require that both the rising and falling stage delays be 0.5 nsec.

The device properties are given in Lecture 22 summary at the end of the exam. But for this problem use  $\lambda = 0$ .

(a) What value of  $R_P$  and  $R_N$  are required to achieve the 0.5nsec stage delay?

$$R_p = R_N = R$$

$0.69 \ R^c = 0.5 \times 10^{-9} \ sec$

$c = 10 \times 10^{-12} F$

$\Rightarrow R = 72.5 \ T$

$$R_P = 72.5 \Omega$$

$$R_N = 72.5 \Omega$$

(b) Suppose the answer to part A were  $R_P = 100\Omega$ ,  $R_N = 100\Omega$  (not the right answers!). What NMOS and PMOS device widths would be required? (Standard 0.18µm device properties, but with  $\lambda = 0$ .)

$$R_{p} = R_{N} = \frac{0.75 \text{ Vdd}}{I_{AVE} = I_{DS}} = \frac{0.75 \times 1.8}{W \cdot I_{DS}' \cdot |V_{GS} - V_{T}|} = \frac{0.75 \times 1.8}{W_{P} = 38.6 \text{ um}}$$

$$R_{N} = 100, W_{N} = 19.3 \text{ um}$$

$$R_{p} = 100, W_{p} = 38.6 \text{ um}$$

$$W_{p} = 38.6 \text{ um}$$

$$W_{N} = 19.3 \text{ um}$$

$$250 \times 10^{-6} (PMS)$$

(c) At what input voltage does the maximum current flow from  ${\cal V}_{DD}$  to ground?

At

$$Vin = \frac{1}{a}Vdd$$

, both transistors

are on "half-way" and current flows

through  $Vad \rightarrow Ground$  (cap. is irrelevant)

VIN = 0.9V

(d) What is the value of the current?

$$\lambda = 0$$

)  $I_D = I_{DS} = W \times I_{DS} \times |V_{GS} - V_T|$   $I = 4.82$  mA

=  $|9.29 \times 500 = 6 \times (0.9 - 0.4)$

=  $4.82$  mA

# Problem 4 (25 points) - Please give answers on page opposite

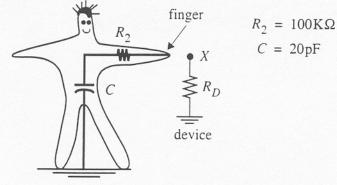

As you may know, electrostatic discharge can destroy CMOS circuits by "zapping" the gate insulators. The equivalent circuit of a Berkeley undergraduate on a nylon carpet is given below:

Undergrad Circuit Model

Suppose C is initially charged to 25KV by a short walk on the carpet.

(a) What is the energy stored in the capacitor?

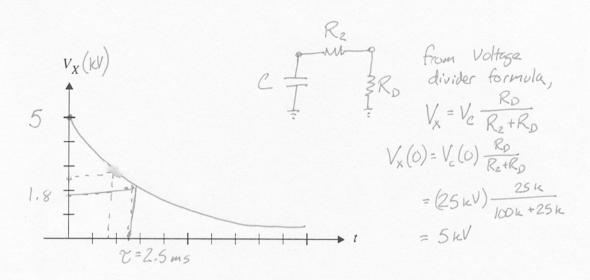

(b) Let  $R_D$  represent a device you touch at t = 0 (finger touchs X, connecting  $R_2$  to  $R_D$ ).  $R_D = 25 \text{K}\Omega$ . Sketch the voltage on node X versus time.

(c) Write an equation for the voltage  $V_X(t)$ .

(d) Your strategy to protect the device is to put a series resistance  $R_S$  on your finger so big that  $V_X$  never rises above 10 V. (That is,  $R_S$  is in series with  $R_2$ .)

How big must  $R_S$  be?

### **Problem 4 Answer Sheet**

$$E = \frac{1}{2}CV^{2} = \frac{1}{2}(20 \times 10^{-12}F)(25 \times 10^{3}V)^{2}$$

$$= 6.25 \text{ mJ}$$

(b)

Capacitor is discharging

$$V_X(t) = \frac{(5kV)e^{-t/2.5ms}}{V_X(t)} = \frac{R_D}{R_2 + R_D} V_2(t) = \frac{R_D}{R_2 + R_D} (25kV)e^{-t/2.5ms}$$

$$= (5kV)e^{-t/2.5ms}$$

(d)

$$\frac{V_{e}}{V_{e}} = 25 \text{ kV}$$

$$R_{z} = 25 \text{ kV}$$

$R_S = 62.375 \quad M\Omega$

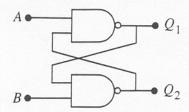

# Problem 5 (25 points)

A non-standard flip-flop circuit is given below:

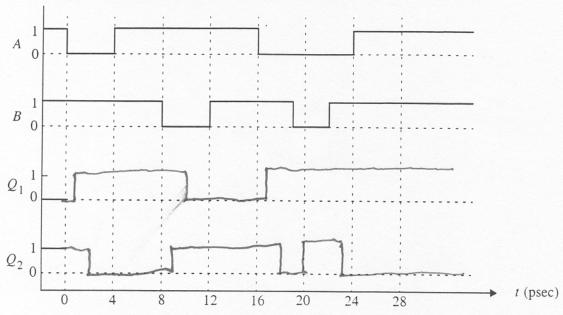

(a) A possible set of input waveforms is given below. Show the behavior of  $Q_1$  and  $Q_2$  assuming the unit gate delay is 1 psec. (Do **NOT** ignore gate delay in your diagram.)

**(b)** Under what input conditions is  $Q_2 \neq \overline{Q}_1$ ?

| A = | 0 |  |

|-----|---|--|

| B = | 0 |  |

(c) Under what input conditions is  $Q_2 = \overline{Q}_1$  and  $Q_1$  is free to be either 0 or 1 (depending on previous history)?

(d) How many PMOS and NMOS devices would it take to construct this circuit?

| NMOS _ | 4 |  |

|--------|---|--|

| PMOS   | 4 |  |

### Problem 6 (20 points)

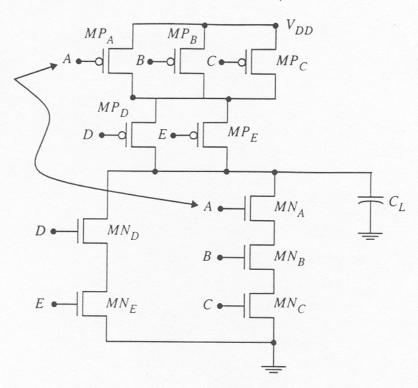

The following special CMOS logic circuit is constructed in our standard  $0.25 \mu m$  CMOS.

Note: A is actually connected to A, etc., but these wires are omitted for simplicity.

(a) Write the expression for the logic function  $\overline{F}$  in terms of A, B, C, D, E.

$$\bar{F} = ABC + DE$$

(b) Assume devices  $MN_D$  and  $MN_E$  are  $2\mu m$  wide, size all the remaining devices so that they are as small as possible, but the worst case fall time equals the worst case rise time, i.e., find all device widths.

$$W_{MP_A} = \Delta \omega m$$

$W_{MN_A} = \Delta \omega m$

$W_{MN_B} = \Delta \omega m$

$W_{MN_C} = \Delta \omega m$

$W_{MN_C} = \Delta \omega m$

$W_{MN_C} = \Delta \omega m$

# Problem 7 (25 points)

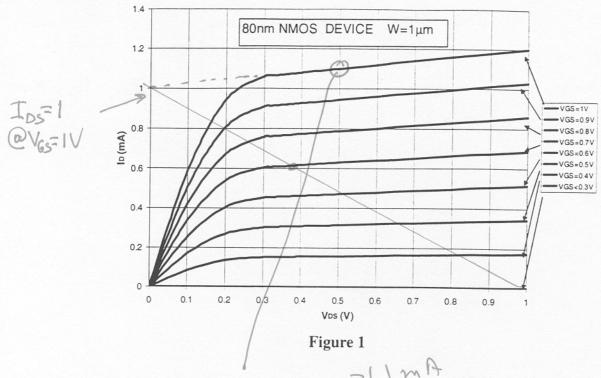

The I-V graph of a super high performance experimental NMOS device is given in Figure 1. The device Width is  $W = 1 \mu \text{m}$ .

(a) What is  $I_D$  if  $V_{GS} = 1V$ ,  $V_{DS} = 0.5V$  (±10%)?  $\nearrow I_1 \setminus m$

(b) Can you estimate values for  $V_T$ ? T > 0 at  $V_0 > V_T$

$V_T = 0.3$

(c) What is the value of the parameter  $I_{DS}$  for this device ( $\pm 10\%$ )?

(d) What is the value of the parameter  $\lambda$  for this device ( $\pm 20\%$ )?

$\lambda = \sqrt{5} = 0.2 \text{ V}^{-1}$

(e) What is  $I_D$  in this circuit? 0.7V  $\longrightarrow$  device above

ID = 0,61m

13 of 22

# Problem 8 (25 points)

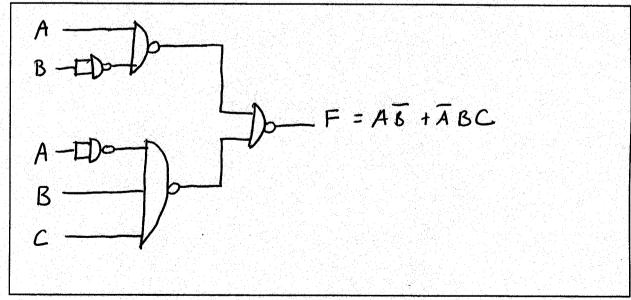

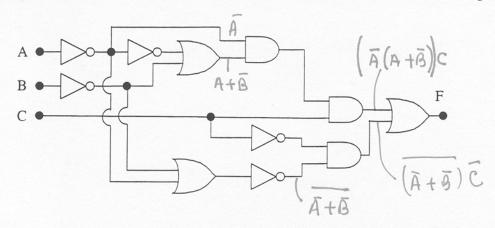

A recent Stanford graduate performed a logic design and proudly came up with the following logic circuit:

(a) Write the logic function directly from the circuit without simplification (please, <u>without simplification</u>). There is only one correct answer for this part, even though you may greatly simplify the expression with little effort.

(b) Simplify the expression for F.

(c) The answer to part (c) is not  $A\overline{B} + \overline{A}BC$ , but for this part of the problem we will assume that the answer to part (c) is  $F = A\overline{B} + \overline{A}BC$ . Design a logic circuit for this function using only NAND gates, with inputs A, B, C and output F.

### **Problem 8 Answer Sheet**

(a)

(b)

$$F = (\overline{A} + \overline{B}) A C + (\overline{A} + \overline{B}) \overline{C}$$

$$= (A + \overline{B}) \overline{A} C + (\overline{\overline{A} \cdot \overline{B}}) \overline{C}$$

(c) Draw circuit here: