## Lecture 27/28

Last time:

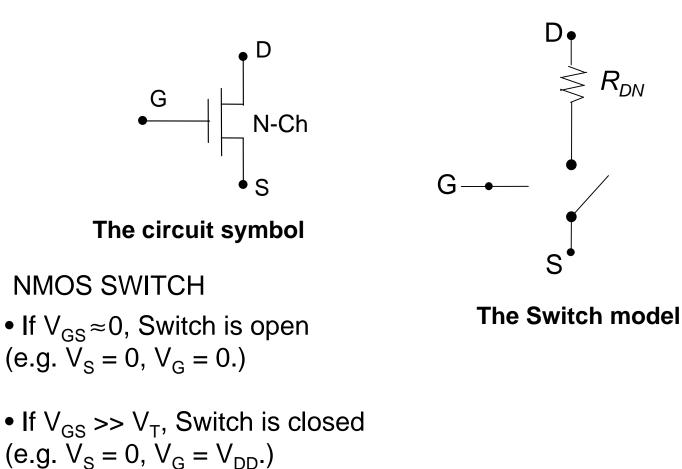

NMOS = n-channel Metal Oxide Semiconductor Field Effect Transistor

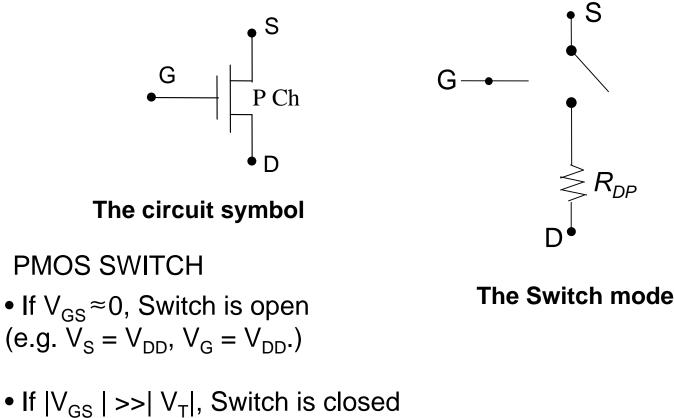

CMOS is a process that uses both NMOS and PMOS devices (complementary)

NMOS and PMOS Switch Models

Today -

- NMOS and PMOS models including Capacitance

- •CMOS inverter electrical behavior

- •Glimpse of layout (more next time)

# NMOS Circuit Model

#### NMOS transistor has an equivalent resistance $R_{DN}$ when closed

W Oldham

(e.g.  $V_{S} = V_{DD}, V_{G} = 0.$ )

# PMOS Circuit Model

#### PMOS transistor has an equivalent resistance $R_{DP}$ when closed

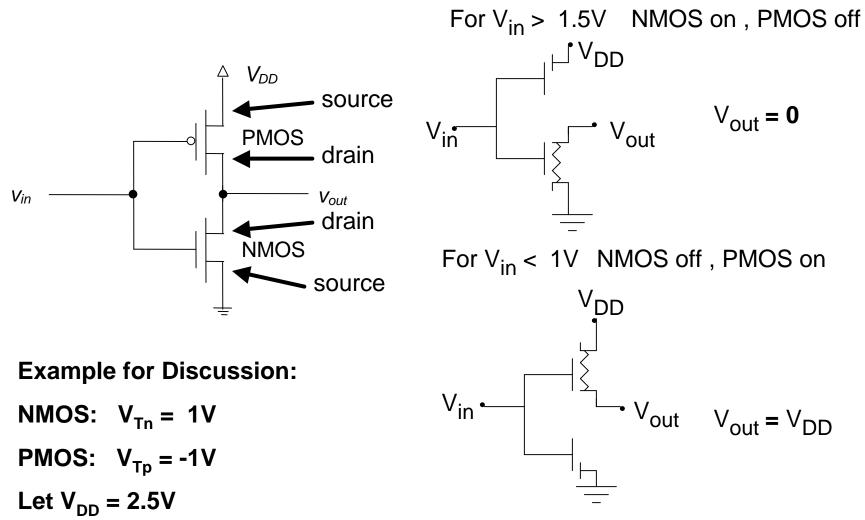

#### THE BASIC STATIC CMOS INVERTER

4

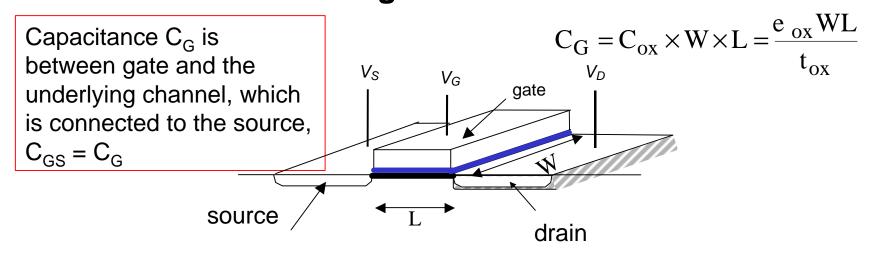

### Model Refinements: Add Gate Capacitances Node connected to the gate:

The gate capacitance is the dominant capacitance, perhaps 60-80% of total node capacitance. So we will focus just on it.

To compute it we need the gate capacitance per unit area ( $e_{0x}/t_{0x}$ ) and the gate area (W x L).

The CMOS Inverter  $\cdot V_{DD}$ S<sub>p</sub> (;**≓B**⊳) Symbolic circuit Model  $R_p$ **Ç**<sub>Gp</sub> V<sub>DD</sub> MODE Gp .<u>D</u>p... **V**out Vin Vin Vout  $\boldsymbol{\mathsf{D}}_{\mathsf{n}}$  $G_n$  $C_{Gn}$  $R_n$ ÷  $S_n = B_n$ ÷

Note that the switches are NOT independent , in fact they are "ganged"

6

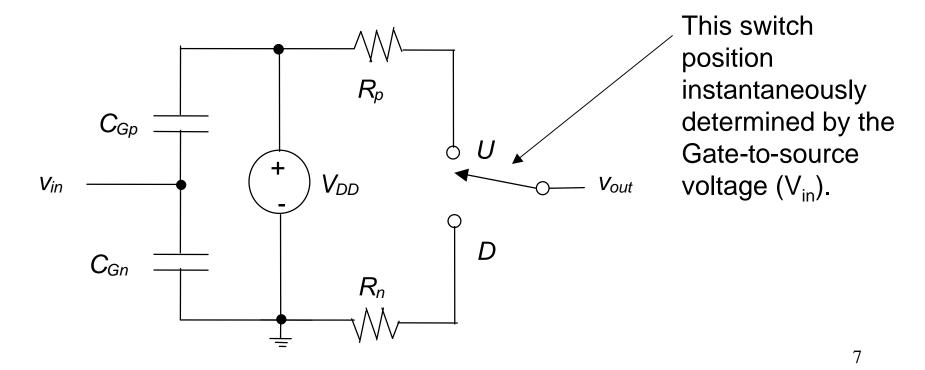

# First Order CMOS Inverter Model

The switches are "ganged" (move together) since they have essentially the same trip voltages

NMOS is closed when V<sub>in</sub> high ; PMOS is open

PMOS is closed when  $V_{in}$  low ; NMOS is open

Reduce to a single switch: (Whose position depends on  $V_{in}$ )

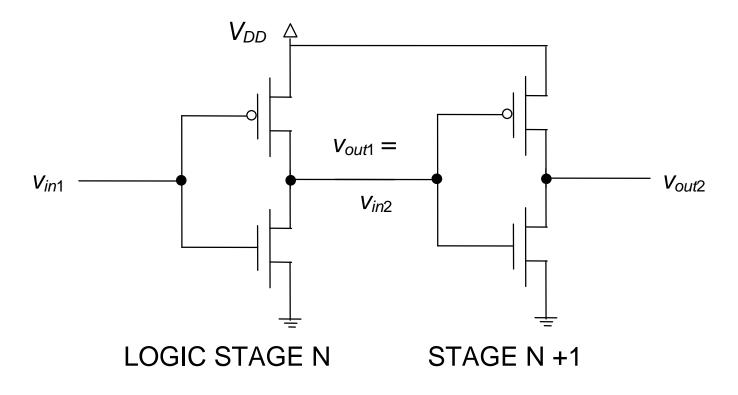

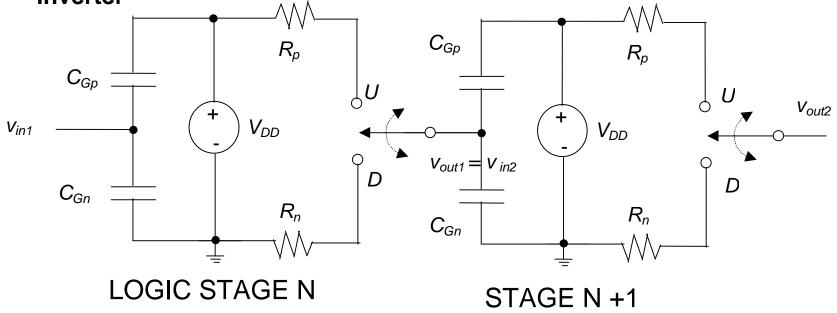

### "Cascaded" CMOS Inverters

# What's connected to the $v_{out}$ node? Answer: One or more logic gates, for example another CMOS inverter

Note that there are no resistors, capacitors, inductors in a CMOS circuit -- there are only NMOS and PMOS transistors.

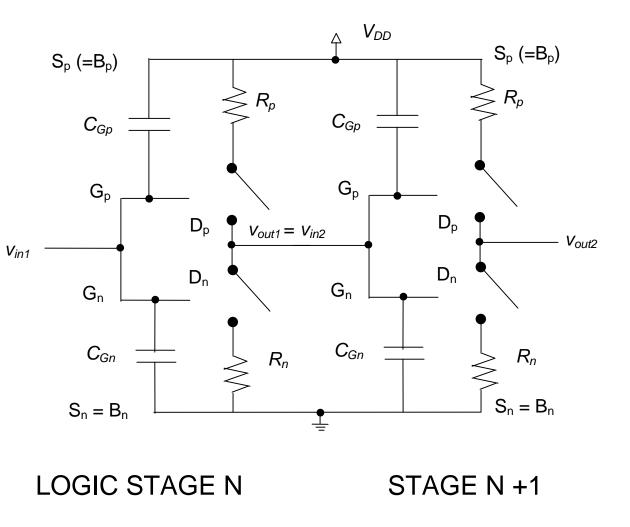

### Cascaded Identical CMOS Inverter Circuit Model

Full switch model showing gate capacitances.

Note that it is the gate capacitance of Stage N +1 combined with the drain resistance of Stage N that slow the gate charging of Stage N +1.

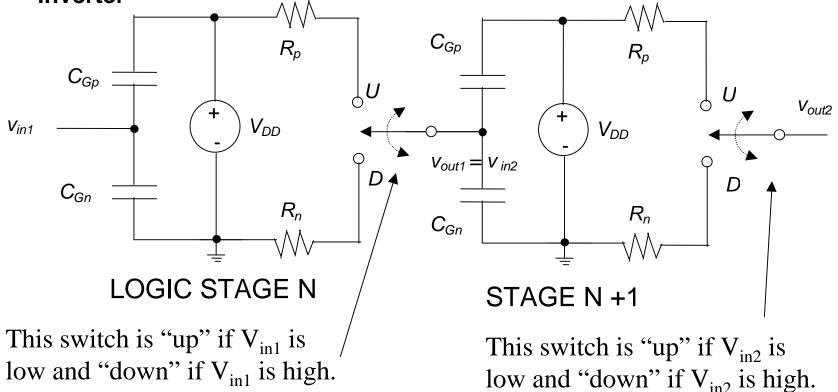

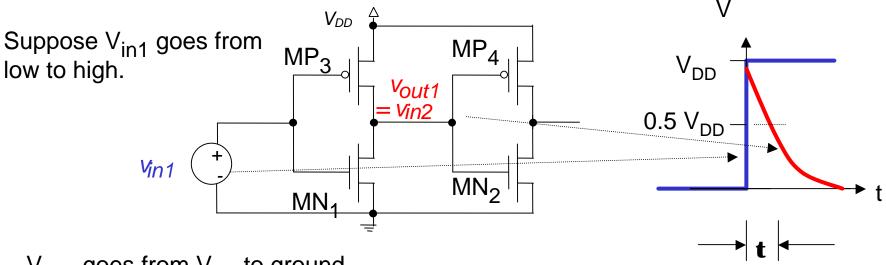

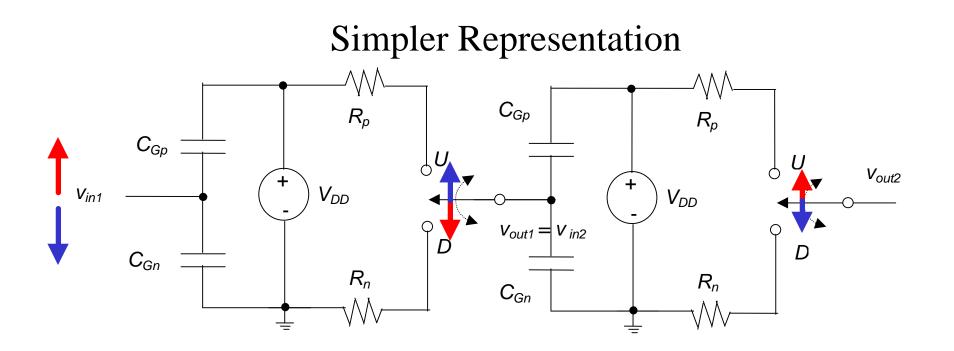

### Simpler Representation

NMOS and PMOS transistors have the same logic thresholds, but operate in a complementary fashion  $\rightarrow$  reduce to a single switch per inverter

### Simpler Representation

NMOS and PMOS transistors have the same logic thresholds, but operate in a complementary fashion  $\rightarrow$  reduce to a single switch per inverter

**Transitions of interest:**

1.  $v_{in1}$  goes high : switch for inverter 1 moves to "D" position from previous "U" position (and subsequently output switch goes to "U")

2.  $v_{in1}$  goes low : switch for inverter 1 moves to "U" position from previous "D" position (and subsequently output switch goes to "D") 11

#### Gate-Delay Analysis -- Identify key Components

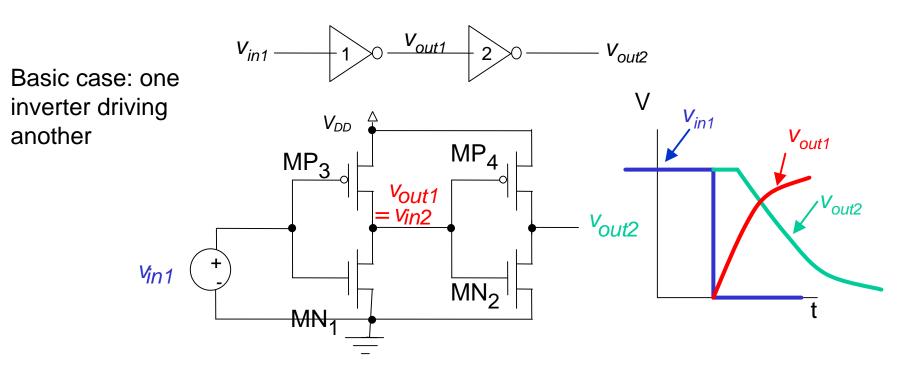

Suppose  $V_{in1}$  goes from high to low.  $\rightarrow$  MP<sub>3</sub> turns on and MN<sub>1</sub> turns off.

Then  $V_{out1}$  goes from low to high (but a little bit later ... i.e. delayed ). Of course  $V_{in2}$  is the same as  $V_{out1}$ .

Thus  $V_{out2}$  goes from high to low (delayed even more from the input  $V_{in1}$ ).

#### How to define the inverter delay

$V_{out1}$  goes from  $V_{DD}$  to ground.

We define the inverter stage delay  ${\bf t}$  as the time until  $V_{out1}$  reaches  $V_{DD}$  /2 .

Because when it reaches this value, the following stage will sense that its input has switched from high to low.

The properly designed stage will have nearly the identical stage delay time for rising input as for falling input. (Design proper ratio of  $W_p$  to  $W_n$ )

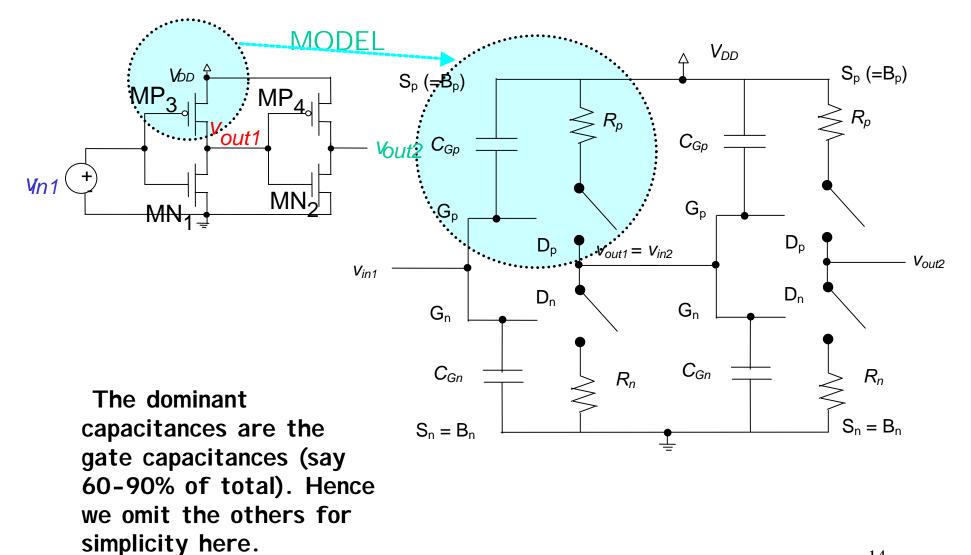

#### Cascaded Identical CMOS Inverter Circuit Model

14

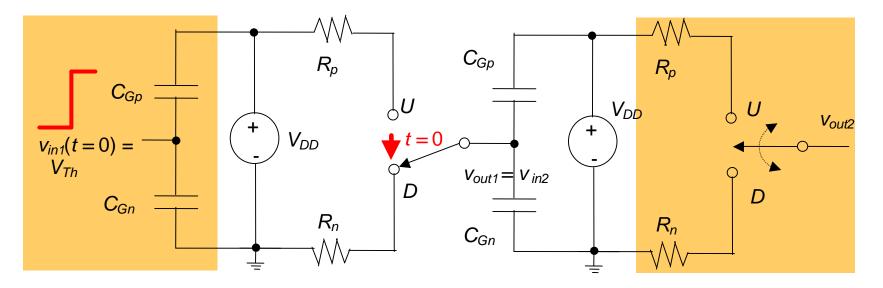

#### **Transitions of interest:**

1.  $V_{in1}$  increases above  $V_{Th}$ : switch for inverter 1 moves to "D" position from previous "U" position. Of course  $V_{out2}$  will follow (switch up).

2.  $V_{in1}$  decreases below  $V_{TI}$ : switch for inverter 1 moves to "U" position from previous "D" position. Of course  $V_{out2}$  will follow (switch down).

#### Where's the Delay?

Suppose the switch moves instantaneously ... what is the origin of gate delay?

Cascaded inverters  $\rightarrow$  input capacitance of the second inverter ("the load") must be charged (or discharged) by current from the first inverter ("the driver") ... this takes time! (And there are additional capacitances at this node...)

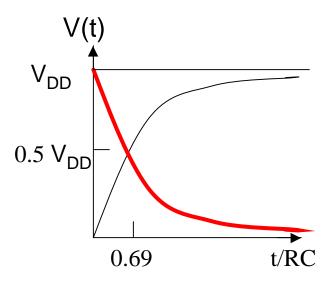

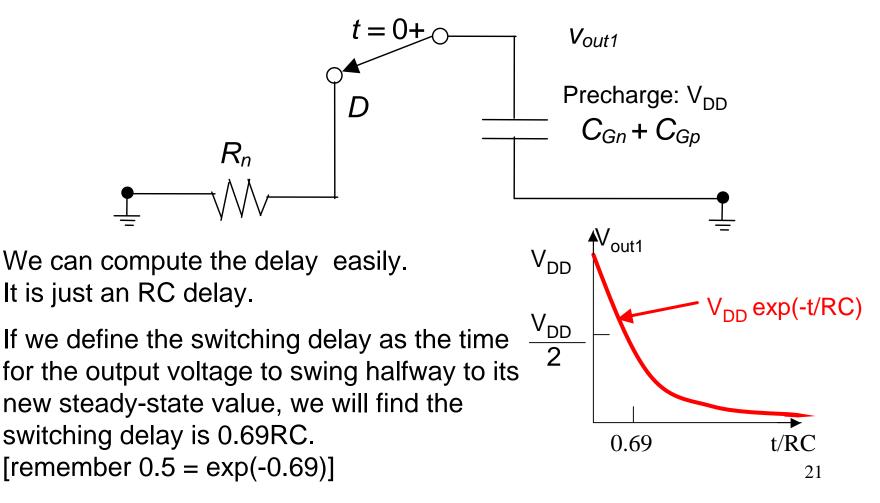

But we can compute the delay easily. It is just an RC delay. If we define the switching delay as the time for the output voltage to swing halfway to its new steady-state value, we will find the switching delay is 0.69RC.

Remember if  $V(t) = V_{DD} \exp(-t/RC)$ ] then  $V(t) = V_{DD}/2$  at t= 0.69RC. [Because 0.5 = exp(-0.69)]

# Where's the Delay?

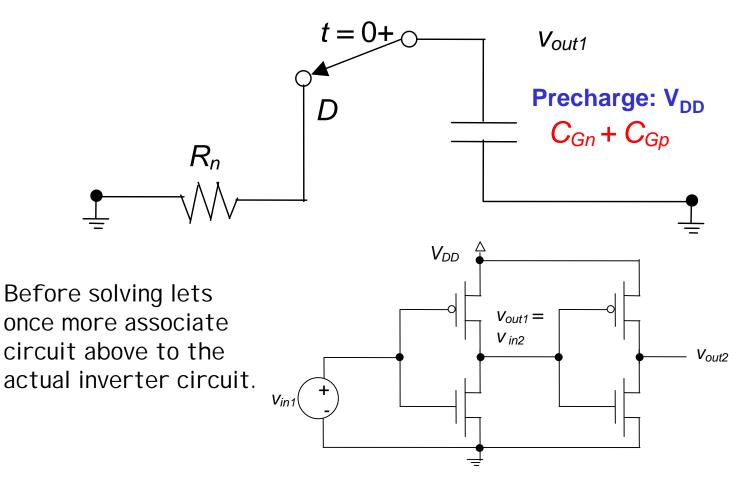

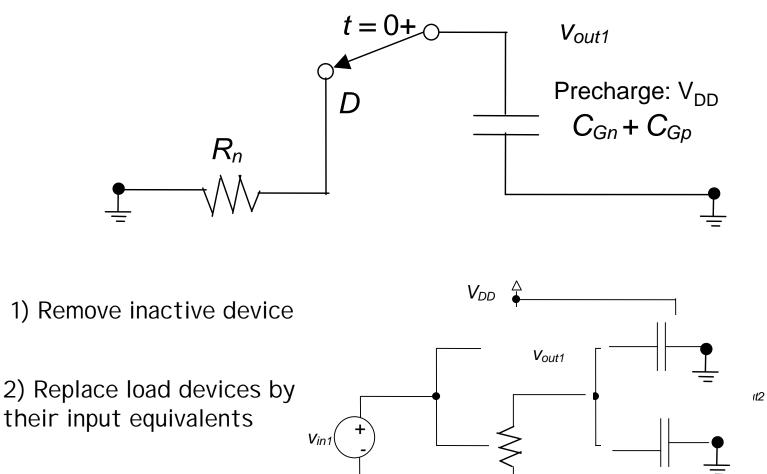

Equivalent circuit for transition 1: note that  $v_{out1}(t = 0+) = V_{DD}$

Shaded areas play no role in finding  $v_{out1}(t)$ .

So lets redraw the circuit with essential elements only ..... eliminate shaded stuff.

18

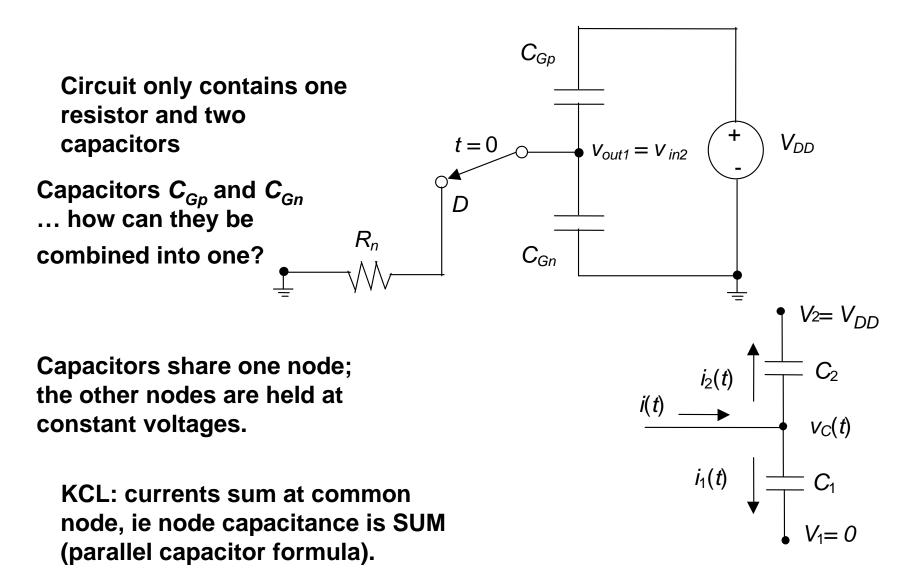

#### Core Circuit for "Pull-Down" Transition

"Virtually Parallel" Capacitors

# Pull-Down Equivalent Circuit

Two capacitors add for finding the charging current  $\rightarrow$  applies to gate capacitances

# Equivalent circuit vs actual circuit

3) Replace NMOS pulldown by by its output equivalent.

## Gate Delay from Pull-Down Equivalent Circuit

Capacitor is precharged to  $V_{\text{DD}}$  and discharged to ground through resistance  $\textbf{R}_{n}.$

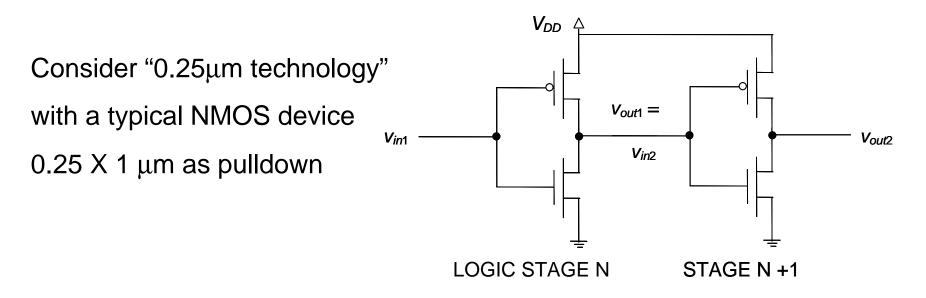

# **Typical values:**

The typical  $R_{DN}$  value is  $4K\Omega$

and the typical minimum load value is 5fF.

Thus RC = 20 pS

and the stage delay would be .69 X 20 or 14pS.