# **Discussion Section 3**

Sean Huang January 29, 2021

### FPGAs: Building Blocks of Logic

#### **FPGA Structure**

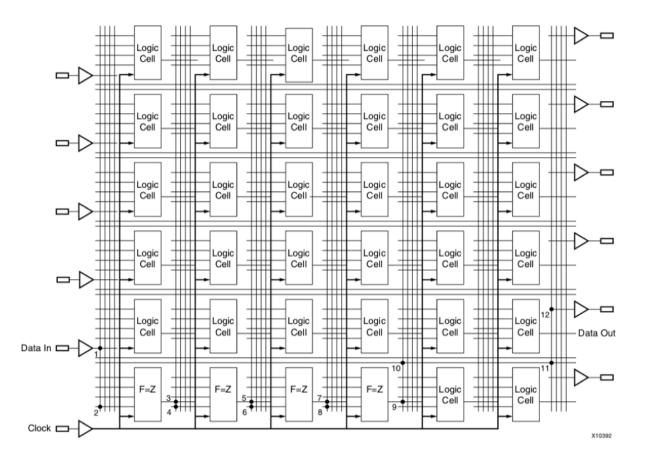

- Array of "Logic Cells" and interconnect

- What are "Logic Cells" exactly?

- How to implement every possible logic function in finite space?

- How to adapt to any N-bit wide input?

### **Truth Tables**

- Completely characterizes logic function

- Any N-input function requires  $2^N$  rows to fully define

- Map input to output for all possible inputs

- Could we represent logic functions this way?

| С | b | а | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 0 | 1 | 0 | 1   |

| 0 | 1 | 1 | 0   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | 1   |

# Look-Up Tables (LUTs)

- Like a hardware truth table

- Map each input to corresponding output

| 2 | b | а | out |       |     |

|---|---|---|-----|-------|-----|

| 0 | 0 | 0 | 0   |       |     |

| 0 | 0 | 1 | 1   |       |     |

| 0 | 1 | 0 | 1   | a ——— |     |

| 0 | 1 | 1 | 0   | b ——— | LUT |

| 1 | 0 | 0 | 1   | с ——— |     |

| 1 | 0 | 1 | 0   | -     |     |

| 1 | 1 | 0 | 0   |       |     |

| 1 | 1 | 1 | 1   |       |     |

— out

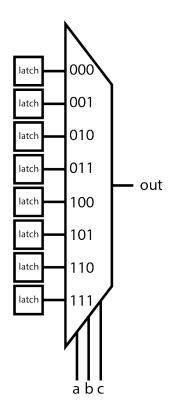

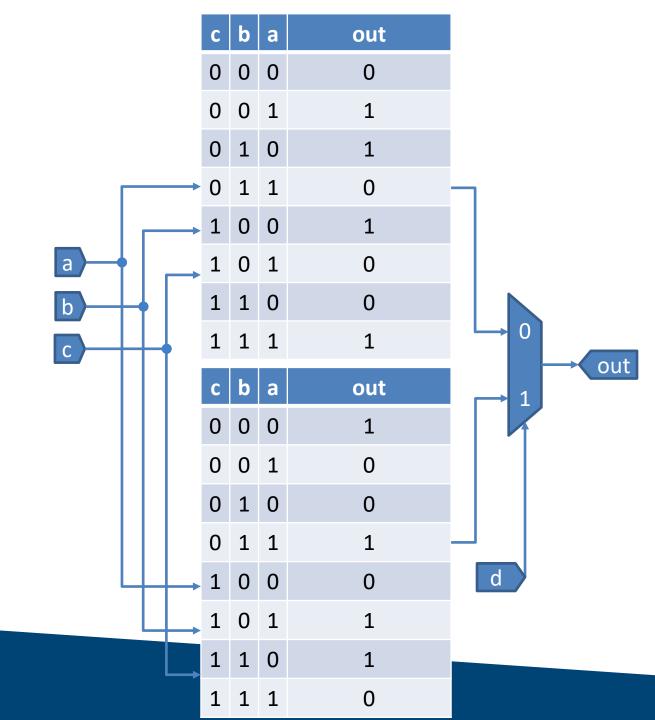

# Look-Up Tables (LUTs)

- Like a hardware truth table

- Map each input to corresponding output

- Easy way to implement

- Use mux with programmable latches on each input

- Program Latch to correspond to expected output

- Select output with inputs to LUT

| С | b | а | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 0 | 1 | 0 | 1   |

| 0 | 1 | 1 | 0   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | 1   |

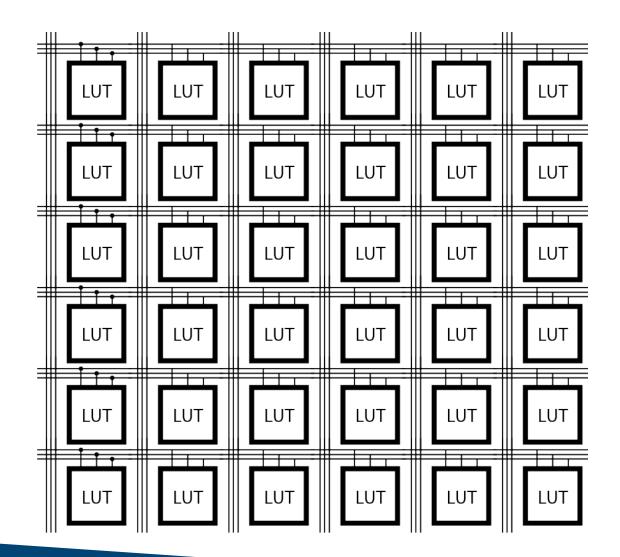

#### Proto-FPGA

- Array of LUTs and interconnect

- Here's a proto-FPGA of 3-input LUTs

- Can perform any combination of 3input logic functions!

- What if we want to have a 4-input function?

# **Building Bigger LUTs**

- Consider a 4-input LUT

This one is a 4-input XOR

- How to build this out of 3 input LUTs?

| d | С | b | а | out |

|---|---|---|---|-----|

| 0 | 0 | 0 | 0 | 0   |

| 0 | 0 | 0 | 1 | 1   |

| 0 | 0 | 1 | 0 | 1   |

| 0 | 0 | 1 | 1 | 0   |

| 0 | 1 | 0 | 0 | 1   |

| 0 | 1 | 0 | 1 | 0   |

| 0 | 1 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1 | 1   |

| 1 | 0 | 0 | 0 | 1   |

| 1 | 0 | 0 | 1 | 0   |

| 1 | 0 | 1 | 0 | 0   |

| 1 | 0 | 1 | 1 | 1   |

| 1 | 1 | 0 | 0 | 0   |

| 1 | 1 | 0 | 1 | 1   |

| 1 | 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1 | 0   |

# **Building Bigger LUTs**

- Consider a 4-input LUT

This one is a 4-input XOR

- How to build this out of 3 input LUTs?

- Notice how the LUT depends on d

- Can split into d=0 and d=1 halves

- abc inputs look identical!

Berkelev

|         | d | С | b | а | out |

|---------|---|---|---|---|-----|

| ſ       | 0 | 0 | 0 | 0 | 0   |

|         | 0 | 0 | 0 | 1 | 1   |

|         | 0 | 0 | 1 | 0 | 1   |

| d = 0   | 0 | 0 | 1 | 1 | 0   |

| u - 0   | 0 | 1 | 0 | 0 | 1   |

|         | 0 | 1 | 0 | 1 | 0   |

|         | 0 | 1 | 1 | 0 | 0   |

|         | 0 | 1 | 1 | 1 | 1   |

| (       | 1 | 0 | 0 | 0 | 1   |

|         | 1 | 0 | 0 | 1 | 0   |

|         | 1 | 0 | 1 | 0 | 0   |

| d=1     | 1 | 0 | 1 | 1 | 1   |

| d = 1 🖌 | 1 | 1 | 0 | 0 | 0   |

|         | 1 | 1 | 0 | 1 | 1   |

|         | 1 | 1 | 1 | 0 | 1   |

|         | 1 | 1 | 1 | 1 | 0   |

# **Building Bigger LUTs**

- Consider a 4-input LUT

This one is a 4-input XOR

- How to build this out of 3 input LUTs?

- Notice how the LUT depends on d

- Can split into d=0 and d=1 halves

- abc inputs look identical!

Rerkelev

#### LUT Caveats

- <u>Can</u> implement any logic function as a LUT

- Just because you can doesn't mean you should

- Ex: 64-inputs require 2<sup>64</sup>=1.84x10<sup>19</sup> lines of LUT!

- Bit width common in arithmetic or encoders

- Might use LUTs for sub-blocks

- LUT not most efficient way to implement a function

- But it is very straightforward

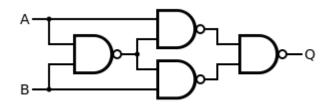

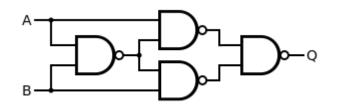

#### Boolean Algebra

• How would you build an XOR gate out of only ANDs and ORs?

- How would you build an XOR gate out of only ANDs and ORs?

- Spoiler: You can't

- Need a NOT for functional completeness

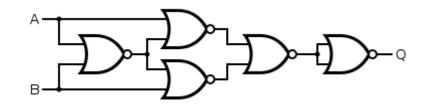

- Are NANDs functionally complete? Can you make an XOR out of them?

- How would you build an XOR gate out of only ANDs and ORs?

- Spoiler: You can't

- Need a NOT for functional completeness

- Are NANDs functionally complete? Can you make an XOR out of them?

- What about NORs?

- How would you build an XOR gate out of only ANDs and ORs?

- Spoiler: You can't

- Need a NOT for functional completeness

- Are NANDs functionally complete? Can you make an XOR out of them?

- What about NORs?

# Logic as Math

- Basic operators

- AND (\*, ∧)

- − OR (+, ∨)

- NOT(  $\neg$ , ', !, ~, or "bar" ex:  $\overline{a}$ )

- Order of Operations

- Similar to arithmetic, AND (\*) is done before OR (+), NOT takes precedence over AND

- $a'b + bc = ((a') \cdot b) + (b \cdot c)$

- Laws and Properties

- Boolean Algebra has its own set of laws and properties to simply expressions

### Properties

- Properties listed in Lecture 6 Slides

- Useful for transforming expressions to be easier to simplify

- Here is a selection of some useful ones

| ab = bc                         | a + b = b + a                          | $a^{\prime\prime} = a$ |           |

|---------------------------------|----------------------------------------|------------------------|-----------|

| (ab)c = a(bc)                   | (a+b) + c = a + (b+c)                  | $a \cdot 0 = 0$        | a + 1 = 1 |

| a(b+c) = ab + ac                | a + bc = (a + b)(a + c)                | $a \cdot 1 = a$        | a + 0 = a |

| $(a+b+\cdots+c)'=a'b'\cdots c'$ | $(ab\cdots c)' = a' + b' + \dots + c'$ | $a \cdot a = a$        | a + a = a |

| ab' + ab = a(b)                 | $a \cdot \overline{a} = 0$             | $a + \overline{a} = 1$ |           |

#### **Canonical Forms**

- Every Boolean expression can be expressed in one of these forms

- Sum-of-Products (SOP)

- Sum (OR) of series of products (AND)

- Ex: a'b + bc + acd + c'd + b'd

- Each product sometimes referred to as a "minterm" if SOP in most simplified form

- Product-of-Sums (POS)

- Product (AND) of series of sums (OR)

- Ex: (a+b)(b+c)(a+c'+d)(b+d)

- Each sum sometimes referred to as a "maxterm" if POS in most simplified form

- Can use different methods to simplify down to one of these two forms

- Karnaugh maps (K-maps) are one such method

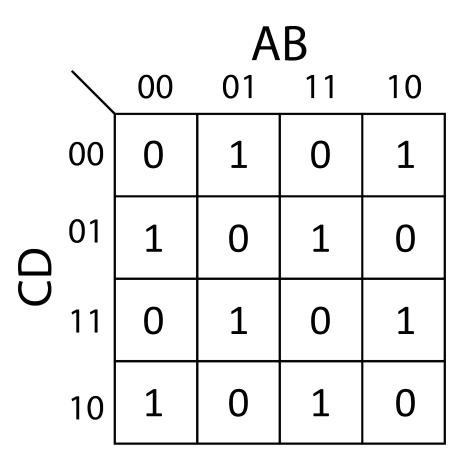

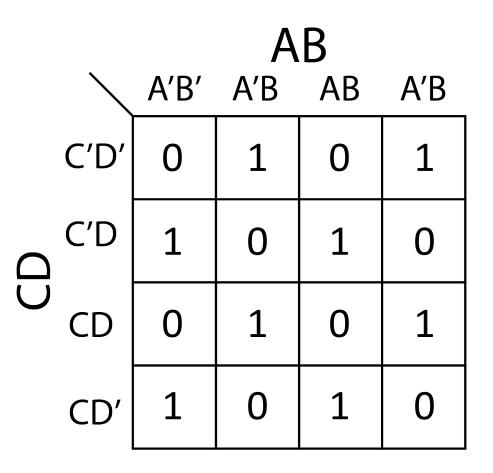

# Karnaugh Maps

- Visualize Truth Table

- Keep "adjacent" terms nearby

- Adjacency means only 1 bit changes between them

- Wikipedia has a decent illustration of adjacency

- <u>https://en.wikipedia.org/wiki/Karnaugh\_map#Karnaugh\_map</u>

- Can use this to find either SOP or POS representation of function

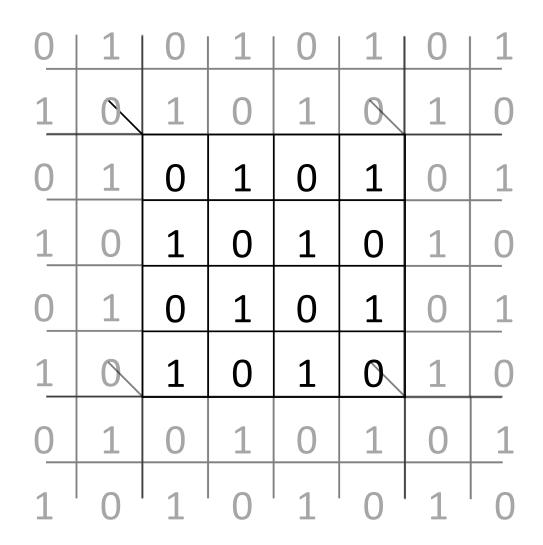

## Karnaugh Maps

- Visualize Truth Table

- Keep "adjacent" terms nearby

- Adjacency means only 1 bit changes between them

- Wikipedia has a decent illustration of adjacency

- <u>https://en.wikipedia.org/wiki/Karnaugh\_map#Karnaugh\_map</u>

- Can use this to find either SOP or POS representation of function

## Gray Code

- Each adjacent term in sequence only differs by 1 bit

- 00, 01, 11, 10

- Mapping truth table by Gray code leads to K-map adjacency

- Each term differs in input by only 1 bit from its neighbors

# Gray Code

- Each adjacent term in sequence only differs by 1 bit

- 00, 01, 11, 10

- Mapping truth table by Gray code leads to K-map adjacency

- Each term differs in input by only 1 bit from its neighbors

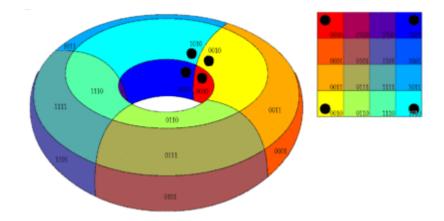

- Can also think of it like the K-map is tiled on all sides

- Edges "wrap around"

- Like a Pac-man stage