EECS 151/251A Spring 2021 Digital Design and Integrated Circuits

Instructors: Wawrzynek

Lecture 9: CMOS1

# Announcements

□ Virtual Front Row for today 2/16: Ellie Wang Khashayar Pirouzmand Thanakul Wattanawong Rajiv Govindjee Jiefeng Chen Keep those questions/comments coming please! (they help determine your class participation points)

# From the Bottom Up

IC processing

MOS transistors

CMOS Circuits

### **Overview of Physical Implementations**

The stuff out of which we make systems.

- Integrated Circuits (ICs)

- Combinational logic circuits, memory elements, analog interfaces.

- Printed Circuits (PC) boards

- substrate for ICs and interconnection, distribution of CLK, Vdd, and GND signals, heat dissipation.

- Power Supplies

- Converts line AC voltage or battery DC voltage to regulated DC low voltage levels.

- Chassis (rack, case, ...)

- holds boards, power supply, fans, provides physical interface to user or other systems.

- Connectors and Cables.

- Peripheral and I/O components.

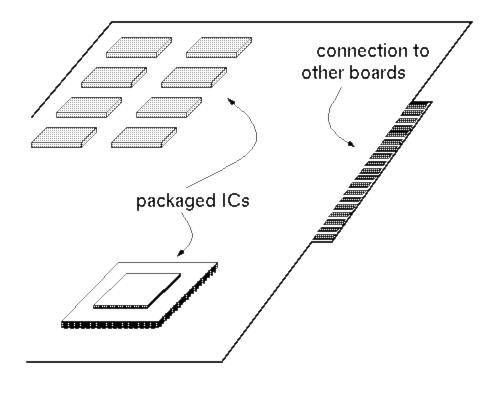

## **Printed Circuit Boards**

Multichip Modules (MCMs)

• Multiple chips directly connected to a substrate. (silicon, ceramic, plastic, fiberglass) with or without chip packages.

fiberglass or ceramic

1-25 conductive layers

~1-20in on a side

IC packages are soldered down.

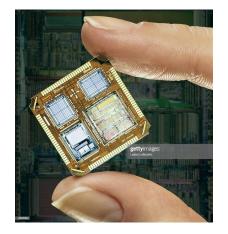

# **Integrated Circuits**

#### Chip in Package

- Primarily Crystalline Silicon

- □ 1mm 25mm on a side

- 100 20B transistors

- □ (25 250M "logic gates")

- 3 10 conductive layers

- 2021 state-of-the-art feature size

5nm = 0.005 x 10<sup>-6</sup> m

- "CMOS" most common complementary metal oxide semiconductor

- Package provides:

- spreading of chip-level signal paths to board-level

- heat dissipation.

- Ceramic or plastic with gold wires.

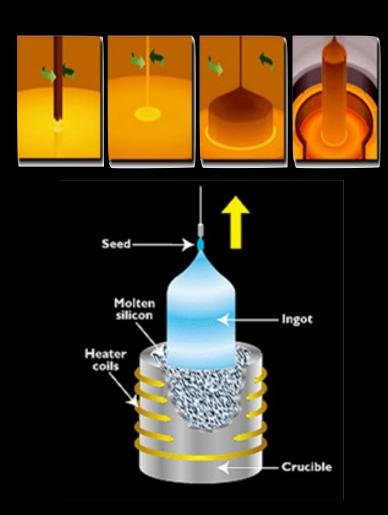

# Chip Fabrication

Silicon "ingots" are grown from a "perfect" crystal seed in a melt, and then purified to "nine nines".

#### Ingots sliced into 450µm thick wafers, using a diamond saw.

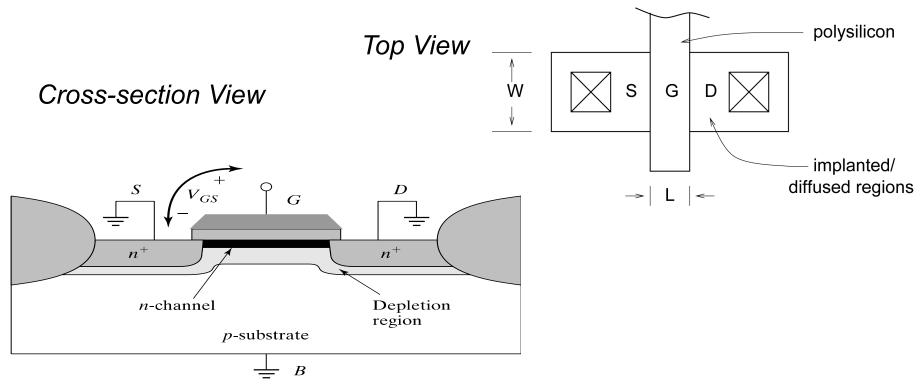

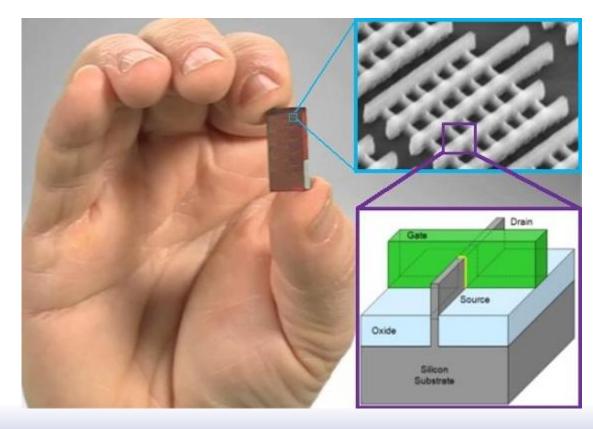

# **CMOS Transistors**

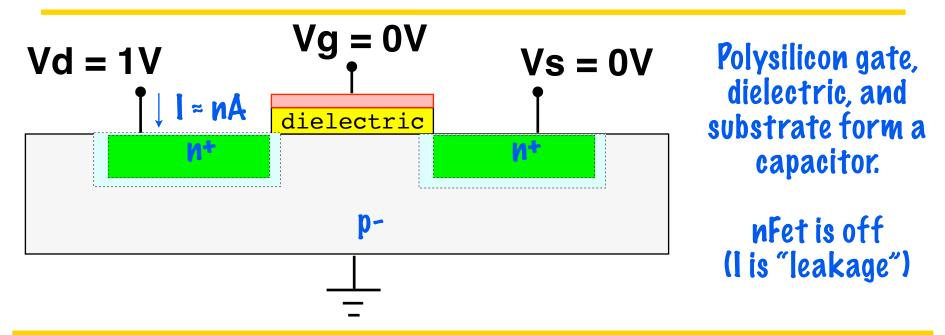

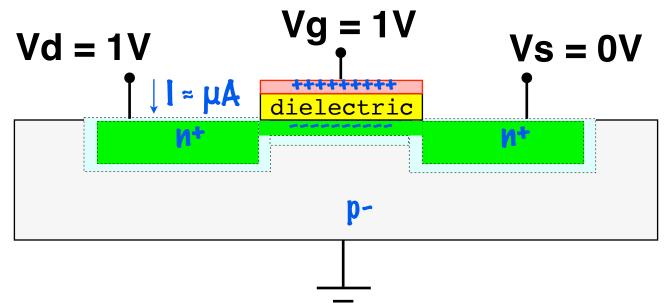

MOSFET (Metal Oxide Semiconductor Field Effect Transistor).

The gate acts like a capacitor. A high voltage on the gate attracts charge into the channel. If a voltage exists between the source and drain a current will flow. In its simplest approximation, the device acts like a switch.

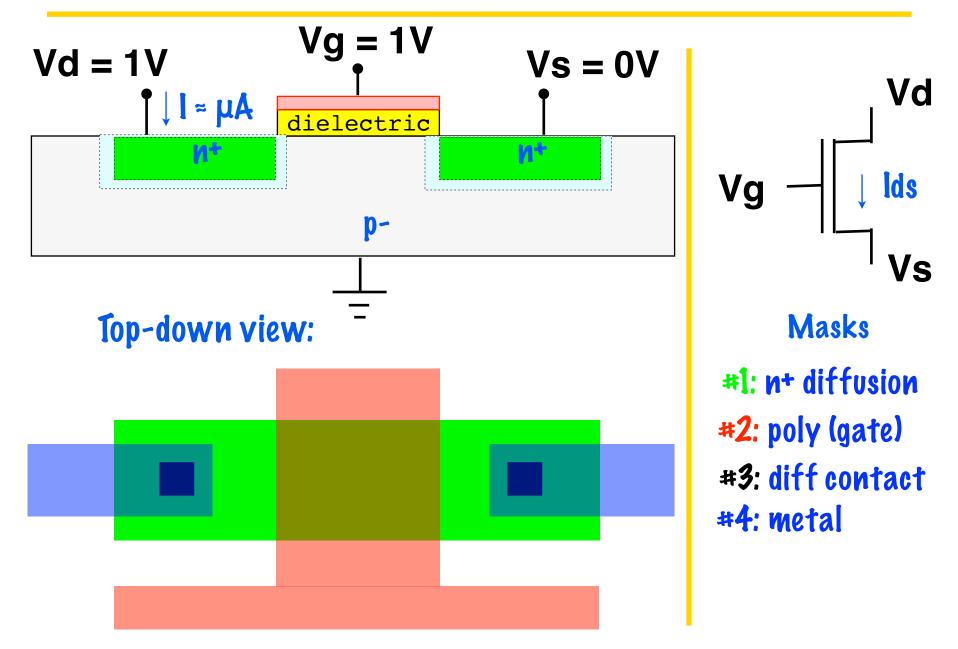

### **An n-channel MOS transistor (planar)**

Vg = 1V, small region near the surface turns from p-type to n-type.

nFet is on.

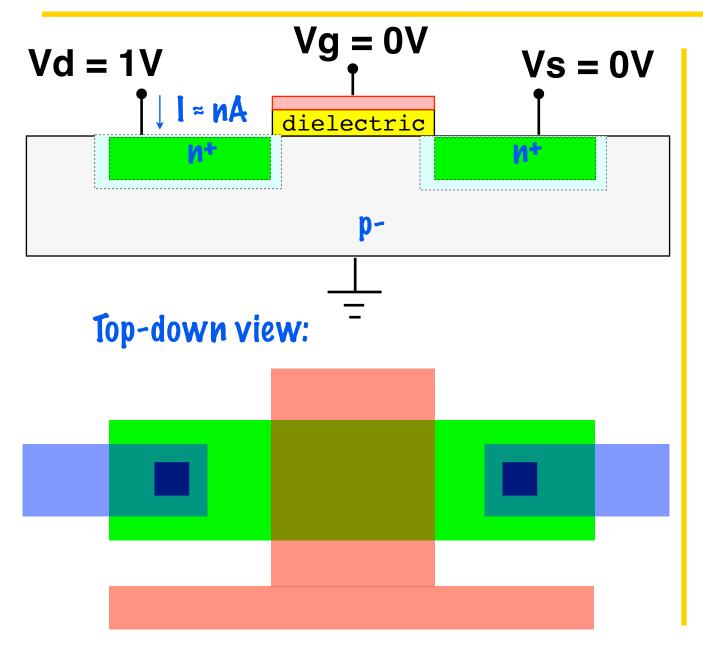

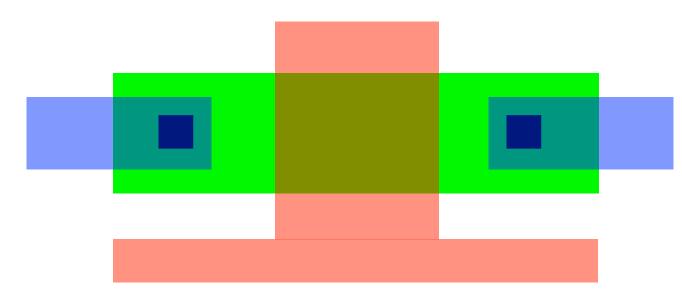

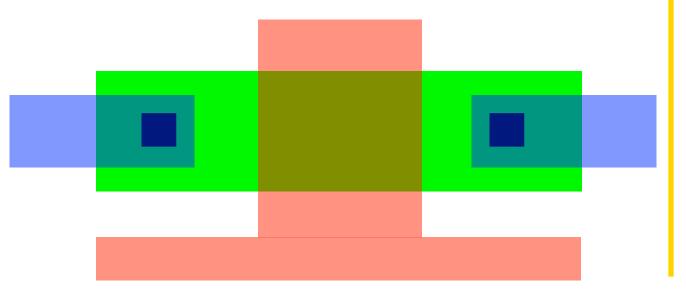

### Mask set for an n-Fet (circa 1986)

Masks #1: n+ diffusion #2: poly (gate) #3: diff contact #4: metal

Layers to do p-Fet not shown. Modern processes have 6 to 10 metal layers (or more) (in 1986: 2).

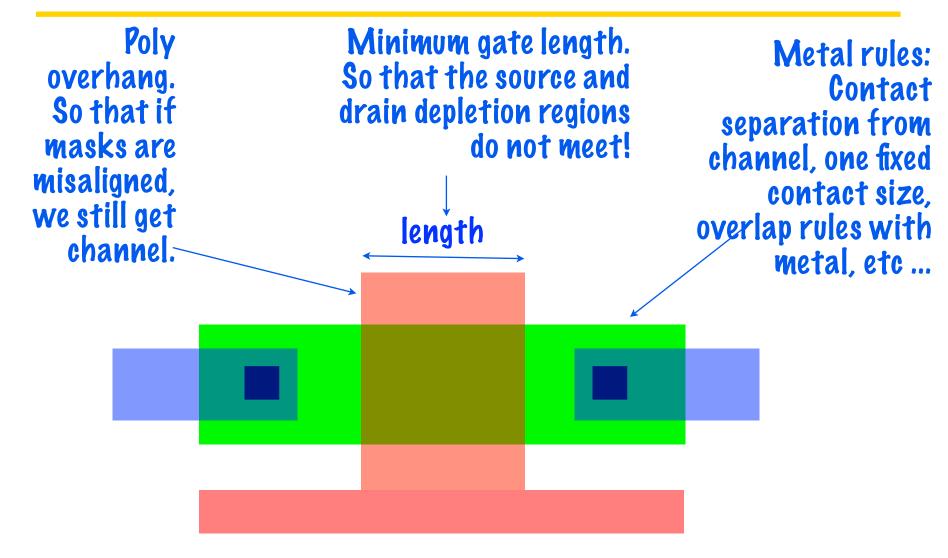

### "Design rules" for masks, 1986 ...

#1: n+ diffusion

#2: poly (gate)

**#3: diff contact #4: metal**

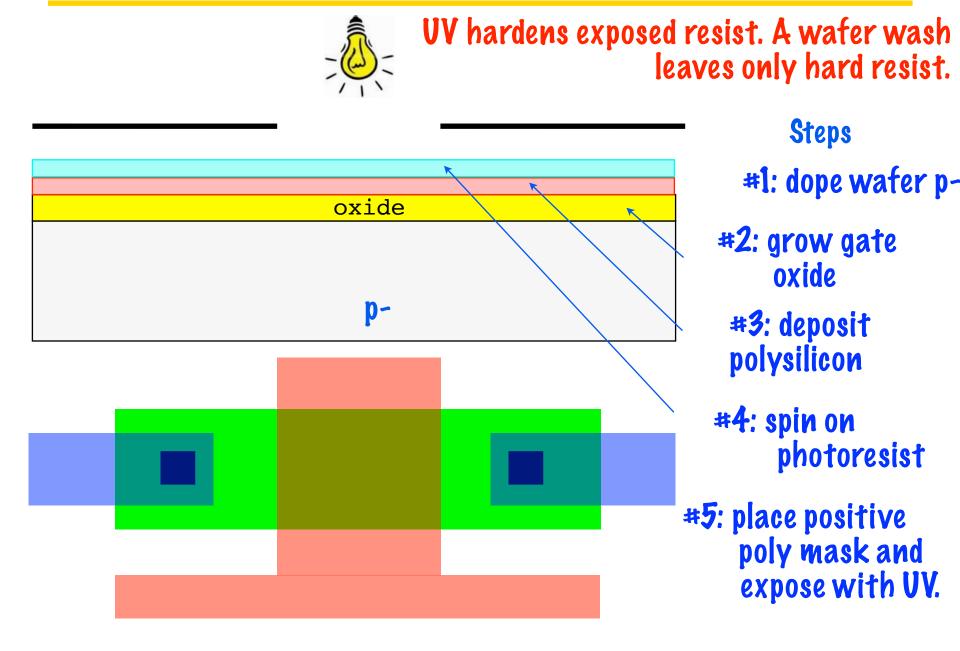

### How a fab uses a mask set to make an IC

### Start with an un-doped wafer ...

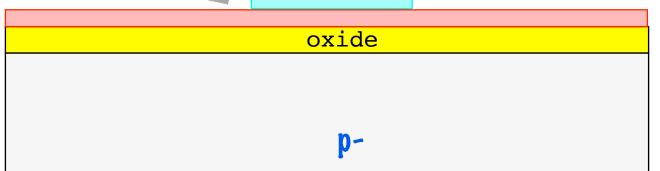

### Wet etch to remove unmasked ...

#### HF acid etches through poly and oxide, but not hardened resist.

After etch and resist removal

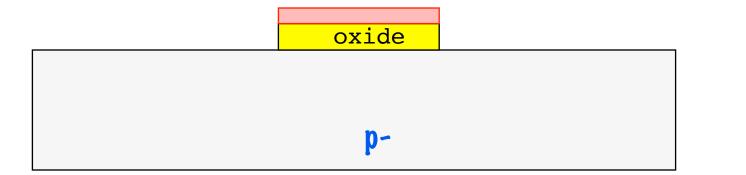

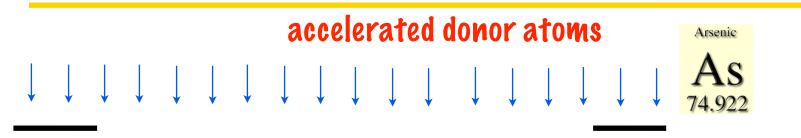

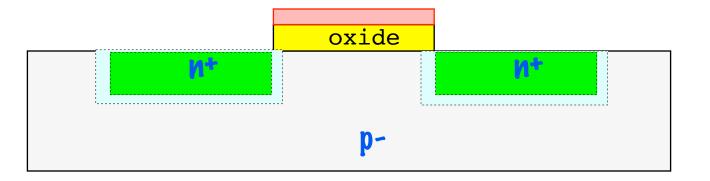

### **Use diffusion mask to implant n-type**

Notice how donor atoms are blocked by gate and do not enter channel.

Thus, the channel is "self-aligned", precise mask alignment is not needed!

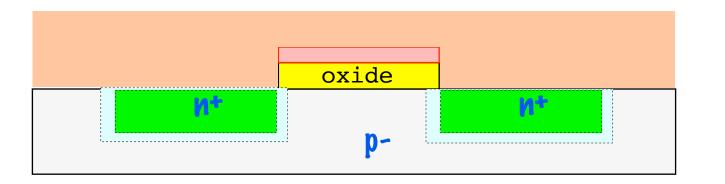

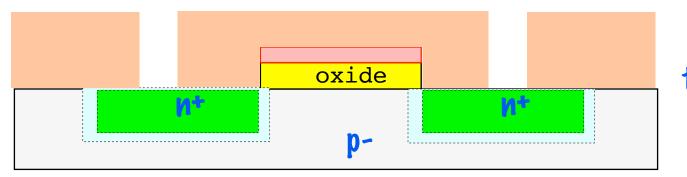

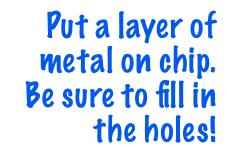

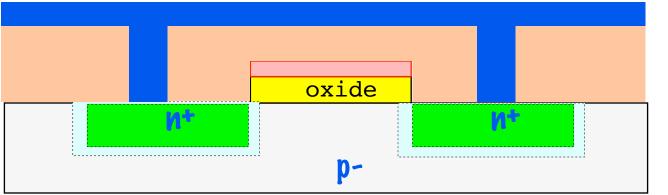

### **Metallization completes device**

#### Grow a thick oxide on top of the wafer.

#### Mask and etch to make contact holes

CS 250 L1: Fab/Design Interface

### Final product ...

Top-down view:

"The planar process"

#### Jean Hoerni, Fairchild Semiconductor 1958

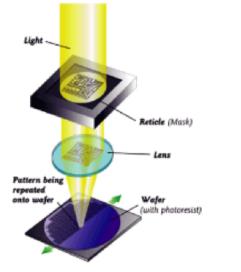

# Lithography

A lithography device [International Society of Optical Engineering]

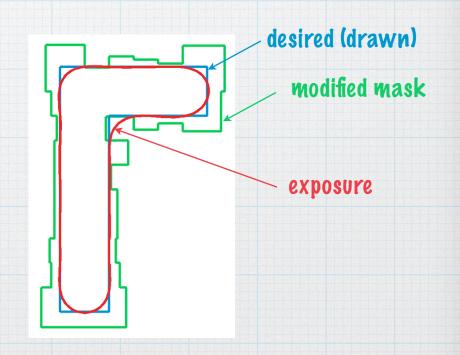

Current state-of-the-art photolithography tools use deep ultraviolet (DUV) light with wavelengths of 248 and 193 nm, which allow minimum feature sizes below 50 nm. Newer processing uses extreme ultraviolet (EUV) with wavelength of 13.5nm.  Optical proximity correction (OPC) is an enhancement technique commonly used to compensate for image errors due to <u>diffraction</u> or process effects.

## Latest Modern Process

| (12) | Unite<br>Hu et al                                                                                                                      | d States<br>Filed:                                                                                                                                                                                                                                                                                           | Patent<br>Oct. 23, 2000 |

|------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| (54) | FINFET TRANSISTOR STRUCTURES<br>HAVING A DOUBLE GATE CHANNEL<br>EXTENDING VERTICALLY FROM A<br>SUBSTRATE AND METHODS OF<br>MANUFACTURE |                                                                                                                                                                                                                                                                                                              |                         |

| (75) | Inventors:                                                                                                                             | Chenming Hu, Alamo; Tsu-Jae King,<br>Fremont; Vivek Subramanian,<br>Redwood City; Leland Chang,<br>Berkeley; Xuejue Huang; Yang-Kyu<br>Choi, both of Albany; Jakub Tadeusz<br>Kedzierski, Hayward; Nick Lindert,<br>Berkeley; Jeffrey Bokor, Oakland, all<br>of CA (US); Wen-Chin Lee, Beaverton,<br>OR (US) |                         |

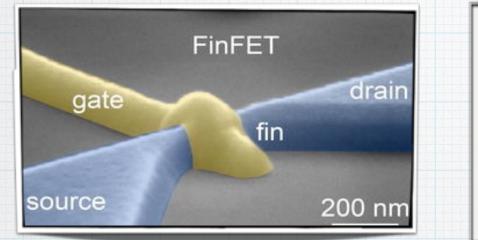

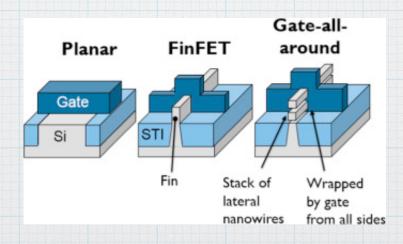

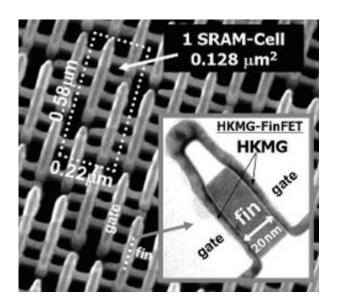

#### Transistor channel is a raised fin. Gate controls channel from sides and top.

# **CMOS Transistors – State-of-the-Art**

# **Sllicon Foundries**

- Separate the designer from the fabricator: Modeled after the printing industry. (Very few authors actually own and run printing presses!)

- Standard geometric design rules are the key: these form the "contract" between the designer and manufacturer.

- Designer sends the layout (in GDS format), foundry manufactures the chip and send back. Designer promises not to violate the design rules. Foundry promises to accurately follow layout.

- A scalable model for the industry:

- ▶ IC fab is expensive and complex

- Amortizes the expense over many designers (batch processing with deep queues help).

- Designers and companies not held back by need to develop and maintain large expensive factories.

- "fabless" semiconductor companies lots of these and very few foundries.

#### Semiconductor device fabrication

MOSFET scaling (process nodes) 10 µm - 1971 6 µm - 1974 3 µm - 1977 1.5 µm - 1981 1 µm - 1984 800 nm - 1987 600 nm - 1990 350 nm - 1993 250 nm - 1996 180 nm - 1999 130 nm - 2001 90 nm - 2003 65 nm - 2005 45 nm - 2007 32 nm - 2009 22 nm - 2012 14 nm - 2014 10 nm - 2016 7 nm - 2018 5 nm - 2020 Future 3 nm - ~2022

2 nm - >2023

State of the art

#### \* From Wikipedia

As of September 2018, mass production of 7 nm devices has begun. The first mainstream 7 nm mobile processor intended for mass market use, the Apple A12 Bionic, was released at their September 2018 event. Although Huawei announced its own 7 nm processor before the Apple A12 Bionic, the Kirin 980 on August 31, 2018, the Apple A12 Bionic was released for public, mass market use to consumers before the Kirin 980. Both chips are manufactured by TSMC. On July 7, 2019, AMD officially launched their Ryzen 3000 series of central processing units, based on the TSMC 7 nm process and Zen 2 microarchitecture.

#### **5**nm

> 7nm

In October 2019, TSMC started sampling 5nm A14 processors for Apple. In December 2019, TSMC announced an average yield of ~80%, with a peak yield per wafer of >90% for their 5nm test chips with a die size of 17.92 mm<sup>2</sup>. In mid 2020 TSMC claimed its (N5) 5nm process offered 1.8x the density of its 7nm N7 process, with 15% speed improvement or 30% lower power consumption; an improved sub-version (N5P) was claimed to improve on N5 with +5% speed or -10% power.<sup>[19]</sup>

On October 13, 2020, Apple announced a new iPhone 12 lineup using the A14, together with the Huawei Mate 40 lineup using the HiSilicon Kirin 9000, which were the first devices to be commercialized on TSMC's 5nm node. Later, on November 10, 2020, Apple also revealed three new Mac models using the Apple M1, another 5nm chip. According to Semianalysis, the A14 processor has a transistor density of 134 million transistors per mm<sup>2</sup>.

#### **3**nm

As of 2019, Intel, Samsung, and TSMC have all announced plans to put a 3 nm semiconductor node into commercial production. Samsung's 3 nm process is based on GAAFET (gate-all-around field-effect transistor) technology, a type of multi-gate MOSFET technology, while TSMC's 3nm process will still use FinFET (fin field-effect transistor) technology,<sup>[1]</sup> despite TSMC developing GAAFET transistors.