# Sampling

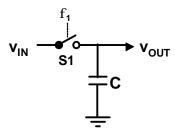

Ideal Sampling

Grab exact value of V<sub>in</sub> when switch opens

**Practical Sampling**

- kT/C noise

- Finite  $R_{sw} \rightarrow limited bandwidth$   $R_{sw} = f(V_{in}) \rightarrow distortion$

- Switch charge injection (EE240)

- · Clock jitter

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 1

# kT/C Noise

$$\frac{k_B T}{C} \le \frac{\Delta^2}{12}$$

$$C \ge 12k_B T \left(\frac{2^B - 1}{V_{FS}}\right)^2$$

In high resolution ADCs kT/C noise usually dominates overall error (power dissipation argument).

| В  | C <sub>min</sub> (V <sub>FS</sub> = 1V) |

|----|-----------------------------------------|

| _  |                                         |

| 8  | 0.003 pF                                |

| 12 | 0.8 pF                                  |

| 14 | 13 pF                                   |

| 16 | 206 pF                                  |

| 20 | 52 800 pF                               |

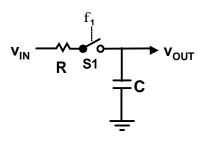

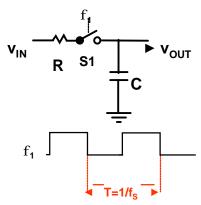

### Acquisition Bandwidth

- The resistance R of switch S1 turns the sampling network into a lowpass filter with risetime = RC = τ

- Assuming V<sub>in</sub> is constant during the sampling period and C is initially discharged (a good idea—why?):

$$v_{out}(t) = v_{in} \left( 1 - e^{-t/t} \right)$$

A/D DSP EECS 247 Lecture 15: Sampling

© 2002 B. Boser 3

### Switch On-Resistance

$$v_{in} - v_{out} \left( t = \frac{1}{2f_s} \right) << \Delta$$

$$v_{in} e^{-\frac{1}{2}f_s t} << \Delta$$

Worst Case:  $v_{in} = V_{FS}$

$$t << -\frac{T}{2} \frac{1}{\ln(2^B - 1)}$$

$$R << -\frac{1}{2f_s C} \frac{1}{\ln(2^B - 1)}$$

### Example:

$$B=14, \quad C=13 pF, \quad f_s=100 MHz$$

$$T/\tau >> 19.4, \quad R << 40 \Omega$$

A/D DSP

EECS 247 Lecture 15: Sampling

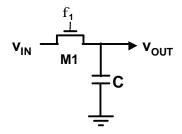

### Switch On-Resistance

$$\begin{split} I_{D(triode)} &= \mathbf{m} C_{ox} \frac{W}{L} \bigg( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \bigg) V_{DS} \\ &\frac{1}{R_{ON}} \cong \frac{dI_{D(triode)}}{dV_{DS}} \bigg|_{V_{DS} \to 0} \\ &= \frac{1}{\mathbf{m} C_{ox} \frac{W}{L} \big( V_{GS} - V_{TH} \big)} \\ &= \frac{1}{\mathbf{m} C_{ox} \frac{W}{L} \big( V_{DD} - V_{TH} - v_{in} \big)} \\ &= \frac{1}{R_o} \frac{1}{1 - \frac{v_{in}}{V_{DD} - V_{TH}}} \quad \text{ with } \quad R_o = \frac{1}{\mathbf{m} C_{ox} \frac{W}{L} \big( V_{DD} - V_{TH} \big)} \\ R_{ON} &= R_o \Big( 1 - \frac{v_{in}}{V_{DD} - V_{TH}} \Big) \end{split}$$

A/D DSP

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 5

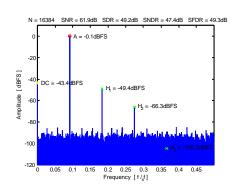

# **Sampling Distortion**

$$v_{out} = v_{in} \left( 1 - e^{-\frac{T}{2t} \frac{1}{1 - \frac{V_{in}}{V_{DD} - V_{TH}}}} \right)$$

$$\begin{split} T/\tau &= 10 \\ V_{DD} - V_{TH} &= 2V \qquad V_{FS} = 1V \end{split}$$

A/D DSP

EECS 247 Lecture 15: Sampling

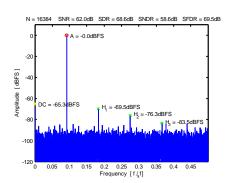

# Sampling Distortion

- SFDR is very sensitive to sampling distortion

- · Solutions:

- Overdesign switches

- → increased switch charge injection

- Complementary switch

- Maximize V<sub>DD</sub>/V<sub>FS</sub>

- → increased noise

- Constant V<sub>GS</sub> ? f(V<sub>in</sub>)

$$T/\tau = 20$$

$V_{DD} - V_{TH} = 2V$   $V_{FS} = 1V$

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 7

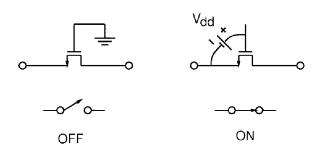

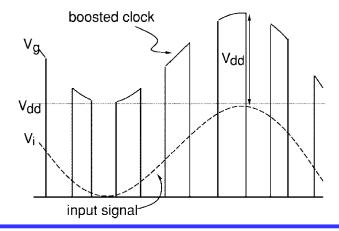

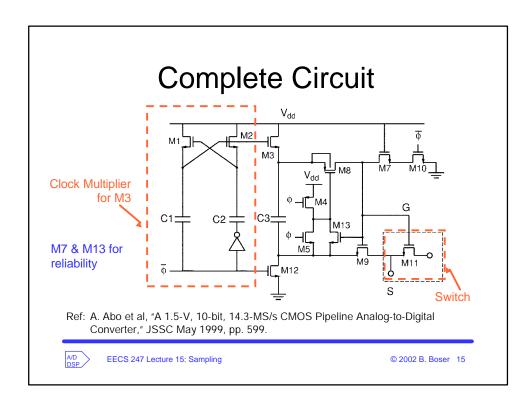

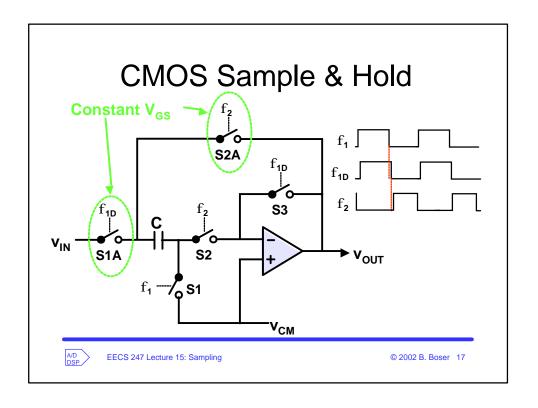

# Constant V<sub>GS</sub> Sampling

- Switch overdrive voltage is independent of signal

- Error from finite R<sub>ON</sub> is linear (to first order)

A/D DSP

EECS 247 Lecture 15: Sampling

A/D DSP

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 9

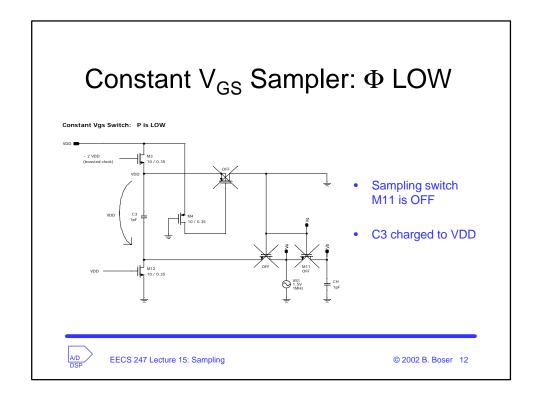

# Constant V<sub>GS</sub> Sampling Circuit

A/D DSP

EECS 247 Lecture 15: Sampling

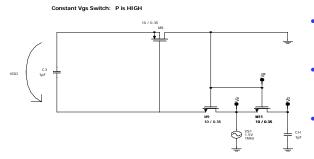

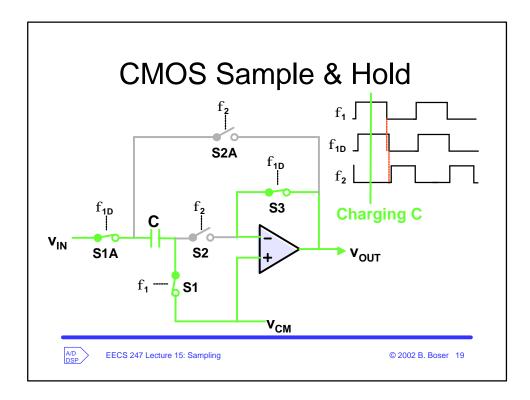

# Constant $V_{GS}$ Sampler: $\Phi$ HIGH

- C3 previously charged to VDD

- M8 & M9 are on:C3 across G-S of M11

- M11 on with constant VGS = VDD

A/D DSP

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 13

# Constant V<sub>GS</sub> Sampling Second of the secon

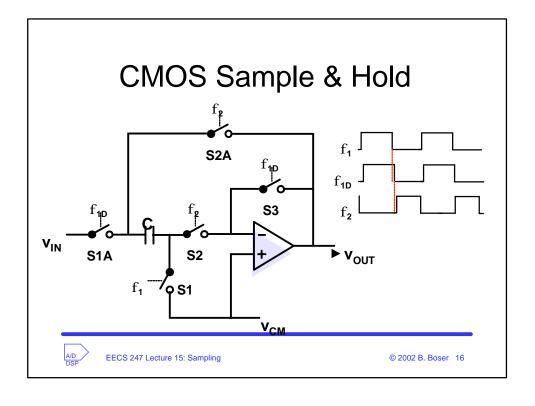

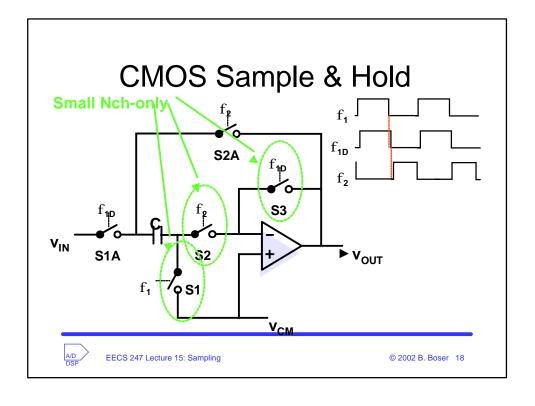

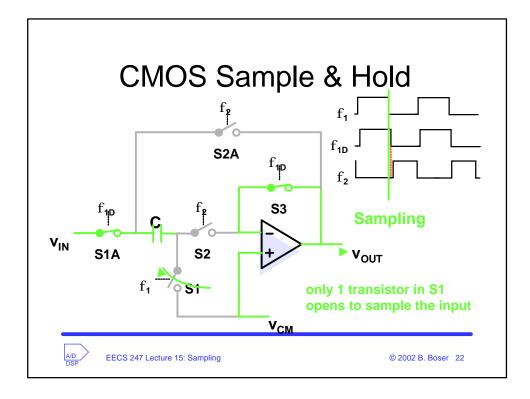

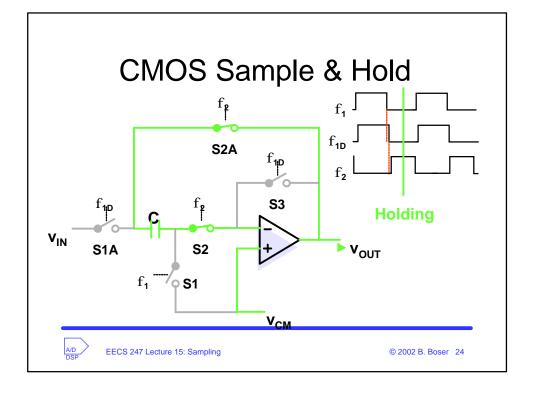

# CMOS Sample & Hold

- S1 is an n-channel MOSFET

- S1 provides as much of the sampling path resistance as possible (R=R<sub>S1A</sub>+R<sub>S1</sub>)

- S1A is a wide (much lower resistance than S1) constant V<sub>GS</sub> switch

- If S1A's resistance is negligible, aperture delay depends only on S1 resistance

- S1 resistance is independent of  $v_{IN}$ ; hence, aperture delay is independent of  $v_{IN}$

### Charge Injection

- At the instant of sampling, some of the charge stored in sampling switch S1 is dumped onto C

- This unwanted charge is called "charge injection"

- The circuit on slide 15.2 has charge injection that varies in a wildly nonlinear fashion with v<sub>IN</sub>

- With the CMOS Sampling Circuit, charge injection comes only from S1 and is first-order independent of v<sub>IN</sub>

- Only a dc offset is added to the input signal

- This dc offset can be removed with a differential architecture

A/D DSP EECS 247 Lecture 15: Sampling

# **CMOS Sample & Hold**

- During  $\phi_2$ , the opamp buffers the sampling capacitor for loads that need it

- The hold topology is shown on the following slide...

A/D DSP EECS 247 Lecture 15: Sampling

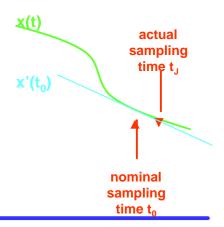

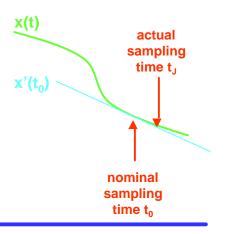

### **Jitter**

- All of the preceding analyses assume that sampling impulses are spaced evenly in time

- In the real world, separation of sampling impulses has some distribution around the nominal value T

- The variability in T is called jitter

A/D DSP EECS 247 Lecture 15: Sampling

© 2002 B. Boser 25

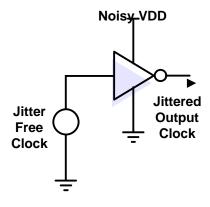

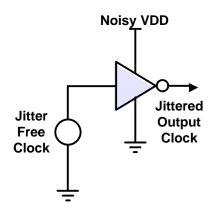

### **Jitter**

- The dominant cause of clock jitter in most chips is power supply noise produced by unrelated activity in other parts of the chip

- The inverter symbol represents a chain of gates in the sampling clock path

A/D

EECS 247 Lecture 15: Sampling

### **Jitter**

- Let's assume the inverter delay is 100psec, and that the delay varies by 20% per volt change in VDD (20psec/V)

- 200mV of power supply noise becomes 4psec of clock jitter

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 27

### **Jitter**

- Sampling jitter adds an error voltage proportional to the product of (t<sub>J</sub>-t<sub>0</sub>) and the derivative of the input signal at the sampling instant

- Jitter doesn't matter when sampling dc signals

EECS 247 Lecture 15: Sampling

### **Jitter**

• The error voltage is

$$e = x'(t_0)(t_J - t_0)$$

A/D DSP

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 29

# Jitter Example

### Sinusoidal input

Amplitude: A

Frequency:  $f_x$ Jitter: 2t

$$x(t) = A\sin(2\mathbf{p}f_x t)$$

$$x'(t) = 2\mathbf{p}fA\cos(2\mathbf{p}f_x t)$$

$$|x'(t)| \le 2\mathbf{p}fA$$

$$|e(t)| \le |x'(t)| ?t$$

### Worst case

$$A = A_{FS}$$

$$f_x = \frac{f_s}{2}$$

$$|e(t)| \ll \frac{\Delta}{2} \cong \frac{A_{FS}}{2^{B+1}}$$

$$?t << \frac{1}{2^B \mathbf{p} f_a}$$

| R  | f        | Δt << than   |

|----|----------|--------------|

|    | 's       | Δι << triair |

| 16 | 10 MHz   | 0.5 ps       |

| 12 | 100 MHz  | 0.8 ps       |

| 8  | 1000 MHz | 1.2 ps       |

### The Jitter Law

- The worst case looks pretty stringent ... what about the "average"?

- Let's calculate the mean squared jitter error (variance)

- If we're sampling a sinusoidal signal

$$x(t) = A\sin(2\pi f_x t),$$

then

$- x'(t) = 2\pi f_x A\cos(2\pi f_x t)$

$$- E{[x'(t)]^2} = 2\pi^2 f_x^2 A^2$$

- If jitter is uniformly distributed from  $-\tau/2$  to  $+\tau/2$

- $E\{(t_1-t_0)^2\} = \tau^2/12$

EECS 247 Lecture 15: Sampling

© 2002 B. Boser 31

### The Jitter Law

- If x'(t) and the jitter are independent

- $E\{[x'(t)(t_J-t_0)]^2\} = E\{[x'(t)]^2\} E\{(t_J-t_0)^2\}$

- Hence, the jitter error power is

$$E\{e^2\} = p^2 f_x^2 A^2 t^2 / 6$$

If the jitter is uncorrelated from sample to sample, this "jitter noise" is white

A/D DSP

EECS 247 Lecture 15: Sampling

### The Jitter Law

$$DR_{\text{jitter}} = \frac{A^{2}/2}{\mathbf{p}^{2} f_{x}^{2} A^{2} \mathbf{t}^{2}/6}$$

$$= \frac{3}{\mathbf{p}^{2} f_{x}^{2} \mathbf{t}^{2}}$$

$$= -20 \log_{10}(f_{x} \mathbf{t}) - 5.172 \text{dB}$$

| f <sub>x</sub> | τ      | DR <sub>jitter</sub> | ENOB |

|----------------|--------|----------------------|------|

| 1 MHz          | 1 ns   | 55 dB                | 8.8  |

| 1 MHz          | 2 ps   | 109 dB               | 17.8 |

| 100 MHz        | 0.4 ps | 83 dB                | 13.5 |

| 1000 MHz       | 0.5 ps | 61 dB                | 9.8  |

A/D DSP EECS 247 Lecture 15: Sampling

© 2002 B. Boser 33

### The Jitter Law

- The Jitter Law must be respected whenever you require highresolution conversion of high frequency signals

- Sampling a 1MHz signal with 1nsec of peak-to-peak jitter yields a dynamic range of only 55dB

- In practice, jitter is usually controlled to add negligible to the total converter error (i.e. thermal and quantization noise)

- This translates into the jitter being ~10dB below other noise sources

- For 16 Bit conversion of 1MHz signals, a –109dB jitter DR limit requires < 2 psec peak-to-peak jitter</li>

A/D DSP

EECS 247 Lecture 15: Sampling

### The Jitter Law

- Clock jitter in the single-digit picosecond range doesn't just happen

- Separate supplies

- Separate analog and digital clocks

- Short inverter chains between clock and sampling switch

- Few, if any, other analog-to-digital conversion nonidealities have the same symptoms as sampling jitter:

- RMS noise proportional to input frequency

- RMS noise proportional to input amplitude

- So, if sampling clock jitter is limiting your dynamic range, it's easy to tell, but difficult to fix

- Very difficult to fix in silicon without all-layer mask revisions

A/D DSP EECS 247 Lecture 15: Sampling