! This class has been made inactive. No posts will be allowed until an instructor reactivates the class.

| ■ note @2127 ⓒ ★ 272 views                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Past Exams] 2020                                                                                                                                                                                                                                                                                                                                                                                                   |

| You can find the past exams here: https://cs61c.org/sp22/resources/exams/                                                                                                                                                                                                                                                                                                                                           |

| Summer 2020 midterm walkthrough                                                                                                                                                                                                                                                                                                                                                                                     |

| When posting questions, please reference the semester, exam, and question in this format so it's easier for students<br>and staff to search for similar questions:<br>Semester-Exam-Question Number<br>For example: SP20-Final-Q1, or FA20-MT2-Q3                                                                                                                                                                   |

| FA20-MT1 Video Walk Through Links<br>Bit Manipulations Walkthrough<br>Slip Walkthrough                                                                                                                                                                                                                                                                                                                              |

| exam exam/final                                                                                                                                                                                                                                                                                                                                                                                                     |

| good note     0     Updated 5 months ago by Jerry Xu and Peyrin Kao                                                                                                                                                                                                                                                                                                                                                 |

| followup discussions, for lingering questions and comments                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>Resolved Unresolved @2127_f1 (c)</li> <li>This was marked a duplicate to the question/note above by Peyrin Kao 5 months ago</li> <li>Anonymous Comp 5 months ago</li> <li>[sp20-final] questions</li> <li>There's no solution for q5a.iii. Does this answer make sense? I'm not really sure what does the pointer in the instruction "if the pointer is currently pointing at a 0" referring to</li> </ul> |

| (memory_grid[x][y] == 0 && dir==1)? dir=0 : dir=1                                                                                                                                                                                                                                                                                                                                                                   |

| helpful! 0                                                                                                                                                                                                                                                                                                                                                                                                          |

| Adelson Chua 5 months ago<br>Almost correct.<br>You only change dir from forward (1) to backward (0), and not vice versa.<br>good comment 0                                                                                                                                                                                                                                                                         |

| Anonymous Comp 5 months ago<br>How to write that logic in one line? We can't really have two ?: groups right?<br>helpful! 0                                                                                                                                                                                                                                                                                         |

| Adelson Chua 5 months ago                                                                                                                                                                                                                                                                                                                                                                                           |

```

Sp20 Final Q2

uint32_t arr[N];

for (int j=0; j < 30; j++) {

for (int i=0; i < N; i += 1) {

process(arr[i]);

}

}</pre>

```

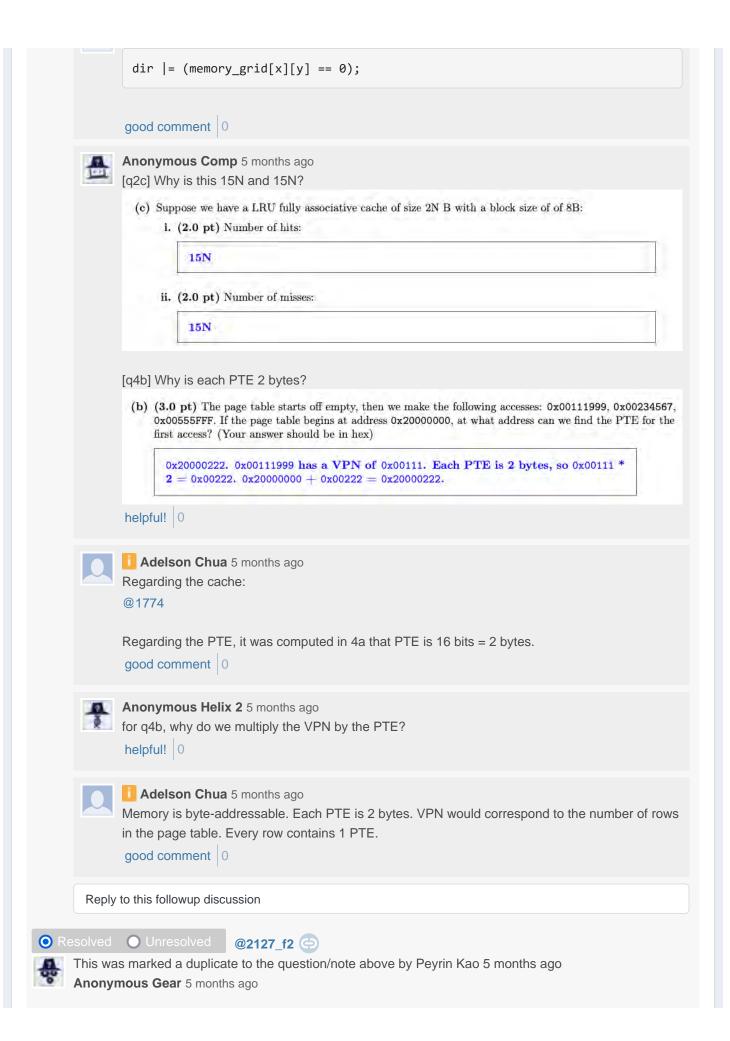

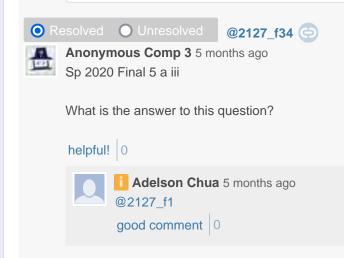

What are the number of hits + what type of locality are the following caches taking advantage of? All caches start out empty:

1. LRU fully associative cache of size 4N B and a block size of 4B

2. LRU fully associative cache of size 2N B and a block size of 4B

3. LRU fully associative cache of size 2N B and a block size of 8B

I would like to confirm that my thinking process is correct for the first two caches and am also confused on the answer for the third cache.

Block size == line size, which means that there is one 32-bit integer (4B) stored in each line of the first and second caches. Because there are N lines in the first cache (4N / 4), we have N integers that are able to be stored. Since the inner for loop repeats 30 times, we only need to store a total of N integers which can be repeatedly accessed each of the 30 times. So, for the first cache, there are N misses due to the first N compulsory misses and 29N hits. It takes advantage of temporal locality due to the LRU policy. For the second cache, because there are only half the number of cache lines available, we would continually need to replace elements in the cache based on LRU, which means we have 0 hits and 30N misses. This also means the second cache doesn't take advantage of any type of locality.

But for the third cache, I thought that each line could store 2 integers, which makes up for the cache having only half the number of lines as the first cache. I thought this meant that we would also only have N misses, but the answer says there are 15N misses and 15N hits.

Could someone explain if my thinking for the first and second caches are correct, and why the third one is as is? Thank you!

helpful! 0

# **Adelson Chua** 5 months ago

The explanation for 1st cache architecture is correct. The cache fits the whole array, 1st of the 30 iterations are compulsory misses, next 29 are hits.

The explanation for 2nd cache is also correct. The cache cannot fit the whole array, there will be replacements when you access the 2nd half of the array, thus there will be no hits afterward. For 3rd cache, for every miss, you get one hit (because the block size is 2 ints, 1 int for the one you missed, and the next int after that). So that's always 50% miss 50% hit.

good comment 0

# ÷

# Anonymous Gear 5 months ago

I understand now that there would be a 50-50 miss/hit, but wouldn't this happen only for the 1st of the 30 iterations leading to N/2 misses? Because there wouldn't need to be any replacements given that the cache can hold all N elements?

|                                                                    | helpful! 0                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    | Adelson Chua 5 months ago         Cache size is 2N though. So it can only fit half of the array. There will be replacements, just like in cache 2.         good comment       0                                                                                                                                                                       |

| 40                                                                 | Anonymous Gear 5 months ago<br>Ohh right, got it! Thank you so much!<br>helpful! 0                                                                                                                                                                                                                                                                    |

| <b>A</b>                                                           | Anonymous Comp 3 5 months ago<br>What is Quasi-balistic locality?<br>helpful!                                                                                                                                                                                                                                                                         |

|                                                                    | Adelson Chua 5 months agoNot sure. It's not covered in the lecture anyway. Just an added choice.good comment0                                                                                                                                                                                                                                         |

| Reply                                                              | r to this followup discussion                                                                                                                                                                                                                                                                                                                         |

| Resolved                                                           | O Unresolved @2127_f3 👄                                                                                                                                                                                                                                                                                                                               |

| _                                                                  | mous Scale 5 months ago                                                                                                                                                                                                                                                                                                                               |

| 1000                                                               | inal-S1-Q1A question                                                                                                                                                                                                                                                                                                                                  |

| Section                                                            | on 1: Quest Clobber                                                                                                                                                                                                                                                                                                                                   |

| 1: Qu                                                              | est Clobber (10 pts)                                                                                                                                                                                                                                                                                                                                  |

| are neg<br>choosir<br><b>Soluti</b><br>Answer<br>and ha<br>to posi | r: 6DDDDD. For now, let's pretend that 0 is negative; that way, we want exactly half the numbers to be negative,<br>If to be positive, and all numbers are positive or negative. If we do that, then we want the cutoff from negative<br>tive to be right in the middle of all possible numbers; this is between the numbers 6DDDDD and 700000. Our 0 |

|                                                                    | be the number right before this cutoff, and is thus 6DDDDD.<br>ts: Different bases (all even, so the above process works), and different number of digits.                                                                                                                                                                                            |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                       |

| would b<br>6DDDD<br>biased                                         | stand that the bias would be -(14^(6-1) - 1) -(DDDDD) based on the equation and the concept that 0 be in between the cutoff of negative and positive numbers. However, I do not understand why 0D is 0's biased representation when on discussion 01 on part 3 0 for an 8 bit-biased notation with -127 is 127.                                       |

| helpful                                                            | ·   0                                                                                                                                                                                                                                                                                                                                                 |

|                                                                    | Adelson Chua 5 months agoI do not know what you are trying to connect between this exam question and the discussion.This exam question is in 6-digit base-14. The discussion is in 8-bit binary.good comment0                                                                                                                                         |

| ₽                                                                  | Anonymous Scale 5 months ago<br>Sorry for the confusion. I am just confused on where did the 6 came from in representation of 0 in                                                                                                                                                                                                                    |

I also don't understand why we need to mod by b->size or the final answer...

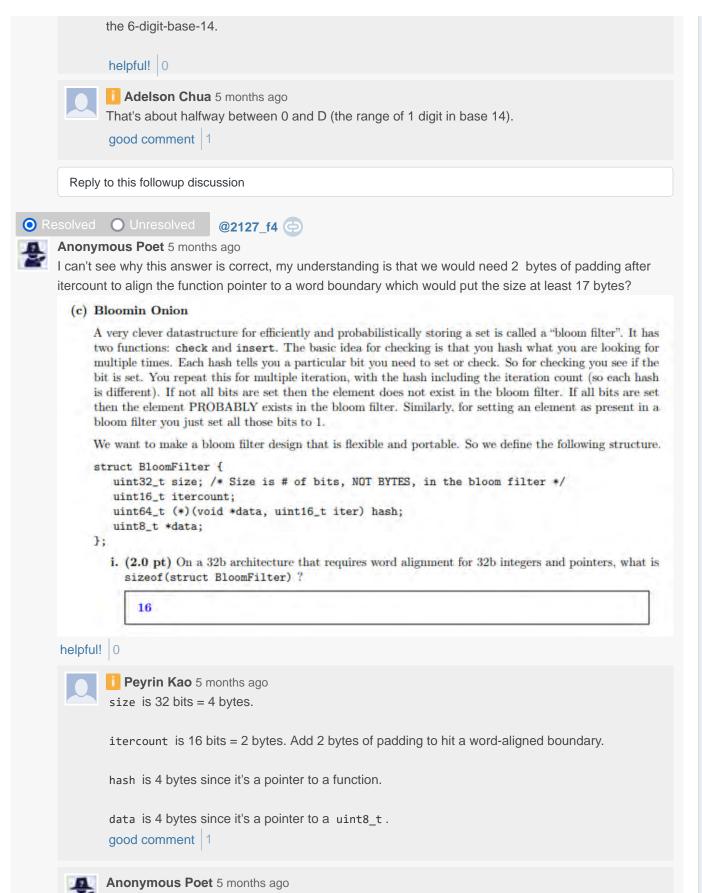

#### (c) Bloomin Onion

A very clever datastructure for efficiently and probabilistically storing a set is called a "bloom filter". It has

two functions: check and insert. The basic idea for checking is that you hash what you are looking for multiple times. Each hash tells you a particular bit you need to set or check. So for checking you see if the bit is set. You repeat this for multiple iteration, with the hash including the iteration count (so each hash is different). If not all bits are set then the element does not exist in the bloom filter. If all bits are set then the element PROBABLY exists in the bloom filter. Similarly, for setting an element as present in a bloom filter you just set all those bits to 1.

We want to make a bloom filter design that is flexible and portable. So we define the following structure.

```

struct BloomFilter {

uint32_t size; /* Size is # of bits, NOT BYTES, in the bloom filter */

uint16_t itercount;

uint64_t (*)(void *data, uint16_t iter) hash;

uint8_t *data;

};

```

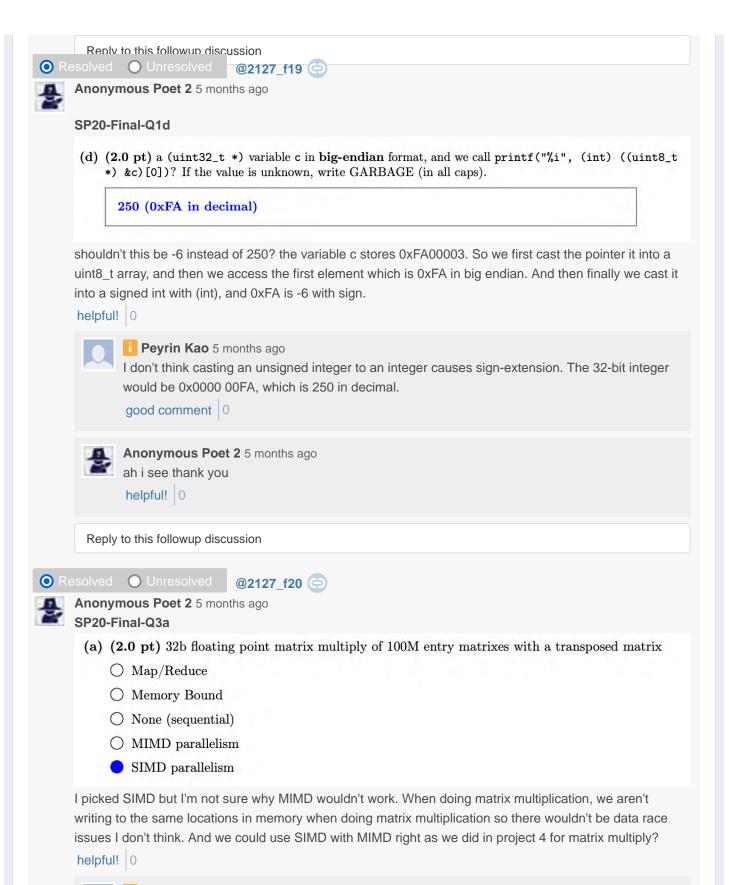

i. (2.0 pt) On a 32b architecture that requires word alignment for 32b integers and pointers, what is sizeof(struct BloomFilter) ?

```

ii. And now we have the insert function... For this we need to set the appropriate bit for each iteration.

```

```

void insert(struct BloomFilter *b, void *element){

uint64_t bitnum; /* which bit we need to set */

int i;

for(i = 0; i < (CODE INPUT 1); ++i){

bitnum = (CODE INPUT 2);

b->data[bitnum >> 3] = (CODE INPUT 3);

}

}

```

```

A. (1.0 pt) (CODE INPUT 1):

```

b->itercount

16

B. (3.0 pt) (CODE INPUT 2):

b->hash(element, (uint16\_t) i) % b->size

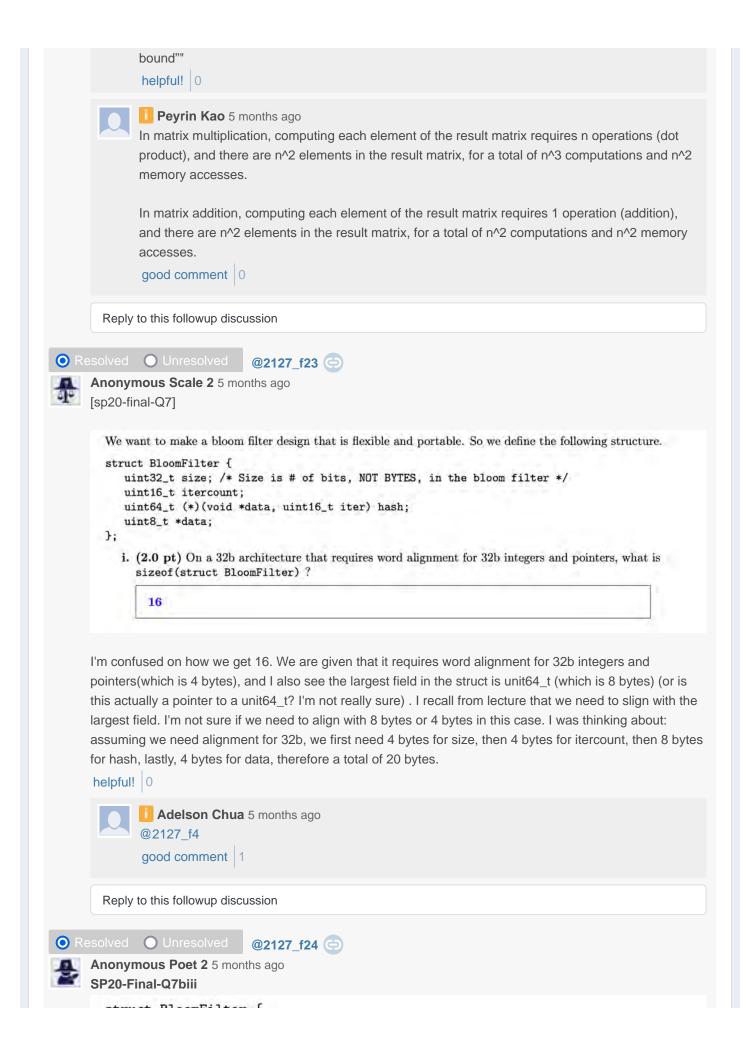

C. (3.0 pt) (CODE INPUT 3):

@2127 f5 🖨

b->data[bitnum >> 3] | (1 << (bitnum & 0x7)) (or equivalent)

helpful! 0

Peyrin Kao 5 months ago

The hash outputs a uint64\_t, but the data array only has b->size elements, so we need to use the mod operator to convert the hash output into one of the elements in the array of hashes.

data is an array of bytes (8 bits each), and we want to set a specific bit given by the index bitnum. bitnum >> 3 gives all but the lowest 3 bits of the index, which are used to choose what byte we want to set. bitnum & 0x7 gives us only the lowest 3 bits of the index, which are used to choose which bit within the byte we want to set.

good comment 0

Reply to this followup discussion

A

Anonymous Atom 5 months ago Solutions CODE INPUT 1: \*\*head

Resolved O Unresolved

CODE INPUT 2: 1 << 20 - 1 CODE INPUT 3: \*head CODE INPUT 4: \*head CODE INPUT 5: & CODE INPUT 6: ~(1 << 20 - 1) CODE INPUT 7: &head [HEX INPUT HERE]: 12400000

In order for this code to work, we need at least one contiguous group of size bits, starting at an aligned address. We don't have any control over our initial head position, so we need to add an extra few bytes to ensure our buffer contains such a block. The specified amount makes it so that exactly one such buffer is guaranteed to exist; we then shift our return value to exactly the right spot. We need to send in a double pointer so that we modify a pointer outside the program; if we had a single pointer, the change we make to head in the function would not appear outside the function, because C is pass-by-value.

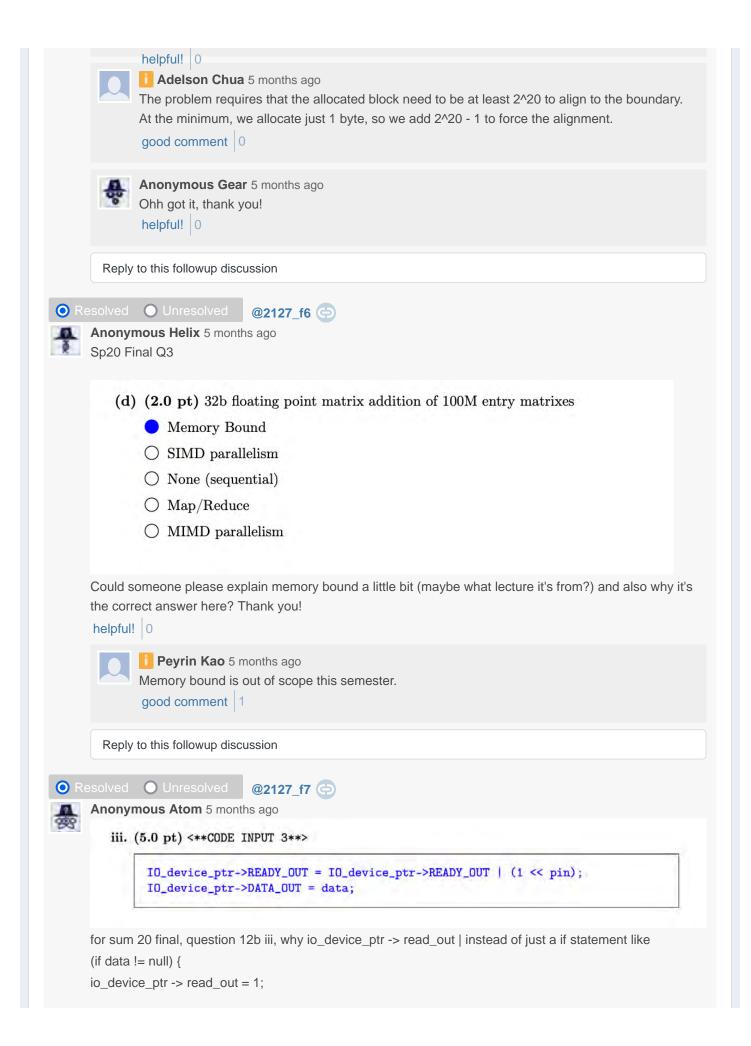

For fa20 final question 1B, how is 1 << 20 -1 change to a memory address aligned to 2 20-byte boundaries?

helpful! 0

Anonymous Atom 5 months ago also how we get 12400000?

helpful! 0

Adelson Chua 5 months ago

$1 \ll 20$  is basically  $2^20$ .

There's a -1 to ensure a malloc'd size of 1 byte will still get 2^20 allocated.

0x12400000 might have been a typo. I believe it should be 0x12300000

# good comment 0

Anonymous Atom 5 months ago then how we get 0x12300000? helpful! 0

Adelson Chua 5 months ago The return value is calculated as follows: 0x12345678 & ~(1 << 20 -1) // this is 1 followed by 20 zeros minus 1 0x12345678 & ~(0x0007FFFF) // which is 19 1s 0x12345678 & (0xFFF80000) // bitwise negate 0x12300000 // bitwise AND

It might help to review boolean logic. good comment 0

Anonymous Gear 5 months ago

When it says "we want to malloc the *fewest extra bytes possible*", why is the fewest extra bytes  $2^{20}$  byte boundaries? I thought it meant we would need to offset a certain amount to fill the boundary given the size passed in.

```

} else {

io_device_ptr -> read_out = 0;

}

?

helpful! 0

Adelson Chua 5 months ago

Your proposed if statement block will only work for pin = 0.

... actually maybe not, because I don't know why you are check for data != null. What is data?

The (1<<pin) is important since the READY_OUT is a collection of bits corresponding to different

pin numbers. See the definition of this in the main problem statement.

good comment 0

Reply to this followup discussion

• Resolved • Unresolved

@2127_f8 👄

Anonymous Mouse 5 months ago

Can you explain how all these multiple choice questions were selected. I literally got a 0 on this whole

question which is statistically impressive but also means I really had 0 clue what was going on. There is no

explanations for the solutions.

(b) (2.0 pt)

int * shifted = other + shift;

int dot_product = 0;

#pragma omp parallel for reduction(+:dot_product)

for (int i = 0; i < n; i++) {

#pragma omp critical

dot_product += shifted[i] * original[i];

7

result[shift] = dot_product;

How will this code behave?

Always Correct, slower than serial

□ Always Correct, faster than serial

□ Sometimes Incorrect

(c) (2.0 pt)

int * shifted = other + shift;

int dps[4] = {0,0,0,0};

#pragma omp parallel

£

#pragma omp for

for (int i = 0; i < n; i++) {

int id = omp_get_thread_num();

dps[id] += shifted[i] * original(i];

}

}

result[shift] = dps[0] + dps[1] + dps[2] + dps[3];

How will this code behave?

Always Correct, faster than serial

Always Correct, slower than serial

```

#### □ Sometimes Incorrect

The intended answer was that the code ends up being slower. Note that the due to false sharing and MOESI, elements of dps in the same cache block will have to continuously kick each other out, thus slowing down the code to slower than serial. Note that we specify the size of a cache block as 32 B.

However, this applies only when the array is block-aligned. In reality, we can expect that this array is randomly placed in a word-aligned location. Some of these will indeed be such that dps takes up two cache blocks, thus creating up to a 2x speedup. It is thus dependent on the exact location of dps, whether the parallelized version runs faster or slower than serial.

# 2. TLP

In signal processing, the technique of **cross-correlation** (or *sliding dot-product*) is often used to determine the delay of a signal. In this problem, we will implement a cross-correlation function in C, parallelized of course! (You don't need to know anything about EE to ace this problem!) :0

The following function,  $sliding_dot$ , takes two arrays. original contains an array of length n and other contains n + k elements. We will shift other k times, and for each shift, compute its dot product with original. We then store these values in result.

We want to parallelize sliding\_dot with OpenMP. Examine our attempts below and choose the behavior(s) you expect from each version. Assume the processor has four threads, 32B cache blocks, and sizeof(int) = 4.You may also assume that all calls to calloc() succeed.

Here is the template of the code where we will replace the /\* OPTIMIZED CODE \*/ with the code on each question.

```

int * sliding_dot(int * other, int * original, int n, int k) {

int * result = (int *) calloc(k * sizeof(int))

// shift the array

for (int shift = 0; shift <= k, shift++) {

/* OPTIMIZED CODE */

}

return result;

}</pre>

```

```

(a) (2.0 pt)

```

result[shift] = dot\_product;

How will this code behave?

Always Correct, faster than serial

Sometimes Incorrect

□ Always Correct, slower than serial

```

(d) (2.0 pt)

```

```

int * shifted = other + shift;

int dot_product = 0

#pragma omp parallel for

for (int i = 0; i < n; i++) {

dot_product += shifted[i] * original[i];

}

result[shift] = dot_product;

How will this code behave?

Always Correct, slower than serial

Always Correct, faster than serial

Sometimes Incorrect

```

#### helpful! 0

## Peyrin Kao 5 months ago

(b) dot\_product is being updated in a critical section, so the threads will wait to update it one at a time. This means there are no data races, so the code is correct. However, the time it takes to start up all the threads means that it would have just been faster to run that one line of code in the for loop serially.

(c) Every thread is writing to a different element of dps so there are no data races, so the code is correct. The speedup depends on whether all the elements of dps are in one cache block, which would lead to false sharing (as explained in the solutions, but feel free to follow up if you have specific questions).

(a) The dot\_product is marked private, so every thread gets its own separate copy. This code is only correct if all the work runs on one thread; otherwise, there's nothing to specify how the different copies of dot\_product get combined.

(d) dot\_product is declared outside the for loop, so every thread writes to the same single copy of the variable. This is vulnerable to data races.

good comment 2

Anonymous Calc 5 months ago

For (a), so for the last line result[shift] = dot\_product; , the system will just randomly pick up a thread and use its dot\_product value?

helpful! 0

## Peyrin Kao 5 months ago

I think it just uses the dot\_product value before any of the threads get run. (In other words, the private variables are local to each thread and get deleted after the thread finishes.)

good comment 0

Reply to this followup discussion

[Su20-MT2-4d]

Assume now, with the current 8-way set associative cache, we add a second-level 64 KiB Direct Mapped cache with 128 B blocks, a write back policy for write hits, and a write allocate policy for write misses. Calculate the respective local hit rates for the L1 and L2 caches.

(d) i. (1.0 pt) L1

| 62/189                               |   |

|--------------------------------------|---|

| A[16] Miss B[0] Miss A[0] Miss       | ~ |

| A[32] Miss B[16] Miss A[16] Hit      |   |

| Alasl Miser - Hil B120 Mise A130 Hil |   |

A[64] Miss B[48] Miss->Hit A[48] Hit A[80] Miss->Hit B[64] Miss A[64] Hit A[96] Miss B[80] Miss->Hit A[80] Hit MMHMHM... MMMHMH... MHHHHH.... HR = 62/189

cam generated for cs61c@berkeley.edu

ii. (4.0 pt) L2

23

| 112 8.7                                                   |                                                                                                                                                                                                                       |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61/127                                                    |                                                                                                                                                                                                                       |

| A[16] Miss B[0] Miss A[0] Miss                            |                                                                                                                                                                                                                       |

| A[32] Miss B[16] Miss A[16]                               |                                                                                                                                                                                                                       |

| A[48] Hit B[32] Miss A[32]                                |                                                                                                                                                                                                                       |

| A[64] Miss B[48] Hit A[48]                                |                                                                                                                                                                                                                       |

| A[80] Hit B[64] Miss A[64]                                |                                                                                                                                                                                                                       |

| A[96] Miss B[80] Hit A[80]                                |                                                                                                                                                                                                                       |

| MMHMHM MMMHMH 0 hit/1 access                              |                                                                                                                                                                                                                       |

| $HR = ((63-1)/2) \cdot 2 + (63-2)//2)/(63+63+1) = 61/127$ |                                                                                                                                                                                                                       |

|                                                           | A[16] Miss B[0] Miss A[0] Miss<br>A[32] Miss B[16] Miss A[16]<br>A[48] Hit B[32] Miss A[32]<br>A[64] Miss B[48] Hit A[48]<br>A[80] Hit B[64] Miss A[64]<br>A[96] Miss B[80] Hit A[80]<br>MMHMHM MMMHMH 0 hit/1 access |

Can someone explain how the values are brought back into the cache? The L1 cache has 64B block and L2 has 128B block. So, if the L1\$ were to miss, go to L2\$ and also miss, would it bring back 32 integers into the L2\$ and then 16 integers into the L1\$?

According to the solution i part i, A[32] is a miss. But, I was thinking it'd be a miss->hit because the first time A[16] is accessed in the line above, it'd bring in 128 bytes into the L2\$, which corresponds to A[16]-A[47]. Then shouldn't A[32] be a hit in the L2\$? I know I'm messing up but I'm not sure where. helpful! 0

# 0 🚺 A

Adelson Chua 5 months ago

would it bring back 32 integers into the L2\$ and then 16 integers into the L1\$? Yes

When L2 missed on A[16], it brought back A[0]-A[31]. That's the whole cache block for L2. The cache block does not always start on the address that you missed.

It might be helpful to write the corresponding addresses in binary then see what the index is. You bring in data from a single index.

good comment 0

| 4    | Anonymous Beaker 5 months agoThen wouldn't A[0] be a miss->hit in the first group of access? Since we access A[16] first, I'massuming it brings A[16:31] into L1 and A[0:31] into L2. So, when we try A[0], it'd miss in L1 andhit in L2, right?helpful!                                                                                                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <b>Adelson Chua</b> 5 months ago<br>Yeah, that's a good point. That reasoning sounds correct.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | A[16] Miss B[0] Miss A[0] Miss<br>A[32] Miss B[16] Miss A[16]<br>A[48] Hit B[32] Miss A[32]<br>A[64] Miss B[48] Hit A[48]<br>A[80] Hit B[64] Miss A[64]<br>A[96] Miss B[80] Hit A[80]<br>MMHMHM MMMHMH 0 hit/1 access<br>HR = ((63 - 1)/2) * 2 + (63 - 2)//2)/(63 + 63 + 1) = 61/127<br>The solution isn't labeling the A[16] as anything (not hit or miss label).<br>I don't know what is going on with the math, but it's as if it is treating that as a miss? Not sure.<br>If it is, then I think there's an error in the solution.<br>good comment 0 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Repl | ly to this followup discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.   | Ourseolved @2127_f10 (c) ymous Beaker 5 months ago SDS, Logic We will be analyzing the following circuit: Image: Constrained of the following circuit: Image: Constrained of the following circuit:                                                                                                                                                                                                                                                                                                                                                      |

|      | Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Given the following information:

- AND gates have a propagation delay of 9ns

- OR gates have a propagation delay of 14ns

- NOT gates have a propagation delay of 5ns

- x\_input switches value(i.e. 1 to 0, 0 to 1) 30 ns after the rising edge of the clk

- **y\_output** is directly attached to a register

- Setup time is 3ns

- Clk-to-q delay time: 4ns

- (a) (2.0 pt) What is the max hold time in ns?

| 18                                                                                           |  |

|----------------------------------------------------------------------------------------------|--|

| Shortest CL: NOT -> AND = $5 + 9 = 14$ ns clk-to-q + shortest CL = $4$ ns+ $14$ ns = $18$ ns |  |

How is the CL defined? Is it register to register, or does it just have to end at a register. I was thinking of  $x_i > AND \rightarrow Reg1$ , which comes out to be 13ns

helpful! 0

Anonymous Beaker 5 months ago

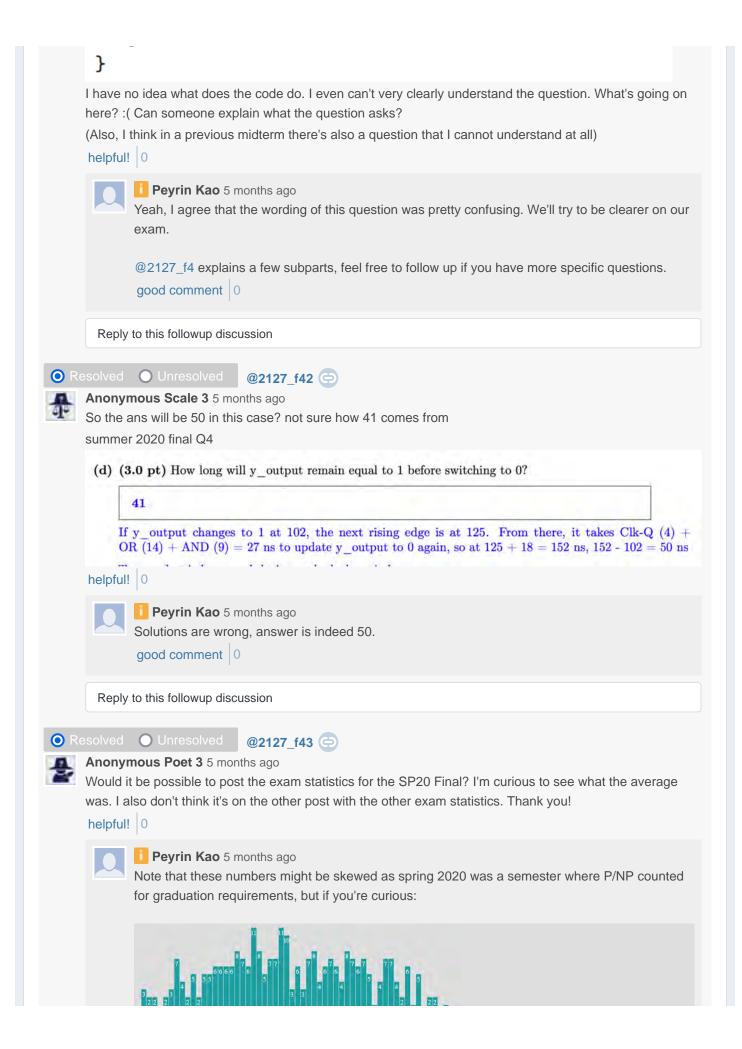

This is Su20-Final-Q4 btw. For 4c, why is the clock period (50ns) being added? I'm not sure what exactly clock period represents. Is it how long it takes for signal to be realized? I thought that was the c2q.

helpful! 0

# Adelson Chua 5 months ago

You start checking for combinational logic delay from a point that is clocked (typically a register, sometimes inputs are also presented as coming from a register) to another point that is clocked (which is usually another register, sometimes outputs are also presented as attached to a register).

In this case, y\_output is attached to a register, x\_input also comes from a register (however, with a c2q delay of 30ns).

What is now the shortest path?

The solutions say the path from Reg1 to y\_output is the shortest. Nothing else is shorter than that. You proposed x\_input -> AND -> Reg1 is longer because x\_input is delayed by 30ns. good comment  $\begin{vmatrix} 1 \end{vmatrix}$

## Adelson Chua 5 months ago

I'll update this follow-up to answer your next question. That requires some drawing. good comment 1

|        | 1 Salton |   | 1 |         | 14 | - |

|--------|----------|---|---|---------|----|---|

| reg Ø  |          |   |   |         |    |   |

| reg1 - |          | 1 |   |         |    |   |

| Y =    |          | 1 |   |         |    |   |

|        |          |   |   | 1.100/1 |    | 1 |

I did the timing diagram and got y to change it's value to 1 at 75 ns. I add in the clk2q and delays for the or and and gate, and get 102 ns. Is this the correct way of doing i? helpful! 0

Adelson Chua 5 months ago Nice! Very nice! Yes this is correct. :) good comment 0

Anonymous Atom 2 5 months ago

why do reg 0 reg 1 and y change at 75? I get why x is changing at 55 but not how each of them change at 75 especially since theres logic gates betweenn the registers and y helpful!

# Adelson Chua 5 months ago

The problem states that there is a 30ns delay from x\_input. Time step 75 is a rising edge of the clock, where the registers update their values. good comment  $\begin{vmatrix} 0 \end{vmatrix}$

# Anonymous Atom 2 5 months ago

so the registers depend on x input. I guess I"m still confused on how the logic gates play a part here. I get why reg 0 would take the x input, but would the and gate before reg 1 not add any propogation delay? and would the and gate not create a 0 for the input of reg1?

and why would y immediatly change as well? is there no clock to q for the register to output a value?

helpful! 0

# **Adelson Chua** 5 months ago

The reg0 and reg1 values shown there are the outputs of the registers, which only update during the rising edge of the clock.

The actual values of the wires does not matter for this problem actually, we are only interested in the delays.

Yeah, the y\_output in the timing diagram is wrong, it should be delayed by the propagation time of the gates from the register to the y\_output.

for (a), (1)just to confirm, is it always true that #of PTE = #of VPN bits? 2) What is this 'information bit' and why we could replace PPN bits with information bits?

(c) how do we find it's a new page? I think it's related to page size, but I found it hard to transform page size into offsets on a single page.

4. Virtual Reality! I Mean Memory...

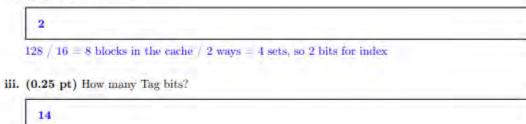

Consider a system with 2 MiB of physical memory and 4 GiB of virtual memory. Page size is 4 KiB. Recall that the single level page table is stored in physical memory and consists of PTE's, or page table entries.

(a) (3.0 pt) If we choose to store seven information bits in each PTE, how big is the page table in bytes?

```

2<sup>21</sup>

VPN contains log(\frac{2^{24}}{2^{12}}) = 20 bits

PPN contains log(\frac{2^{24}}{2^{12}}) = 9 bits

9 bit PPN + 7 info bits = 16 bits per PTE

2<sup>4</sup> bit PTE * 2<sup>20</sup> PTE's = 2<sup>24</sup> bit page table, or 2<sup>21</sup> bytes

```

(b) (3.0 pt) The page table starts off empty, then we make the following accesses: 0x00111999, 0x00234567, 0x005555FFF. If the page table begins at address 0x20000000, at what address can we find the PTE for the first access? (Your answer should be in hex)

0x20000222. 0x00111999 has a VPN of 0x00111. Each PTE is 2 bytes, so 0x00111 \* 2 = 0x00222. 0x20000000 + 0x00222 = 0x20000222.

- (c) (2.0 pt) We have a fully associative TLB that also started empty but now contains the three entries from the accesses above. If we access 0x00556000 now, will we get a TLB hit, page hit, or page fault?

- O TLB Hit

- O Page Hit

- O None of the other answers

Page Fault

Page Fault. 0x00556000 is a new page

# helpful! 0

Adelson Chua 5 months ago

(1)just to confirm, is it always true that #of PTE = #of VPN bits?

Yes, VPN indexes the page table. This is covered in the lecture with corresponding illustrations...

(2) What is this 'information bit' and why we could replace PPN bits with information bits? Those are your valid/dirty/permission bits. Those don't replace the PPN, they are in addition to

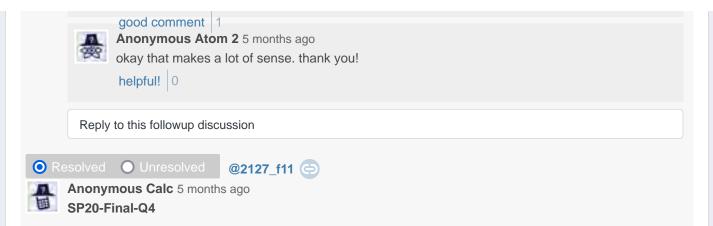

Singe Cycle Mover

XRW YRW MuxSe

BrEq

MemRiA

Control Logic

PFVal

PFSel

Instruction

Let x3, x2, x1, x0 be the bits of an instruction with x0 being the least significant bit, and let BrEq be the value of BrEq. Write the most simplified logical equations for each output of Control Logic.

Please use C syntax when writing out your formulas.

A. (2.0 pt) YRW

~x1 & x2 (or equivalent)

B. (2.0 pt) XRW

~(x1 | x2) (or equivalent)

helpful! 0

# Adelson Chua 5 months ago

Looking at the diagram, YRW controls the WE of the register that determines the value of Y (you can also see it coming from a multiplexed adder adds 1 or adds ffffff (which is -1))

Thus, this would correspond to the 0101 (+1 to y) and 1101 (-1 to y) instructions given in the problem.

Following the same logic, XRW controls the WE for X. This corresponds to the 0001 (+1 to x) and 1001 (-1 to x) instructions.

Now, we have a truth table:

| x3 | x2 | x1 | x0 | YRW | XRW |

|----|----|----|----|-----|-----|

| 0  | 0  | 0  | 1  | 0   | 1   |

| 1  | 0  | 0  | 1  | 0   | 1   |

| 0  | 1  | 0  | 1  | 1   | 0   |

| 1  | 1  | 0  | 1  | 1   | 0   |

| 0  | 0  | 1  | 1  | 0   | 0   |

| 1  | 0  | 1  | 1  | 0   | 0   |

| 0  | 1  | 1  | 1  | 0   | 0   |

| 1  | 1  | 1  | 1  | 0   | 0   |

At this point, just write the corresponding Boolean expression for YRW and XRW in terms of X3 X2 X1 X0 and simplify.

good comment 0

Anonymous Comp 2 5 months ago

Okay I see. Thank you! How would I come up with the rest? Do I follow the same logic? Sorry I'm really lost on this part.

|            | C. (2.0 pt) PFVal                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------------|

|            | "x3 (or the equivalent tx3)                                                                                     |

|            | D. (2.0 pt) PFScl                                                                                               |

|            | x1 & x2 & BrEq (or equivalent)                                                                                  |

|            | E. (2.0 pt) MemRW                                                                                               |

|            | x1 & "x2 (or equivalent)                                                                                        |

|            | F. (2.0 pt) MaxSel                                                                                              |

|            | Ex                                                                                                              |

|            |                                                                                                                 |

| helpful! 0 |                                                                                                                 |

|            | Chua 5 months ago<br>eed to understand how the datapath works and relate how the control signals affect<br>ata. |

| -          | no methodical way of solving this aside from just looking at the datapath and see                               |

good comment 0

functionality.

# Anonymous Scale 2 5 months ago

For MemRW, why is it not ~x1 & x2? I was thinking about when the intruction is 0011 or 1011 which is when x1 is 0 and x2 is 1, we want to set MemRW to 1. helpful! 0

**Adelson Chua** 5 months ago

The ordering of the bits is x3,x2,x1,x0, so that actually translates to x2=0 and x1=1.

Good to know you were able to understand the datapath though!

good comment 0

Anonymous Helix 2 5 months ago

Would it be incorrect if we added a "&x0" to some parts? (I realized after looking at the answers that x0 was always 0)

helpful! 0

**Anonymous Helix 2** 5 months ago for C and D, is PFVal our "new" program flow value if the cases for "]" or "[" pass and PFSel whether or not we choose that "new" value?

helpful! 0

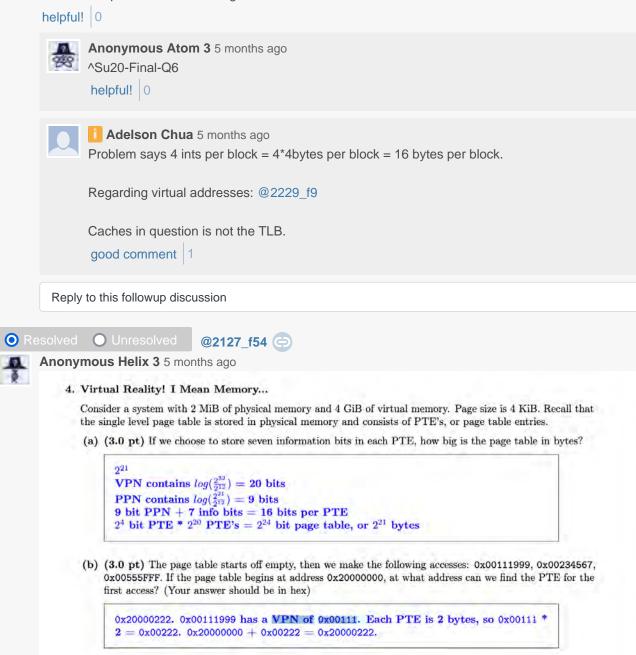

| 09     | r <b>mous Gear 2</b> 5 months ago<br>ner 2020 Final Q6 part cii]                                                                                                                                                                                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ii     | i. A[1] Read                                                                                                                                                                                                                                                                                                    |

|        | A. (0.25 pt)                                                                                                                                                                                                                                                                                                    |

|        | Miss                                                                                                                                                                                                                                                                                                            |

|        | ⊖ Hit                                                                                                                                                                                                                                                                                                           |

|        | B. (0.25 pt)                                                                                                                                                                                                                                                                                                    |

|        | State from proc 0's point of view.                                                                                                                                                                                                                                                                              |

|        | ○ М                                                                                                                                                                                                                                                                                                             |

|        | ○ E                                                                                                                                                                                                                                                                                                             |

|        | • 0                                                                                                                                                                                                                                                                                                             |

|        | $\bigcirc$ s                                                                                                                                                                                                                                                                                                    |

|        | $\bigcirc$ I                                                                                                                                                                                                                                                                                                    |

|        |                                                                                                                                                                                                                                                                                                                 |

| helpfu | <ul> <li>oesn't that mean from proc 0's perspective, isn't that value Invalid?</li> <li>I! 0</li> <li><b>Adelson Chua</b> 5 months ago</li> <li>If you check the diagram for MOESI. Proc0 was in Modified state before this question, then a probe read hit (another processor reads) goes to Owned.</li> </ul> |

|        | Why would it be invalid? The other processor is just reading the data<br>good comment 1                                                                                                                                                                                                                         |

| Reply  | y to this followup discussion                                                                                                                                                                                                                                                                                   |

|        | O Unresolved @2127_f16 🕞<br>mous Beaker 5 months ago<br>final-1bii]                                                                                                                                                                                                                                             |

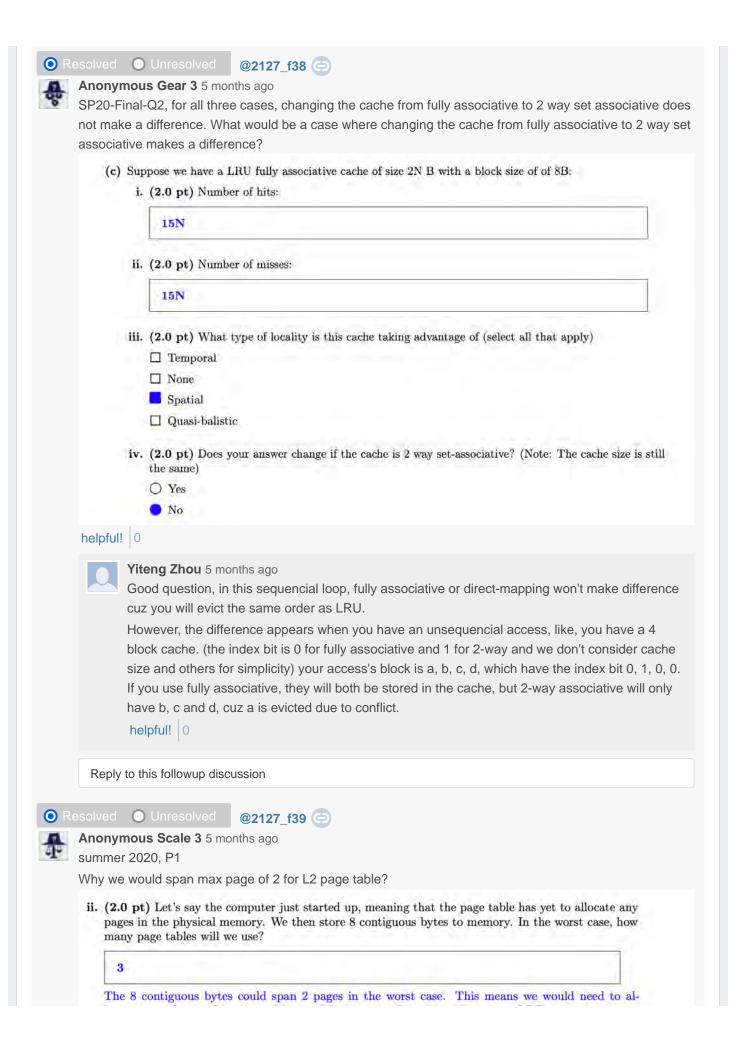

| F      | <b>2.0 pt)</b> Let's say the computer just started up, meaning that the page table has yet to allocate any bages in the physical memory. We then store 8 contiguous bytes to memory. In the worst case, how nany page tables will we use?                                                                       |

| [      | 3                                                                                                                                                                                                                                                                                                               |

|        | The 8 contiguous bytes could span 2 pages in the worst case. This means we would need to al-<br>ocate space for two L2 pages tables in addition to one L1 page table = $3$ total PTs.                                                                                                                           |

| do we  | need 2 L2 page tables in the worst case bc the 8 contig bytes of memory could be split across 2                                                                                                                                                                                                                 |

| physical pages in memory, and the PPN for these two physical pages are split into two separate page tables (ie one PPN is at the end of one L2 page table and the other PPN is at the start of the second L2 page table)?                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adelson Chua 5 months ago<br>Yes! Exactly!<br>good comment 0                                                                                                                                                                                                                                                                                                         |

| Anonymous Beaker 2 5 months ago<br>Why couldn't the 8 byte be split for L1?<br>helpful! 0                                                                                                                                                                                                                                                                            |

| Adelson Chua 5 months ago<br>You can't split the L1. There's only 1 L1 page table in a two-level page table set up.<br>good comment 0                                                                                                                                                                                                                                |

| Reply to this followup discussion                                                                                                                                                                                                                                                                                                                                    |

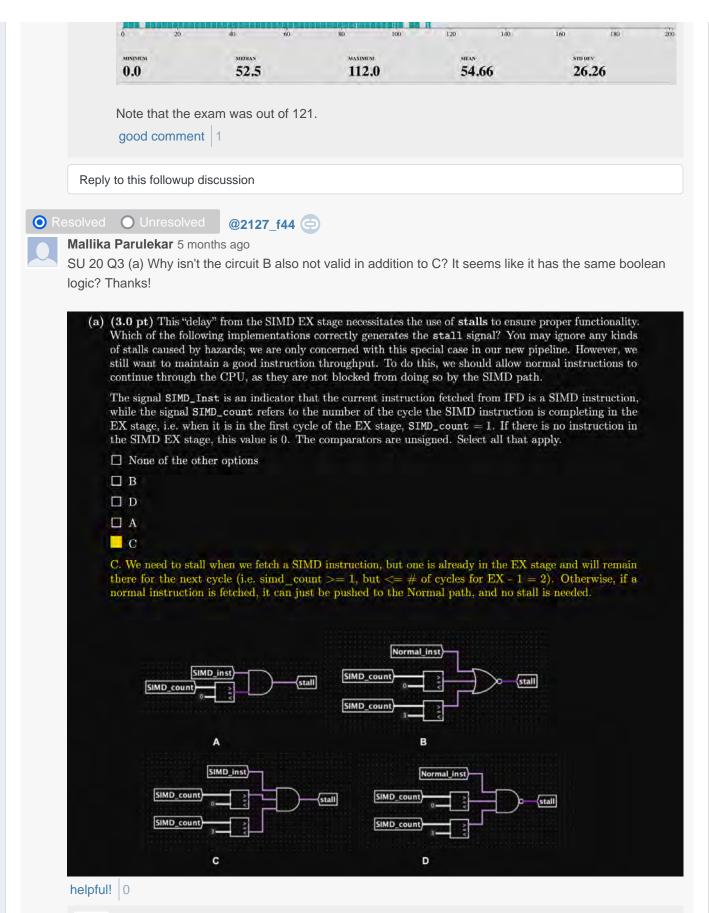

| <ul> <li>Resolved O Unresolved @2127_f17 (c)</li> <li>Anonymous Scale 2 5 months ago<br/>[su20-final-Q3c]</li> <li>I'm confused about how stalling works here. I thought we need to wait for 3 cycles for SIMD instructions and therefore 3 stalls for each SIMD instruction.</li> </ul>                                                                             |

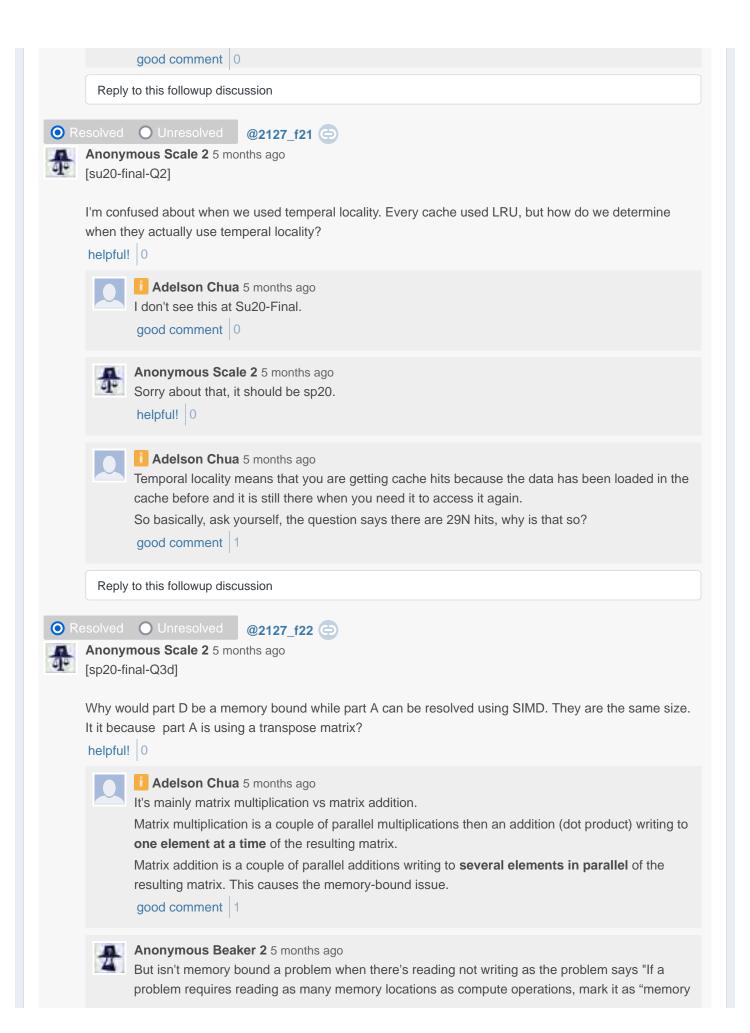

| <ul> <li>(c) (2.0 pt) How many stalls caused by the SIMD EX stage are needed for the following piece of code?</li> <li>1. addi t0, x0, 1</li> <li>2. simd_add x1, x2, x3</li> <li>3. simd_sub x2, x1, x3</li> <li>4. addi t1, t0, 2</li> <li>5. simd_mul x2, x2, x2</li> <li>6. sub t0, t0, t1</li> <li>7. mul t0, t0, t0</li> <li>8. simd_div x2, x2, x1</li> </ul> |

| 3<br>Line 2 adds 2 stalls.<br>Line 5 adds 1 stall left over from simd_sub.                                                                                                                                                                                                                                                                                           |

| helpful! 0                                                                                                                                                                                                                                                                                                                                                           |

| Peyrin Kao 5 months ago<br>Line 2 adds 2 stalls because the IFD stage of line 3 can execute while line 2 is in its third SIMD<br>EX stage.                                                                                                                                                                                                                           |

Line 5 adds one stall since it needs to wait for line 3 to finish its third SIMD EX stage.

|          | 1                        | IFD                                                                                 | EX                                                                                       | MEM                                                                                              | WB                                                                  |                                                        |          |           |            |          |          |              |         |     |

|----------|--------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|----------|-----------|------------|----------|----------|--------------|---------|-----|

|          | 2                        |                                                                                     | IFD                                                                                      | EX                                                                                               | EX                                                                  | EX                                                     | MEM      | WB        |            |          |          |              |         |     |

|          | 3                        |                                                                                     |                                                                                          | -                                                                                                | -                                                                   | IFD                                                    | EX       | EX        | EX         | MEM      | WB       |              |         |     |

|          | 4                        |                                                                                     |                                                                                          |                                                                                                  |                                                                     |                                                        | IFD      | EX        | MEM        | WB       |          |              |         |     |

|          | 5                        |                                                                                     |                                                                                          |                                                                                                  |                                                                     |                                                        |          |           | _          | IFD      | EX       | EX           | EX      | MEM |

|          | WB                       |                                                                                     |                                                                                          |                                                                                                  |                                                                     |                                                        |          |           |            |          |          |              |         |     |

|          | gooc                     | l comr                                                                              | nent                                                                                     | 2                                                                                                |                                                                     |                                                        |          |           |            |          |          |              |         |     |

| Rep      | oly to this              | follow                                                                              | up diso                                                                                  | cussion                                                                                          |                                                                     |                                                        |          |           |            |          |          |              |         |     |

| [su20    | phi<br>Nor<br>The<br>phi | C]<br>t) After<br>of the fi<br>lspel i<br>ne of the<br>addres<br>lspel i<br>lspel i | the seco<br>ollowing<br>s in the<br>e other o<br>s for <b>ph</b><br>s in the<br>s an ext | onths ag<br>ond pass h<br>is true a<br>.text se<br>options<br>ilspel w<br>.text se<br>ernal refe | by the a<br>bout pr<br>gment of<br>vas resol<br>gment of<br>erence. | ssembler,<br>iilspel?<br>of max.s<br>lved.<br>of jie.s | Select a | Il that : | apply.     |          |          | cation table | e.      |     |

|          | l someoi<br>ul! 0        | ne exp                                                                              | olain w                                                                                  | hy it is                                                                                         | true ti                                                             | nat phil                                               | spel is  | in the    | e .text se | egment   | ?        |              |         |     |

| <b>.</b> | I thou<br>there          | ight it                                                                             | can al                                                                                   | i <b>le 2</b> 5 i<br>so be ii<br>pass w                                                          | n the o                                                             | code se                                                | -        |           | ng as it'  | s refere | enced be | efore it's   | definec | 1   |

|          |                          |                                                                                     |                                                                                          |                                                                                                  |                                                                     |                                                        |          |           |            |          |          |              |         |     |

If in the first pass of the assembler a label is resolved, we know definitively it's in the code/text segment of that file and that it's defined before the label is used. The second pass takes a look at labels that are either in an external file/library or is defined after it is used.

Because at this stage our file does not have any knowledge beyond just the file, it cannot resolve anything not defined within itself. Thus, we know that philspel cannot be defined in an external file or library (that's taken care of by the linker).

Thus, philspel is defined within the file itself. There are two main chunks when it comes to an assembly file: the static/data section and the text section.

The static section **cannot** be resolved at the assembly stage. This is because static data belongs in the static segment of memory, which is independent from the text segment. We know the linker is in charge of merging and (re)ordering the combined static and text segments for all files linked at the linker stage, so as of right now, we have no idea where in static memory any static data will reside. Thus, it cannot be resolved and we know philspel cannot be defined in .static of max.s.

That leaves us with the .text segment of max.s by process of elimination. But let's prove it!

We know within a single file, the text segment will not be recorded (since they're instructions and instructions should be executed in the order the programmer/compiler intended for them to be). Thus, as long as we know where the label is defined within the scope of max.s, we can technically resolve it.

This is true for all branch instructions, since they're all PC-relative and thus, shifting and relocating the code will not affect its calculation.

For jal instructions (the main other one besides b\* that uses PC-relative addressing), the label can be a local or external reference. External references need to be relocated, which means they cannot be resolved after the second pass of the assembler. However, local ones can be.

Thus this implies philspel is in the text of max.s.

Hope this makes sense!

# good comment 2

Anonymous Poet 2 5 months ago is the .static you are referring to here the same as the .data assembler directive? helpful! 0

**Caroline Liu** 5 months ago Yep!

good comment 0

Anonymous Scale 3 5 months ago

Hi, Caroline. Thanks for the deep explanation. So it that means the branch, jump are in .text segment as well? Or typically, what is the factor we used to check something is in .text segment? helpful! 0

# ő

**Caroline Liu** 5 months ago

.text is just defined as anything that's considered to be code and would go in the code/text segment of main memory when loaded. This does include jump and branch instructions yes. There is no real "check" I think aside from the fact that when you look at an assembly file, everything after the .text directive, everything is considered to be code!

good comment 0

## **Peyrin Kao** 5 months ago

I think SIMD is the most appropriate answer here because you're performing one operation (multiplication, with maybe some addition) on multiple data. MIMD is a better answer when there are many instructions that have to be executed on multiple data. You're right that Project 4 uses both SIMD and MIMD for this task, though, so it's not the most unambiguous question.

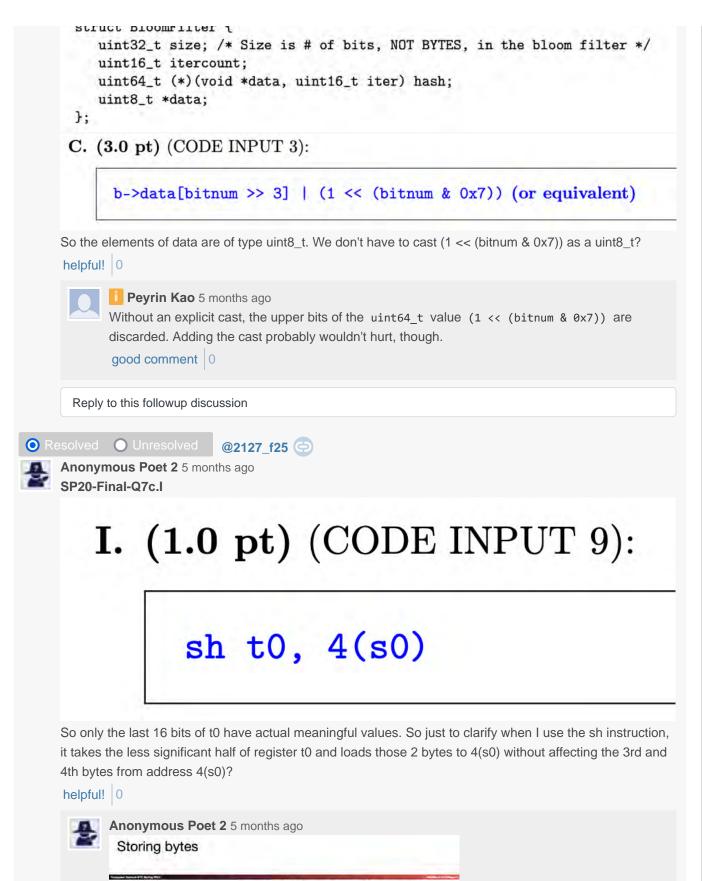

- When you store a byte, only the lower 8 bits of the register is copied to memory, so there is no sign-extension

- This means that we don't need a store byte unsigned (sbu) instruction

Found the answer.

helpful! 0

Reply to this followup discussion

Resolved O Unresolved @2127\_f26 👄 Anonymous Poet 2 5 months ago

- SP20-Final-Q8.C

- C. (2.0 pt) What are assembler directives (explain what they are used for, don't just give examples of them)?

They give directions to the assembler, but do not produce machine instructions.

I thought that the assembler outputs .o files which are machine code. Doesn't this mean that the machine code is made up of machine instructions (albeit we still have to resolve absolute offsets)?

helpful! 0

# Caroline Liu 5 months ago

The assembler itself is what eventually helps provide the machine instructions without absolute references but the assembler directives themselves are not in charge of producing the machine instructions. The job of the directives is to provide information to the assembler, such as start and end of a program/file, memory locations, where start/end of macros/segments are, and more.

Does that answer your question?

good comment 1

Anonymous Poet 2 5 months ago yes ty!

helpful! 0

Reply to this followup discussion

@2127\_f27 🖨

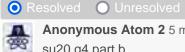

Anonymous Atom 2 5 months ago su20 q4 part b

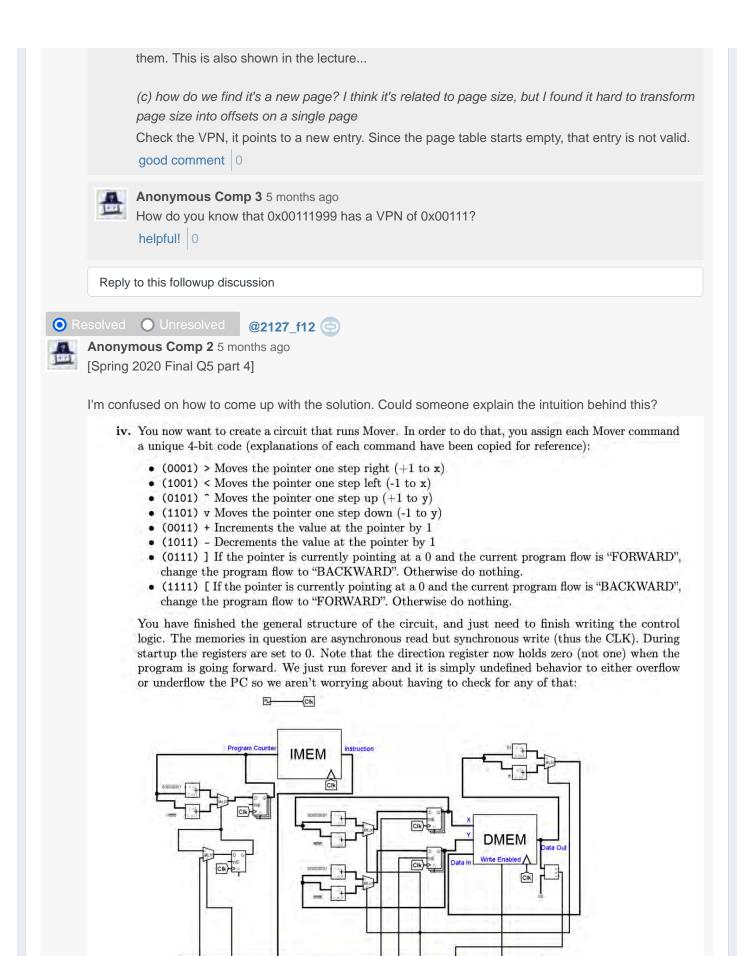

(b) (2.0 pt) What is the minimum clock period in ns?

```

42

```

Critical path = clk-to-q + longest CL + setup = 30ns for x\_input to change (includes clk-to-q) + 9 AND + 3 setup = 42 ns

Can someone help me understand why we use x input here? i thought min clock period was to find the longest cl between two registers, which x isnt, and add the clk to q and setup time. I think I'm missing something conceptually?

helpful! 0

|             |       | i wouldve thought the answer wouldve been clock to q + OR + AND (from reg0 to y output) + setup<br>helpful! 0                                                                                                                                                                                                                                            |  |  |  |  |

|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|             | 会     | Anonymous Atom 2 5 months ago<br>since x input isn't a register, I dont get why we're only calculating from x input to reg1<br>helpful!                                                                                                                                                                                                                  |  |  |  |  |

|             |       | Adelson Chua 5 months ago@2127_f13good comment0                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|             | 会     | Anonymous Atom 2 5 months ago<br>i understand the critical path is between two registers, is x input a register because the problem<br>says it changes 30ns after the rising edge of the clock?<br>helpful! 0                                                                                                                                            |  |  |  |  |

|             |       | Adelson Chua 5 months ago         yes.         good comment       1                                                                                                                                                                                                                                                                                      |  |  |  |  |

|             | 要     | Anonymous Atom 2 5 months ago<br>okay thank you!<br>helpful! 0                                                                                                                                                                                                                                                                                           |  |  |  |  |

|             |       | Adelson Chua 5 months agoYou treat x input as a register with a clk-to-q of 30nsgood comment0                                                                                                                                                                                                                                                            |  |  |  |  |

|             | Reply | Reply to this followup discussion                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| <b>O</b> Re |       | O Unresolved @2127_f28 🕞<br>mous Mouse 2 5 months ago                                                                                                                                                                                                                                                                                                    |  |  |  |  |

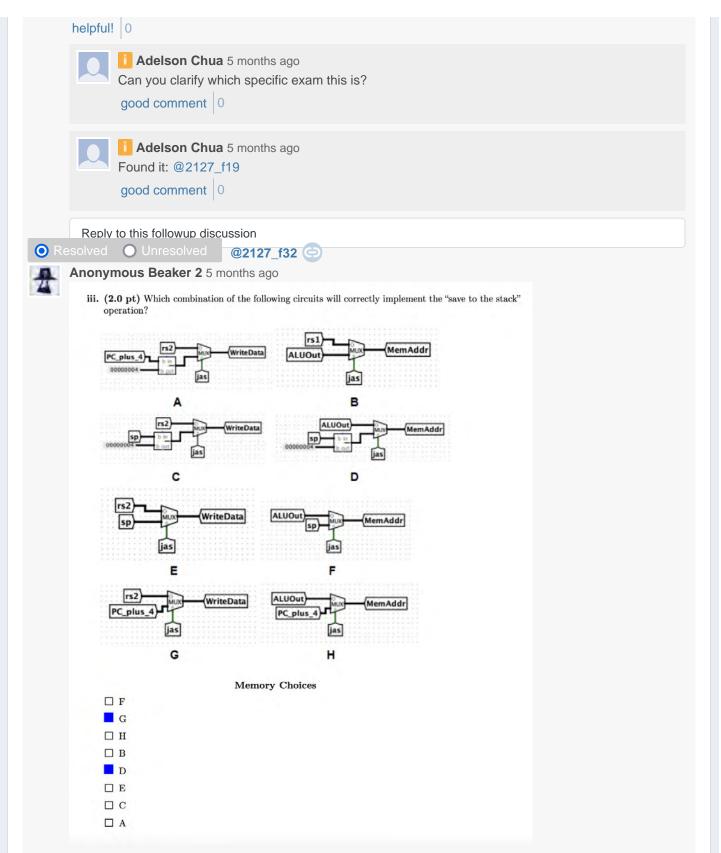

| B           |       | meone explain how to go through Summer 2020 Final 6c? I'm confused with how to determine r it is a hit or miss and when something is owned.                                                                                                                                                                                                              |  |  |  |  |

|             |       | (c) We decide to parallelize a for loop across these 2 processors, but instead of using OpenMP, we have each thread do a strided memory access, where processor 0 handles even indices, while processor 1 handles odd indices. However, the memory accesses are perfectly interleaved, i.e. the order of array accesses are still A[0], A[1], A[2], A[3] |  |  |  |  |

|             |       | <pre># define ARR_LEN 32 // A is located at address 0xA0000 int A[ARR_LEN];</pre>                                                                                                                                                                                                                                                                        |  |  |  |  |

|             |       | <pre>// Processor 0's loop for (int i = 0; i &lt; ARR_LEN; i += 2) {         A[i] += i }</pre>                                                                                                                                                                                                                                                           |  |  |  |  |

|             |       | // Processor 1's loop<br>for (int $j = 1$ ; $j < ARR_LEN$ ; $j \neq 2$ ) {                                                                                                                                                                                                                                                                               |  |  |  |  |

ALJJ += J

3

For each memory access below,

- i. Classify it as a Hit or Miss. Snooping another cache for data is considered a coherency Miss.

- Since we are working in a multiprocessor system, classify the state of the block that the data accessed resides in from the specified processors perspective.

# helpful! 0

Adelson Chua 5 months ago

You would have to look at the state diagram to truly understand this.

Know that in the beginning, you start at the Invalid state.

i) A[0] Read (this is done by processor 0, as stated in the problem)

This is a **compulsory miss**. You already know this from a typical cache problem.

Looking at the diagram, from Invalid, you go to **Exclusive** after a read miss. Since this is the first processor to access that data, it gets 'exclusive' access to that data. Exclusive = I'm the only one who has this data.

ii) A[0] Write (this is still done by processor 0).

Due to the miss before, you pulled the data into the cache, so now this is a **hit**. Typical cache problem.

Looking at the diagram, from Exclusive state, you go to Modified after a write hit. Since the

processor has made changes, it is now modified. Logically, it makes sense.

iii) A[1] Read (this is done by processor 1, as stated in the problem)

Since processor 1 is executing this, processor 1's cache is still empty. This is a **compulsory miss**.