! This class has been made inactive. No posts will be allowed until an instructor reactivates the class.

| note @2128 🔿 🛧 408 views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| [Past Exams] 2021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | s <b>*</b> |

| You can find the past exams here: https://cs61c.org/sp22/resources/exams/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| Spring 2021 final walkthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| When posting questions, please reference the semester, exam, and question in this format so it's easier for students and staff to search for similar questions:                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| Semester-Exam-Question Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| For example: SP21-Final-Q1, or SU21-MT2-Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| exam exam/final                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| good note 0 Updated 5 months ago by Jerry Xu and Peyrin Kad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | С          |

| followup discussions, for lingering questions and comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| <b>Cesolved</b> Unresolved @2128_f1 (c)          This was marked a duplicate to the question/note above by Peyrin Kao 5 months ago         Anonymous Atom 5 months ago         [fa21-final] Questions         [fa21-final-5.3] Can anyone explain this solution?         Q5.3 (2.5 points) Write a sequence of instructions that causes a hazard in a completely unoptimized 5-stage pipeline (no forwarding, no branch prediction, no synchronous read/writes, etc.), but which would not cause a hazard if all mac instructions were changed to mul instructions. If no such sequence exists, write "Not Possible." |            |

| Solution: Note that regardless of the values stored in registers, we still need to stall (since we don't change operation based off ID), so we can write code without initializing registers. The extra hazard that occurs as a result of this instruction is a data hazard on rd; with mul, we don't need to wait for the value of rd to get written back, but we do need to wait for rd for a mac. Thus, a correct answer required a mac instruction up to 3 instructions after its rd got updated, and no other hazards involving other registers. Our staff solution was: mac a0 a1 a1 mac a0 a1 a1               |            |

[fa21-final-5.2] Why "add a new rs3 input to RegFile" is incorrect?

Q5.2 (3 points) We want to add a new instruction mac (multiply and accumulate) to our CPU:

mac rd, rs1, rs2

Set rd to rd + (rs1 \* rs2).

What changes would we need to make to our datapath in order for us to implement this instruction (with as few changes as possible)? Select all that apply.

$\Box$  Add a new instruction format

□ Add a new immediate type for the ImmGen

□ Add a new rs3 input to RegFile

Add a new output to RegFile for a third register value

$\hfill\square$  Add a new input to AMux and update the relevant selectors/control logic

□ Add a new input to BMux and update the relevant selectors/control logic

Add a new ALU input for a third register input

Add a new ALU operation and update the relevant selectors/control logic

$\hfill\square$  Add a new input to WBMux and update the relevant selectors/control logic

$\hfill\square$  None of the above

[fa21-final-1.8] Why 9??

Q1.8 (0.5 points) RAID 5?

TiB

**Solution:** In RAID 5, we get one parity block for every 9 data blocks, so we get a total capacity of 9 TiB

### helpful! 0

**Adelson Chua** 5 months ago

Can anyone explain this solution?

Since the mac instruction needs the value of rd to complete the operation (rd + rs1\*rs2), the following sequence will cause a data hazard due to dependency on a0 (rd)

mac a0 a1 a1 #a0 will be updated here

mac a0 a1 a1 #updated a0 is needed here, data hazard.

However, if this is replaced with a mac instead, there is no dependency on rd, since it is just the destination register.

mul a0 a1 a1 #a0 will be updated here

mul a0 a1 a1 #a0 will be updated here, no data dependency, no hazard.

[fa21-final-5.2] Why "add a new rs3 input to RegFile" is incorrect? Look at the instruction description, there's no rs3 needed. It's just rs1, rs2, rd.

[fa21-final-1.8] Why 9??

|          | -          |       |          |                                                                                      |

|----------|------------|-------|----------|--------------------------------------------------------------------------------------|

|          | 9.         |       | there a  | are 10 disks, 1 disk worth of parity is distributed among the remaining disk. 10-1 = |

|          | Anon       |       |          |                                                                                      |

| B        |            |       |          | ouse 5 months ago<br>o wait for the value of rd for mul?                             |

|          | helpf      |       |          |                                                                                      |

|          |            | 1     |          |                                                                                      |

| -        |            | -     |          | ouse 5 months ago                                                                    |

| U        | don't      |       |          |                                                                                      |

|          | helpf      | u!!   | 0        |                                                                                      |

|          | i Ac       | lels  | on Ch    | ua 5 months ago                                                                      |

|          | The s      | eco   | nd mul   | I instruction does not depend on the result of the first one.                        |

|          | good       | con   | nment    | 0                                                                                    |

|          | Anon       |       |          | eaker 5 months ago                                                                   |

| 4        | What       |       |          | saker 5 months ago                                                                   |

|          |            |       |          |                                                                                      |

|          | helpf      | ul!   | 0        |                                                                                      |

|          | Po         | vrir  | Kao      | 5 months ago                                                                         |

|          |            | -     |          | struction defined in the context of that exam question.                              |

|          | good       | con   | nment    | 0                                                                                    |

|          |            |       |          |                                                                                      |

| Reply    | to this    | tolio | wup ai   | iscussion                                                                            |

| Resolved | ΟU         | nres  | solved   | @2128_f2 🖨                                                                           |

|          |            |       |          | onths ago                                                                            |

| FA21-Fi  | nal-Q6     | 6.3   |          |                                                                                      |

| Q6.3 (   | (2.5 po    | ints  | Par 3    |                                                                                      |

| 1        | An X i     | s use | ed to si | ignify that either 1 or 0 can be outputted for the corresponding input.              |

| [        | WY         | Z     | Out      |                                                                                      |

|          | 0 0        | -     | X        |                                                                                      |

| -        | 0 0        | -     | X        |                                                                                      |

|          | 0 1<br>0 1 | -     | 0        |                                                                                      |

|          | 1 0        | -     | X        |                                                                                      |

|          | 1 0        |       | X        |                                                                                      |

|          | 1 1        | -     | 1        |                                                                                      |

|          | 1 1        | 1     | 0        |                                                                                      |

|          | -          |       |          |                                                                                      |

|          | -          |       | _        |                                                                                      |

| T        | Sala       | tion  | . Staf   | f solution: $W \wedge Z$                                                             |

Other answers may be possible (Notably, this question can yield a score well below par).

In this case, we note that there's never a time when Y distinguishes between 1 and 0; as such, Y never affects the result of our output, and we can look at the reduced truth table containing only W and Z.

Could someone help me with this problem if I were to brute force this problem with boolean algebra? This is my work so far:

(~W & Y & Z) | (W & Y & ~Z) Y((~W&Z) | (W&~Z)) Y(W ^ Z)

I'm not really sure how you get rid of the Y

helpful! 0

Anonymous Comp 5 months ago FA21 Final 6.3 ^^ helpful! 0

### **Peyrin Kao** 5 months ago

Your first sum-of-products expression is assuming that the four X values in the table are 0s, so brute-forcing here won't help you get rid of Y. In other words, that sum-of-products expression isn't equivalent to the truth table because of the X values.

good comment 0

Anonymous Comp 5 months ago

Does that mean this problem can be only solved by eye? Or is there a correct way to create a sum-of-products expression?

Adelson Chua 5 months ago

There is a methodical way using K-maps but this isn't covered in 61C. I'm guessing for this problem, this is mainly through inspection.

good comment 1

### Eugenia Chien 5 months ago

As someone who took this final, I solved this problem by inspection :)

I like to watch for which inputs affect the output, i.e. what inputs can change without affecting output, what inputs are always the same when the output is some value, etc. helpful!

Anonymous Comp 3 5 months ago Wait isn't the answer (W  $\oplus$  Z)? Since (W  $\land$  Z) evals to 0 when W and Z are 1 helpful! 0

### Anonymous Gear 5 months ago

Can someone explain to me how this works? If x = -1 doesn't the while loop keep running still? Since -1>0.

Q1.9 (1 point) We run the following code on two threads.

```

1 int y = 0;

2 int x = 10;

3 #pragma omp parallel

4 {

5 while(x>0)

6 {

7 y = y+1;

8 x = x-1;

9 }

10 }

```

What is the smallest possible value y can contain after this runs?

Solution: This one's a bit tricky. The optimal sequence is:

Thread 1 reads y=0 and goes to sleep. Thread 2 runs to completion. Thread 1 wakes up and writes y=1, reads x=0, sets x=-1, then sees x==-1 and stops the loop.

### helpful! 0

Anonymous Gear 5 months ago

Oh wait. Sorry I get why it stops the loop but is this basically saying that thread 2 goes through 10 iterations of the while loop, but Thread 1 is still asleep? How is this possible? helpful! 0

Adelson Chua 5 months ago Yes, that is possible. Different threads run at different times. Interleaving is not guaranteed. good comment 0

Anonymous Gear 5 months ago

If it was #pragma omp parallel for instead, would the threads have to run 1 iteration of the loop each or no?

helpful! 0

Adelson Chua 5 months ago There's no for loop though... good comment 0

Anonymous Gear 5 months ago Sorry if it was a for loop too helpful! 0

Adelson Chua 5 months ago #pragma omp parallel for

for(int i = 0; i<something; i++){</pre> }

Each thread will have their own i values.

good comment 0

Anonymous Comp 2 5 months ago

To clarify, even though x and y are shared variables, each thread can keep a local copy after they perform a read, and it's when the threads write to the shared variables that the value becomes visible to all threads?

helpful! 2

Edrees Saied 5 months ago

^ I had the same question. How can thread 1 read x = 0, but y = 1? Shouldn't it also read y = 10? helpful! 0

Anonymous Poet 2 5 months ago

^ I also don't understand how thread 1 can write y=1. in order for it to write, it must have gone thru the loop once, but x is already 0 so how can it enter the loop?

helpful! 0

Adelson Chua 5 months ago

To clarify, even though x and y are shared variables, each thread can keep a local copy after they perform a read, and it's when the threads write to the shared variables that the value becomes visible to all threads?

Correct.

You guys should put this back to "Unresolved" if you want us to see this. good comment 0

Anonymous Gear 3 5 months ago Where does thread 1 read x = 0? helpful! 0

**Adelson Chua** 5 months ago

Once thread2 completes the loop (x becomes 0 at the end of the loop), only then will thread1 start to read x (at which point, x is already 0)

good comment 0

Reply to this followup discussion

Resolved O Unresolved @2128\_f6 \ominus

SP21-Final-Q2.A.I

H. NOTE: for all parts, assume changes propogate unless otherwise stated.

As we're working on running the code snippet, we realise we want to run different instances of the

same code. We choose to employ virtual memory on our memory space. We have 4 GiB of virtual memory and 16 MiB of physical memory mapped with a single level page table with a page size of 4 KiB. We choose to store 8 bits of metadata with each page table entry.

I. After running one iteration of the inner loop for the code given in line, how many physical pages will our page table take up?

1024

NOTE: because we did not specify alignment for the system, if you solved for a byte-aligned system, you will get the points for 768 pages.

So the page table has  $2^32$  entries because the virtual memory has  $2^32$  Bytes. Each PTE must take 4 bytes => The page table takes  $2^32 * 2^2 = 2^34$  Bytes. Each page is 4KiB =  $2^12$  bytes. So the number of physical pages that the Page Table takes up should be  $2^34 / 2^12 = 2^22$  right?

Where am I miss interpreting the question? Thanks in advance.

helpful! 0

Anonymous Scale 5 months ago

Nvm I'm an idiot, the number of PTEs is 2<sup>(number of VPN bits)</sup>, which in this case is 2<sup>2</sup>0, so then we have number of bytes in page table =  $2^20 \times 2^2 = 2^2$ . Which means that the number of pages that the page table takes up is  $2^2 / 2^1 = 2^1 = 1024$ .

helpful! 0

8

Anonymous Scale 5 months ago

J. If our caching system remains as seen in question 1, how many caches would be needed to fully fit our page table? Give your answer as a decimal to two decimal places.

In practice does this actually ever occur where we are trying to fit our page table into a cache? Doesn't the TLB serve this purpose? helpful! 0

Adelson Chua 5 months ago

Yeah. TLBs are the caches just serving a different purpose.

good comment 0

Reply to this followup discussion

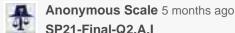

/\* Only the following in the code actually matters:

sl->next gives us back a pointer to a pointer to an SLN (skip list node). next[level] is the same operation as \*(next + level), which makes it seem like this code wants to return a pointer to the level'th SLN node. But how do we know that SLN\*\* pointers are exactly consecutive in memory?

helpful! 0

#

Anonymous Scale 5 months ago

Just realized that the struct SLN\*\* next is treated as an array not a pointer. helpful! 0

Reply to this followup discussion

C. is\_null rd, rs1 is not in a standard RISC-V instruction format; as we're attempting to reduce the number of hardware changes in our datapath. We instead choose to implement our instruction as a pseudoinstruction in the following format. Which of the following statements is true? Assume earlier changes propagate. Select all that apply.

Format: R-Type Instruction

- We need to wire x0 as rs2 and modify the control signals.

- $\bigcirc$  We need to provide a second argument x0 when calling the instruction and modify the control signals.

- $\bigcirc$  We need to provide a second argument x0 as a comparator for all branch comparisons.

- $\bigcirc$  We need to wire x0 as a comparator for all branch comparisons.

- It is impossible to represent as an R-Type instruction.

I don't quite understand the solution, why do we need to modify the control signals? Are we trying to implement is\_null using the ALU instead of the branch comparator?

https://inst.eecs.berkeley.edu/~cs61c/sp21/pdfs/exams/Sp21\_Final\_Solutions.pdf

| helpf     | ul! O                                                                                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <b>Adelson Chua</b> 5 months ago<br>Are we trying to implement is_null using the ALU instead of the branch comparator?<br>The branch comparator will be comparing inputs from the two registers, so using x0 as rs2 is            |

|           | feasible.<br>good comment 0                                                                                                                                                                                                       |

| O Resolve | bly to this followup discussion<br>d O Unresolved @2128_f9 👄                                                                                                                                                                      |

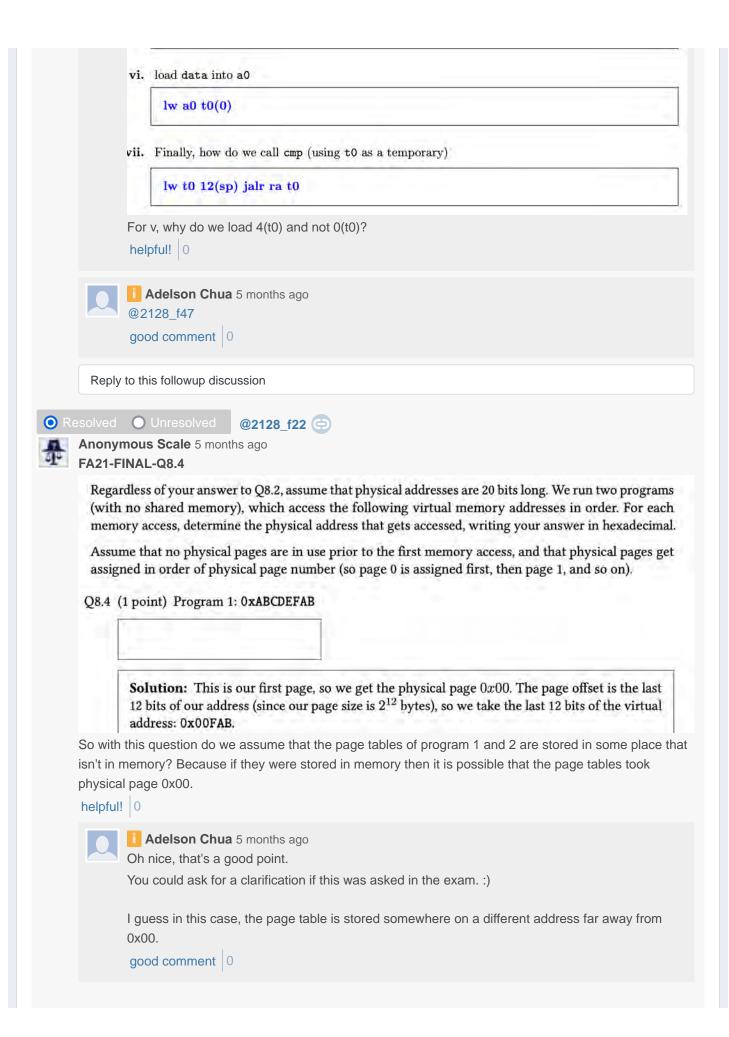

| 100 B     | ymous Scale 5 months ago<br>-Final-Q8.b                                                                                                                                                                                           |

| (b)       | Part 2: RISC-V translation<br>As a reminder, you many NOT use Venus for this question. As a reminder, hexadecimal strings should be                                                                                               |

|           | written with the "0x" prefix, with CAPITALIZED hex digits (ex. 0xDEADBEEF).<br>Translate the following instruction to hexadecimal: srai t0 s3 16. Remember to include the "0x" at the<br>beginning!                               |

|           | 0x4109D293                                                                                                                                                                                                                        |

| helpfu    | Image: Adelson Chua 5 months ago srai is l* instruction type. There's a funct7 included in the upper bits.         Be very careful. good comment         1                                                                        |

| #         | Anonymous Scale 5 months ago         ah got it.         helpful!                                                                                                                                                                  |

| Rep       | ly to this followup discussion                                                                                                                                                                                                    |

| Anon      | d O Unresolved @2128_f10 (c)<br>ymous Poet 5 months ago<br>Final O4 5 where did this equation 1/(25ps) come from and how did we get 40Gbz 2                                                                                       |

|           | <ul> <li>Final-Q4.5, where did this equation 1/(25ps) come from, and how did we get 40Ghz ?</li> <li>4.5 (2 points) What is the maximum allowable clock frequency for this circuit to function properly, in gigahertz?</li> </ul> |

|           | Solution: 40 GHz<br>1 / (25 ps) = 40 GHz                                                                                                                                                                                          |

# helpful! 0 Peyrin Kao 5 months ago Frequency is the inverse of period. If one clock tick takes 25 ps, or $25 \times 10^{-12}$ seconds, then in one second, there are $\frac{1}{25 \times 10^{-12}} = \frac{1}{25} \times 10^{12} = 0.04 \times 10^{12} = 40 \times 10^9$ clock cycles, which is 40 GHz. good comment 0 Reply to this followup discussion

### Resolved O Unresolved @2128\_f11 😔

Anonymous Calc 5 months ago

Su21 1.10.A (practice final on PrarieLearn)

Lecture 24 slide 53 says polling should be used for keyboards and this question says interrupts should be used. Am I misunderstanding the question or is this inconsistent?

# Interrupts vs Polling

rter Science 61C Spring 20

|                                   | Interrupts                                                                                              | Polling                                                                                                                         |

|-----------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| If no I/O activity                | No wasted cycles                                                                                        | Lots of wasted cycles                                                                                                           |

| If lots of I/O activity           | Expensive - saving/restoring state                                                                      | Less expensive - only poll<br>when we are already context<br>switching                                                          |

| Better suited for events that are | <ul> <li>asynchronous (unsure when<br/>event will occur)</li> <li>urgent</li> <li>infrequent</li> </ul> | <ul> <li>synchronous (occurs at fixed intervals)</li> <li>not urgent</li> <li>frequent (majority of polls are a hit)</li> </ul> |

| Examples                          | Disk                                                                                                    | Keyboard, mouse                                                                                                                 |

### PF1.10. Potpourri

## PART A (2 pts.)

We want a CPU to process input from a keyboard. Which technique should we use to process incoming data?

(a) DMA

👘 (b) Polling 🔀

(c) Interrupts

(d) A mix of polling and interrupts

### helpful! 0

### **Nicholas Weaver** 5 months ago

This is one of those "it gets complicated" things. IN an ideal world we probably would actually want interrupts for keyboards due to the low data rate. But the technology we use for keyboards does not actually support interrupts! So instead its polling.

Overall the Polling/Interrupt distinction is really really messy.

Low data rate the ideal would actually be interrupts, but we don't have interrupts on USB ("interrupt" devices in USB speak literally must be polled!). But the rate is low enough that we can shove the polling into the timer interrupt so the overhead for polling in practice becomes very low.

High data rates you want to use interrupts to start/end the transaction through DMA, but if you need to process it as it comes in (e.g. network packets in high performance networking) you'll switch to polling because interrupts in practice are a huge overhead, as it effectively wipes out all the caches!

good comment 0

Anonymous Calc 5 months ago

Thanks, that's interesting. But what should I answer if this question comes up on the test?

Nicholas Weaver 5 months ago

Uhh, scream that Nick said it won't because the answer is properly "Its Complicated"? good comment 6

Reply to this followup discussion

```

Resolved O Unresolved

@2128 f12 🗇

Anonymous Poet 5 months ago

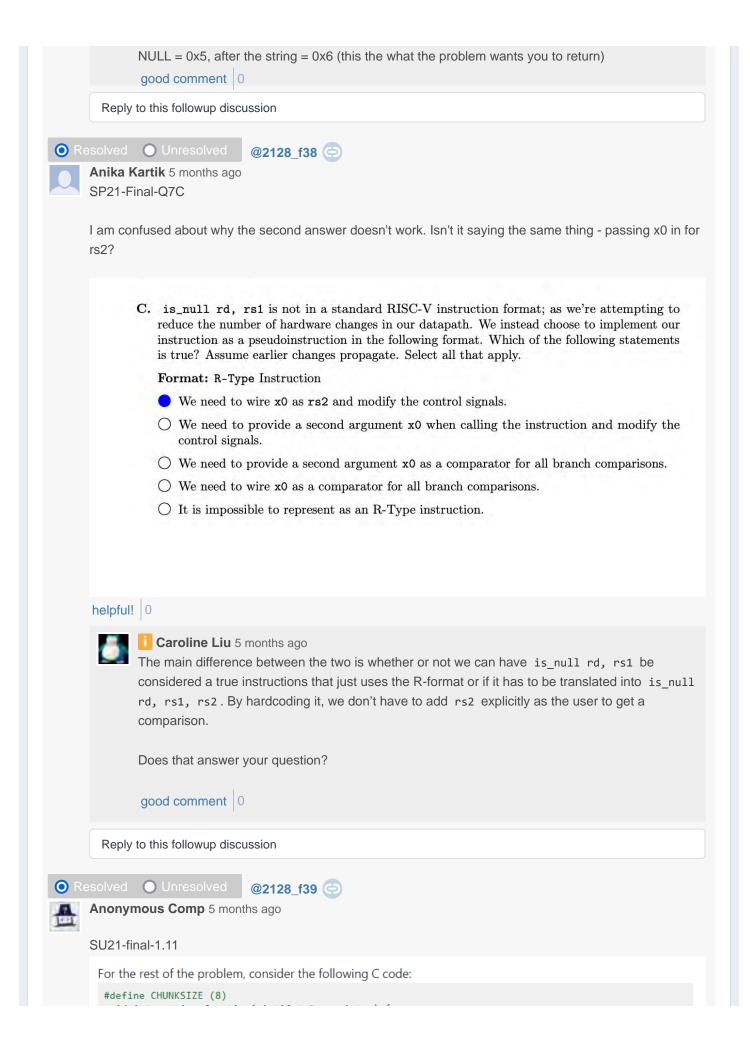

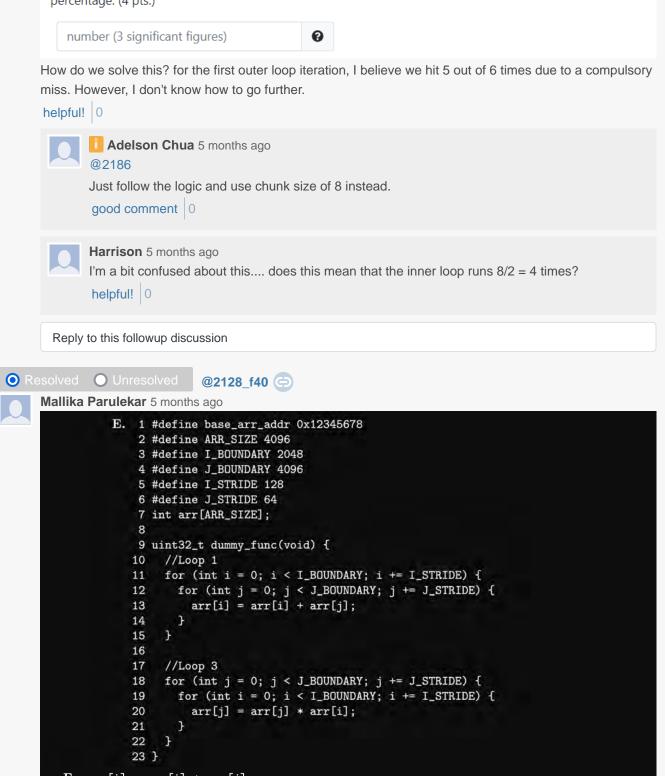

E. 1 #define base_arr_addr 0x12345678

2 #define ARR_SIZE 4096

3 #define I_BOUNDARY 2048

4 #define J BOUNDARY 4096

5 #define I_STRIDE 128

6 #define J_STRIDE 64

7 int arr[ARR_SIZE];

8

9 uint32_t dummy_func(void) {

10 //Loop 1

11 for (int i = 0; i < I_BOUNDARY; i += I_STRIDE) {</pre>

for (int j = 0; j < J_BOUNDARY; j += J_STRIDE) {</pre>

12

13

arr[i] = arr[i] + arr[j];

}

14

15 }

16

17

//Loop 3

18

for (int j = 0; j < J_BOUNDARY; j += J_STRIDE) {</pre>

for (int i = 0; i < I_BOUNDARY; i += I_STRIDE) {</pre>

19

arr[j] = arr[j] * arr[i];

20

21

7

}

22

23 }

```

am generated for cs61c@berkeley.edu

#### F. arr[i] = arr[i] + arr[j]

47/48

Ther outer loop executes 16 times and the inner loop per round executes 64 times. Because the accesses only happen in the inner loop, we can tally the HR for that first and then see how the outer accesses affect the HR. For the first inner iteration, we see we have a miss on the arr[0] read, then a hit on arr[1] and on the arr[0] write. For the next iteration, we get a arr[0] read and write. The next arr[j] is where accesses become tricky; we're stepping by 64 \* 4B =256B; this is larger than one block which means every subsequent arr[j] access will be a miss for one outer iteration. Thus, for the first outer iteration, our overall HR is 2/3. On the next outer iteration however, we notice that the entirety of the array can fit in the cache without conflicts. Because our I\_STRIDE is larger than J\_STRIDE, we know every future arr[i] access will have already had a compulsory miss by arr[j] in previous iterations and because nothing is evicted, we have a HR of 1 for all future access. This gives us a total of: HR = 2/3 \* 1/16+ 3/3 \* 15/16 =47/48. NOTE: the fact our array is 4-way does not affect us here because despite our 128B jumps in accesses, we have  $2^{11}$  sets available to us which means we won't fill up the first way in each set before we fill the second way. Because we only have 2 nested loops with two access patterns, nothing will get kicked out in each set for another access pattern.

1

The entire array can fit in memory. Because the access pattern is effectively the same, all accesses are hits.

#### SP21-FinalQ2

I'm confused how we get 47/48, I see that for the first inner iteration, we have 2/3, since arr[j] will always be a compulsory miss, but why would we not have miss anything in 2nd to last outter iteration? I understand what it says about getting hit becuase arr[j] already accessed it, but I don't understand how I\_stride larger than J\_stride comes into play here.

Also, for G, how can hit rate be one? The first access should always be a compulsory miss right? helpful! 0

Adelson Chua 5 months ago

Write the consecutive memory accesses please.

For i = 0, all iterations of the inner loop will always be 2/3 hit rate. There are 16 total iterations of the outer loop. The other 15 iterations will be all hits because the first iteration already committed the compulsory misses. That's why there's the equation  $2/3 \times 1/16 + 15/16 = 47/48$ .

For G, this loop happens right after the first loop, where the cache has been loaded already. good comment 0

9

|             | I know this doesn't affect the answer. I have a question that, what's the intuitive that the set wor<br>be full and some blocks are evicted? Is that just because there are only 2^14 B integers, and ou<br>cache is 2^19B big?<br>helpful!                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Adelson Chua 5 months ago<br>Yeah 2^11 is probably a typo. 2^10 is logical.                                                                                                                                                                                                                                                                                                                                           |

|             | Is that just because there are only 2^14 B integers, and our cache is 2^19B big?<br>Essentially yes. The cache fits the array, no replacements needed.<br>good comment 0                                                                                                                                                                                                                                              |

| <del></del> | Anonymous Scale 5 5 months ago<br>Are all the arr[j] entries in separate cache blocks? How do we know there are never any conflict<br>misses?<br>helpful! 0                                                                                                                                                                                                                                                           |

|             | Adelson Chua 5 months ago<br>At this point, it might be better to write out the consecutive addresses, split them into T/I/O, and<br>check what the corresponding Index would be for every access.<br>You can start with array[0] = 0x00000000, then go from there. Iterate over the loop, take note of<br>the stride length and see the consecutive addresses and how will they go into the cache.<br>good comment 0 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Rep         | / to this followup discussion                                                                                                                                                                                                                                                                                                                                                                                         |

| Resolve     | O Unresolved @2128_f13 (=)                                                                                                                                                                                                                                                                                                                                                                                            |

| _           | mous Poet 5 months ago                                                                                                                                                                                                                                                                                                                                                                                                |

| 2           | (d) (2.0 pt) What is the overall hit rate? Leave your answer as a fully simplified fraction.                                                                                                                                                                                                                                                                                                                          |

| 32 of       | 1/2                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | 1/2                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | The pattern above continues and repeats for all 8 blocks, giving us a $50\%$ HR.                                                                                                                                                                                                                                                                                                                                      |

|             | (e) (2.0 pt) What fraction of misses are coherency misses? Leave your answer as a fully simplified fraction.                                                                                                                                                                                                                                                                                                          |

|             | 3/4                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | Out of the 4 misses in each "access pattern block", 1 is compulsory, while the other 3 are coherency misses, so 75% of the overall misses.                                                                                                                                                                                                                                                                            |

|             | (f) (1.0 pt) In total, how many times did we need to go to main memory to write-back?                                                                                                                                                                                                                                                                                                                                 |

|             | 0                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | As the array fits perfectly into the cache, we never need to evict an block and write-back, so 0.                                                                                                                                                                                                                                                                                                                     |

|             | (g) (2.0 pt) We want to avoid all the coherency misses, so we look to see if we can rewrite our code to<br>optimize for cache performance. Which of the following methods will lead to a higher HR than that from<br>the interleaved accesses?                                                                                                                                                                        |

|             | $\Box$ None of the other options                                                                                                                                                                                                                                                                                                                                                                                      |

|             | Letting processor 0 start and finish, then processor 1 starts and finishes                                                                                                                                                                                                                                                                                                                                            |

|             | Letting processor 1 start and finish, then processor 0 starts and finishes                                                                                                                                                                                                                                                                                                                                            |

|             | Both of these approaches would be better, since then there would be no coherency misses during the first<br>processor's execution (load in the block, then hit on the other 3 WRW, so 75% HR). Then, the second<br>processor would begin, but instead of compulsory missing, just coherency miss, but get the same HR                                                                                                 |

Su20-Final Q6, why would writback be 0? What does it mean by array fits into the cache perfectly?

helpful! 0

|       | Adelson Chua 5 months agoArray length is 32 ints = 128 bytes. The cache size is 128 bytes as given.good comment0                                                                                                                                                                                                                                                                                                                                    |    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| \$    | Anonymous Poet 5 months agoBut at the end, do we need to evict all cache lines from cache and writeback to main memory?helpful!0                                                                                                                                                                                                                                                                                                                    |    |

|       | Adelson Chua 5 months agoWhat do you mean by 'at the end'? End of what?It is just saying that given the problem at hand, there's no need for cache evictions which leads<br>main memory write.good comment0                                                                                                                                                                                                                                         | to |

| Reply | y to this followup discussion                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|       | O Unresolved @2128_f14 (c)<br>mous Gear 5 months ago<br>for cs61c@berkeley.edu 10                                                                                                                                                                                                                                                                                                                                                                   |    |

| н     | 1. NOTE: for all parts, assume changes propogate unless otherwise stated.<br>As we're working on running the code snippet, we realise we want to run different instances of the same code. We choose to employ virtual memory on our memory space. We have 4 GiB of virtual memory and 16 MiB of physical memory mapped with a single level page table with a page size of 4 KiB. We choose to store 8 bits of metadata with each page table entry. |    |

1024

NOTE: because we did not specify alignment for the system, if you solved for a byte-aligned system, you will get the points for 768 pages.

Can someone help me with this question in Sp 21? I can't understand how they got this. I tried adding up the bits of the VPN and PPN as well as the metadata, then multiplying by 64.

helpful! 0

$\bigcirc$

**Adelson Chua** 5 months ago page offset = 12 bits VPN = 32-12 = 20 bits PPN = 24-12 = 12 bits page table entry = 8 (metadata) + 12 (PPN) = 20 bits Now we can either treat this as 3 bytes (if byte-aligned) or 4 bytes (if word-aligned) If byte-aligned:

page table size =  $2^{20}$  (number of page table rows, dependent on VPN) \* 3 = 3,145,728 (if byte-aligned)

how many pages the page table takes? page table size / page size = 3,145,728/(2^12) = 768

If word-aligned:

```

page table size = 2^{20} (number of page table rows, dependent on VPN) * 4 = 2^{22} how many pages the page table takes? page table size / page size = 2^{22}/2^{12} = 2^{10} = 1024

```

This is somewhat similar to the homework problem. You only need to find how large the page table entry is.

... Now where did you get 64?

good comment 0

Anonymous Calc 3 5 months ago

Can you explain this sentence? I'm very confused

Now we can either treat this as 3 bytes (if byte-aligned) or 4 bytes (if word-aligned)

### helpful! 0

|  | 4 |

|--|---|

Adelson Chua 5 months ago 20 bits is not divisible by 8 (a byte). So we round up to the nearest byte. 24 bits = 3 bytes.

If word-aligned it should be divisible by 32 bits always. So in this case, 32 bits = 4 bytes. good comment  $\begin{vmatrix} 0 \end{vmatrix}$

Reply to this followup discussion

Resolved O Unresolved @2128\_f15

Anonymous Atom 2 5 months ago SP21-Final-Q2B

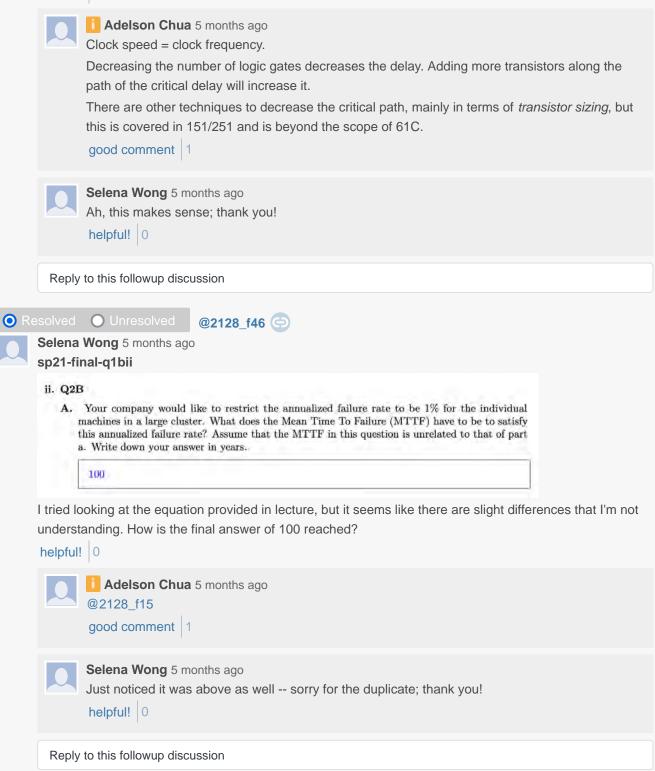

### ii. Q2B

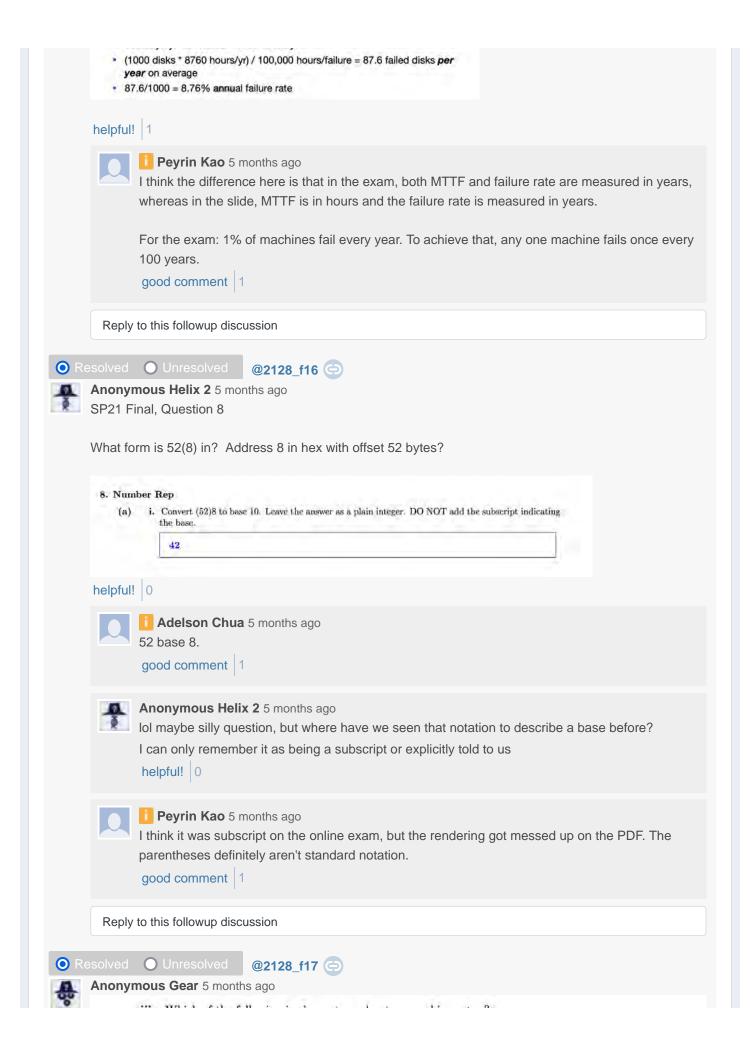

A. Your company would like to restrict the annualized failure rate to be 1% for the individual machines in a large cluster. What does the Mean Time To Failure (MTTF) have to be to satisfy this annualized failure rate? Assume that the MTTF in this question is unrelated to that of part a. Write down your answer in years.

100

Can someone help me with how we get 100? I tried using the following but it does not seem correct.

- Another is average number of failures per year: Annualized Failure Rate (AFR)

- E.g., 1000 disks with 100,000 hour MTTF

- 365 davs/vr \* 24 hours = 8760 hours/vr

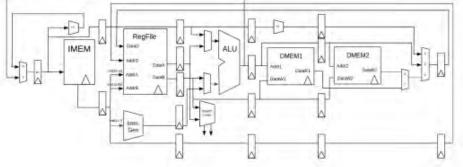

- III. Which of the following is always true about our caching setup?

- Assembly with few control-flow instructions will cause a high hit rate for Cache A.

- O The AMAT for Cache A and Cache B will be the same since the caches are identical.

- O Intended IMEM accesses will cause cache incoherence with intended DMEM accesses if the memory addresses are close.

- O Instuction and data accesses will cause both Cache A and Cache B's states to change for every access.

- $\bigcirc$  None of the above.

#### SP21 Final, Q7ciii:

Hi, Can someone explain to me why this is the answer? I thought the fourth one was the answer. Can someone please explain why it isn't? I thought the first one wasn't correct because I didn't think few control-flow instructions would affect caching.

helpful! 0

Adelson Chua 5 months ago

Few control flow instructions allow you to maximize spatial locality of Cache A leading to high hit rates.

I'm not sure what 'states' are that is being referred to at the fourth option.

good comment 0

Anonymous Atom 2 5 months ago

Could you also explain if this is the case, why subquestion 3 in the same question part B would not select option 4?

helpful! 0

### **Adelson Chua** 5 months ago

Because in that case, the cache is shared between instruction and data. If you are writing a lot of data, there might be cache block replacements going on which can evict blocks intended for instructions. Thus, it is not guaranteed that we are getting high hit rates in that scenario.

good comment 0

Anonymous Scale 5 months ago what is a "control flow" instruction? helpful!

Adelson Chua 5 months ago Branches. Jumps.

good comment 1

Reply to this followup discussion

Resolved O Unresolved @2128\_f18 😔

Anonymous Poet 5 months ago

(a) Consider a system with 4 GiB of physical memory and 64 GiB of Virtual Memory. The page size is 4 KiB.

Recall that the page table is stored in physical memory and consists of PTE's, or page table entries. Please fully simplify your answer and leave it in decimal. Fully simplify your exponents down to decimal! Please round your decimal values to two places if needed (do not include unnecessary 0's).

i. (3.0 pt) If, for each PTE, we choose to also store 12 bits of metadata (e.g. permission bits, dirty bit), how many page table entries can we now store on a page?

1024

First we need to find the side of each PTE so we need to figure out how many bits of physical memory we need to have to address.  $\log_2(\frac{4GiB}{4KiB}) = \log_2(\frac{2^{32}}{2^{12}}) = 20bits$

Now we can calculate the size of each PTE: 20bits (number of physical pages)+12bits (metadata bits) = 32bits = 4Bytes

Then we need to find the size of a page: 4KiB = 4096Bytes

Then we divide: 4096Bytes/4Bytes = 1024

### SU20-MT2-Q1

I'm confused about the concpet of storing page table entries on a page, my understanding is that page table have PTE, and PTE map virtual pages to physical pages, and the page size correspond to the size of each page in virtual page and phyical page. For this question, I don't understand why we want to store page table entries on a page.

helpful! 0

Adelson Chua 5 months ago

But... this is how it works. This should have been covered in the lecture. Also, there is a similar problem like this in the homework.

Page tables are stored as pages in the main memory, just like data pages are stored as pages as well.

Lab 10 slides (uploaded in the lab specs) illustrate this concept following CAMERAs setup.

good comment 0

Reply to this followup discussion

Anonymous Calc 5 months ago

### SU21-FINAL-Q3

I don't remember anything about finite state machines, are they in scope?

### PART A (8 pts.)

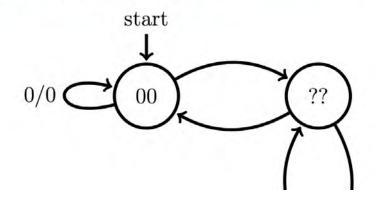

Fill in the transitions for the below FSM which represents the aforementioned 2-bit Gray code counter.

**Note:** state\_msb is the most significant bit of the counter, and state\_lsb is the least significant. That is, if the counter is at 10, then state\_msb is 1 and state\_lsb is 0.

| helpful         | ! 0                                                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Anonymous Calc 5 months ago         Sorry this is supposed to be question 3!!         helpful!       0                                                                 |

|                 | Adelson Chua 5 months agoOut of scope. We didn't cover this in the lecture.good comment1                                                                               |

| Reply           | v to this followup discussion                                                                                                                                          |

| Anony<br>FA21-F | O Unresolved @2128_f20 (5)<br>mous Scale 5 months ago<br>TINAL-Q1.9                                                                                                    |

| Q               | <pre>1.9 (1 point) We run the following code on two threads. 1 int y = 0; 2 int x = 10; 3 #pragma omp parallel 4 { 5 while(x&gt;0) 6 { 7 y = y+1; 8 x = x-1; 9 }</pre> |

Just curious, do we ever use Open MP with while loops in practice? It seems hard to divide the work amongst several hardware threads if we don't know how many iterations the while loop is going to run. My guess is some compilers can figure it out, but there are also cases of "while (keep looping until we get a result)" which may be more difficult for the compiler to figure out how many iterations the loop will run. helpful!

Adelson Chua 5 months ago

Typically, you use this in a for loop. #pragma omp parallel for is the best way to go, just like how

you did it in Proj 4.

Doing multi-threading on while loops are indeed hard and tricky, haha.

good comment 1

**Anonymous Mouse** 5 months ago So the answer is y = 1?

helpful! 0

Yes

Adelson Chua 5 months ago

good comment 0

Anonymous Poet 3 5 months ago

I'm confused why y can't be = 0. does x have to be read at the same time y was read before the for loop?

why can't thread 1 read x after thread 2 has run to completion and read x as 0? helpful! 1

Anonymous Poet 3 5 months ago what line is thread 1 sleeping/stopping at?

I dont get how thread 1 is executing the while loop but reading x as 0. helpful! 1

**Adelson Chua** 5 months ago

Oh, so you mean thread1 does not start at all while thread2 starts and runs to completion? That's a good question.

The solution assumes that when the threads spawn, they execute the *while* (x>0) statement at the same time allowing them to enter the loop.

Your claim is that thread1 does not start at all (does not execute any instructions). Not sure if that's possible.

I'll pull in some help. good comment 2

### **Justin Yokota** 5 months ago

If thread 1 doesn't start at all, then thread 2 fully executes, then thread 1 fully executes, then thread 1 would set y to 10, and thread 1 wouldn't change; the end result would be that y = 10 at the end.

The specific order of operations that yields a y=1 state is if thread 1 goes to sleep after reading y in line 7, but before writing back the value of y in line 7. In that case, the work done by thread 2 on y gets undone by setting y to 0+1 = 1, and since thread 2 set x to 0, thread 1 won't continue to the next iteration of the while loop. The end result would be y = 1.

|                 | good comment3Anonymous Comp 4 5 months agoFor this problem, after thread 1 reads y = 1, why does thread 2 get to read until completion? Ithough for pragma omp parallel, the stuff within the brackets from lines 4-10 get copied onto botthreads, and both threads individually complete the loophelpful!                                                                             |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Adelson Chua 5 months ago<br>But they are sharing the same x and y variable (those are declared outside the pragma), so one<br>thread can modify it and the other thread can see that modification. x and y are not private.<br>The execution of the threads are also non-deterministic. There's no guarantee that they start at<br>the same time, at the same rate.<br>good comment 1 |

| Reply           | v to this followup discussion                                                                                                                                                                                                                                                                                                                                                          |

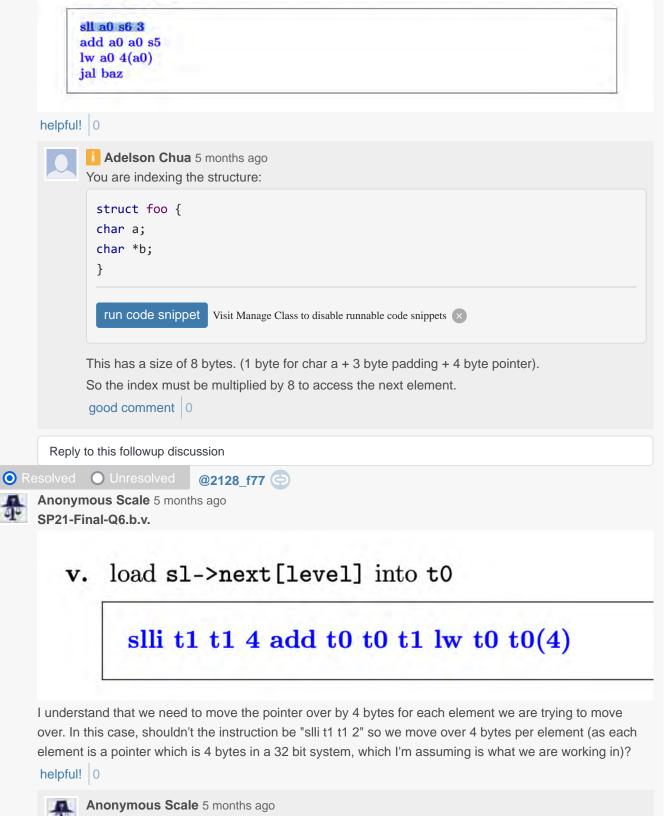

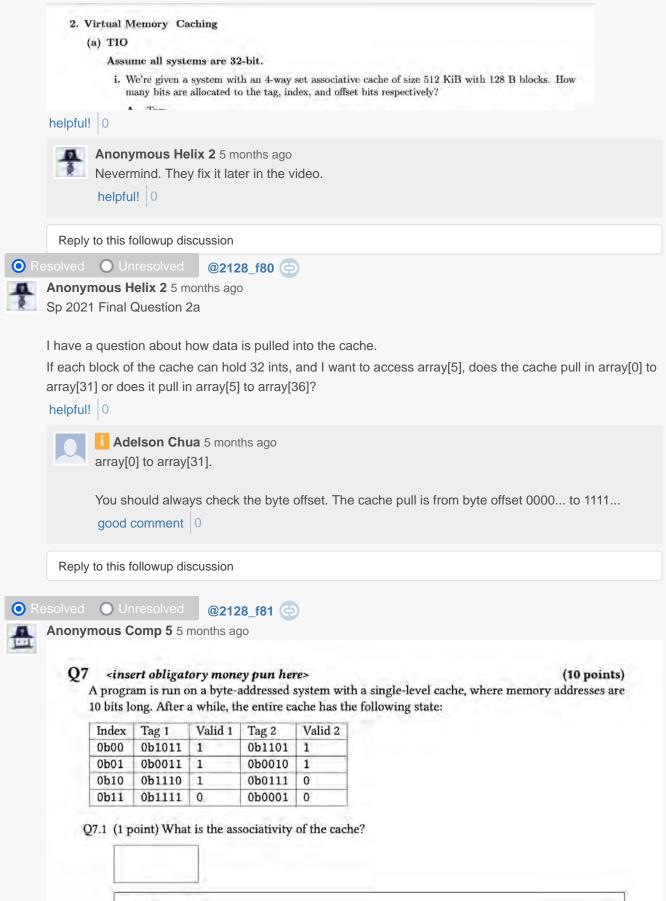

| Is this a       | Question 6b<br>a typo? I thought the syntax was always offset(mem location/register)                                                                                                                                                                                                                                                                                                   |

|                 |                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.              | Load find into a0                                                                                                                                                                                                                                                                                                                                                                      |

|                 | lw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into a1.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0                                                                                                                                                                                                  |

|                 | lw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into a1.         The RISC-V code for that would be (fill in based on comments):                                                                                                                                                                                                                          |

| н.              | lw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into a1.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0         lw t0 sp(8)         Load level into t1                                                                                                                                                   |

| н.              | Iw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into a1.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0         lw t0 sp(8)                                                                                                                                                                              |

| н.<br>ш.        | lw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into a1.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0         lw t0 sp(8)         Load level into t1                                                                                                                                                   |

| н.<br>ш.        | lw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into a1.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0         lw t0 sp(8)         Load level into t1         lw t1 sp(4)                                                                                                                               |

| н.<br>ш.        | lw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into al.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0         lw t0 sp(8)         Load level into t1         lw t1 sp(4)         load sl->next into t0         lw t0 t0(4)                                                                             |

| и.<br>ш.<br>iv. | lw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into al.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0         lw t0 sp(8)         Load level into t1         lw t1 sp(4)         load sl->next into t0         lw t0 t0(4)                                                                             |

| и.<br>ш.<br>iv. | Iw a0 sp(0)         The next thing we need to do is get sl->next[level]->data into al.         The RISC-V code for that would be (fill in based on comments):         Load sl into t0         Iw t0 sp(8)         Load level into t1         Iw t1 sp(4)         hoad sl->next into t0         Iw t0 t0(4)         I delson Chua 5 months ago         Yeah, most likely a typo.        |

|    | Reply to this followup discussion                                                                    |

|----|------------------------------------------------------------------------------------------------------|

| Re | esolved O Unresolved @2128_f23 🕞                                                                     |

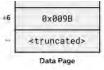

|    | Anonymous Gear 2 5 months ago                                                                        |

|    | I'm a bit confused as to how the last three questions of Part C in the Summer 2021 Practice Final on |

|    | Prairie Learn are TLB misses and a page fault respectively.                                          |

|    | ii) 0x00400C4B                                                                                       |

|    | 1) 0200400046                                                                                        |

|    | (b) TLB miss but page table hit                                                                      |

|    |                                                                                                      |

|    |                                                                                                      |

|    | iii) 0x0000764                                                                                       |

|    |                                                                                                      |

|    | (a) TLB hit                                                                                          |

|    |                                                                                                      |

|    | iv) 0x000006E                                                                                        |

|    |                                                                                                      |

|    | (b) TLB miss but page table hit                                                                      |

|    |                                                                                                      |

|    |                                                                                                      |

|    | V) 0x00400FAE                                                                                        |

|    |                                                                                                      |

|    | (b) TLB miss but page table hit                                                                      |

|    |                                                                                                      |

|    | vi) 0x00016A7                                                                                        |

|    |                                                                                                      |

|    | (c) Page fault                                                                                       |

|    |                                                                                                      |

|    |                                                                                                      |

|    | $\sim$                                                                                               |

|    | at a b a b a b a b a b a b a b a b a b a                                                             |

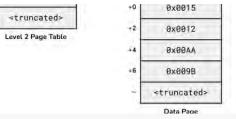

|    | +0 0x8013 +2 0x0012                                                                                  |

|    | +2 0×8017 +4 0×6000                                                                                  |

|    | +4 0x6542 +6 0x0037                                                                                  |

|    | +6 0x8444                                                                                            |

|    | +2 By B74                                                                                            |

|    | +2 0x0074<br>+4 0x8009<br>+2 0x0000                                                                  |

|    | +6 0x2003<br>+6 0x7983                                                                               |

|    | 0x1080 +0 0x1031 +6 0x0082                                                                           |

|    | Base Register +2 8x8017                                                                              |

|    | Level 1 Page Table = Skotty = <truncated></truncated>                                                |

I understand that the first two will be TLB misses as the TLB starts off empty, but then after the next should be a TLB hit as it has the same PTE as the very first hexadecimal value checked in this problem. Due to this intuition, I was under the impression that the next hexadecimal value being checked would also be a TLB hit as it has the same PTE as the previous value check. My next question might be how exactly do we determine what PTE value is within the given hexadecimal? I assumed that the last 4 bits are the offset, while the rest are the PTEs split amongst 3 Page Table levels. I'm just confused how (iv) and (v) are TLB misses, and how (vi) is a page fault when they all have their upper 5 bits in the TLB.

### helpful! 0

Adelson Chua 5 months ago

This is only a 2-level page table...

Given my solution on the follow-up below. Can you follow the correct procedure and write out the corresponding VPN - PPN translations for every memory access?

We need to correctly identify the VPNs for the different addresses.

good comment 0

Anonymous Calc 2 5 months ago

For vi for this question, is it a page fault because the level 2 page table or ppn that we receive has no arrow to a data page?

helpful! 0

Adelson Chua 5 months ago

The valid bit is 0.

good comment 0

Reply to this followup discussion

## Resolved O Unresolved @2128\_f24 (=)

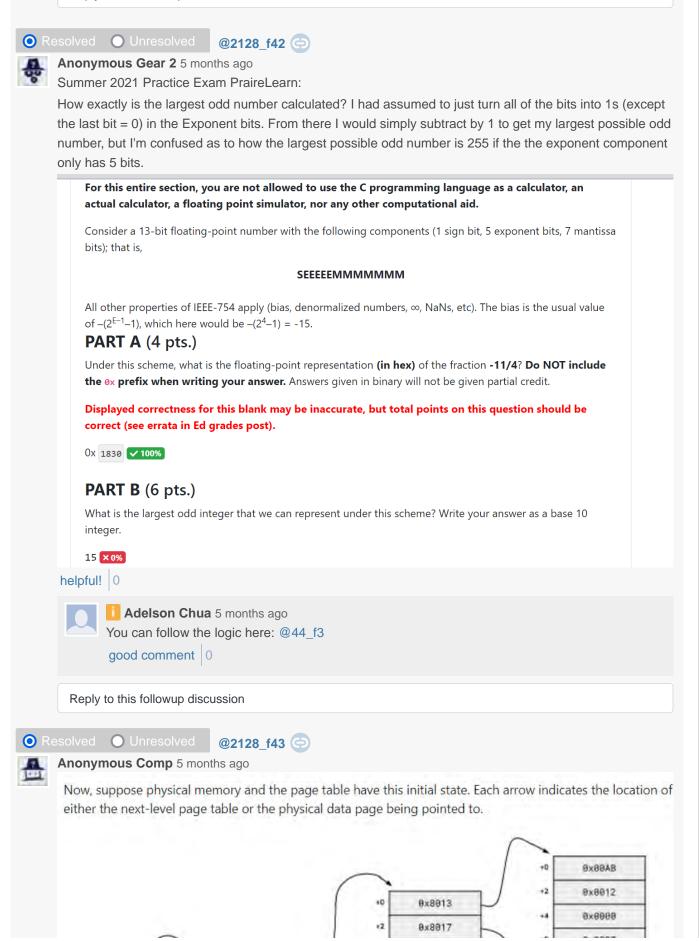

Anonymous Gear 2 5 months ago

I'm not quite sure how to solve part B of the Summer Final Practice Exam on Prairie Learn:

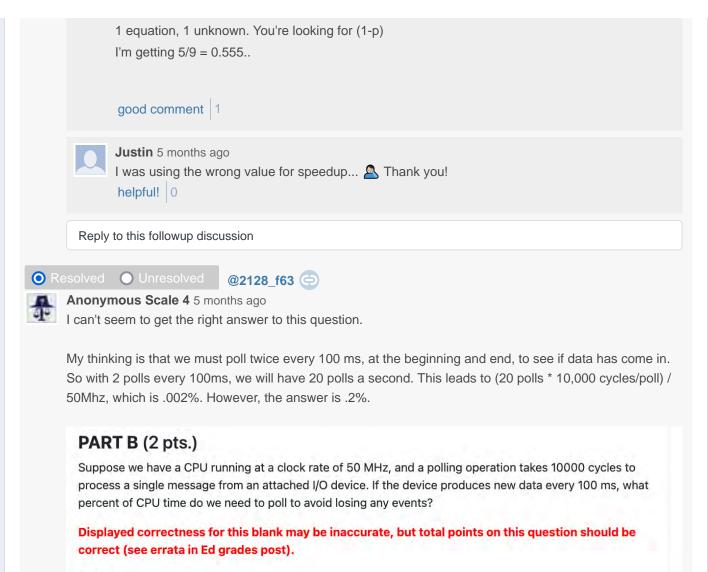

### PART B (3 pts.)

What physical address does virtual address 0x0000041A map to? Write your answer in hexadecimal, without the leading 0x, or write N/A if this does not map to a valid physical address.

Displayed correctness for this blank may be inaccurate, but total points on this question should be correct (see errata in Ed grades post).

0x 9c1A

To solve this, I originally decided to split up the given hexadecimal value into its respective parts: the upper

4 bits are the PTEs, while the last 4 bits represent the offset. I used the bits I assumed to be the PTEs to get to the desired page, and then copied the four bits as the first four bits of my desired output, and I simply added the offset as the last 4 bits (I got 00AB041A). So I'm a bit confused how the actual answer is just 4 bits.

helpful! 0

| · · |                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Adelson Chua 5 months agoThis question is somewhat similar to the homework question, only with different offset bits (this one is 11 bits only).0x0000041A (VPN is 20 bits + offset is 11 bits = 31 bits)000 0000 0000 0000 0100 0000 100 0001 1010 (This is the virtual address in 31-bit binary)Partitioning:000000000 0000 0000 0000 10000011010VPN1VPN2offset |

|     | Check the table.<br>VPN1 = VPN2 = 0. This points to the entry 0x8013. @2187 (take note of this)<br>PPN is part of the page table entry, and is only 11 bits long (the last 11 bits of the page table entry).                                                                                                                                                      |

|     | Last 11 bits is 0x013 => 000 0001 0011<br>Now, combine:<br>Physical address = PPN + offset<br>00000010011 10000011010<br>Regroup and rewrite to hex<br>00 0000 1001 1100 0001 1010<br><b>0x009C1A</b><br>The solution shows 0x9C1A which is also equivalent (PrairieLearn ignores leading zero for this<br>problem for some reason)<br>good comment 4             |

|     |                                                                                                                                                                                                                                                                                                                                                                   |

Reply to this followup discussion

### Resolved O Unresolved @2128\_f25 (=)

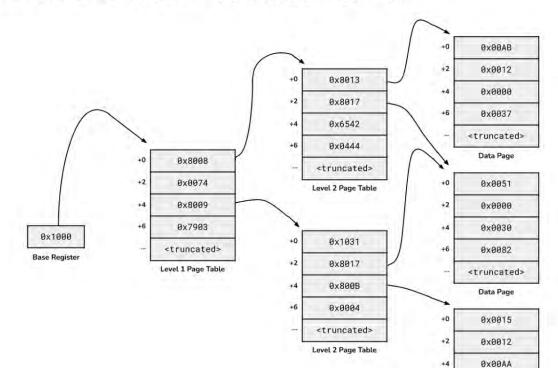

Junsang Yoon 5 months ago I don't understand FA2021 Q7

2: Miss; Our tag isn't in our index. This can either be compulsory or conflict, since we don't know if this block has been accessed before and ejected. This can't be a capacity miss, because there are still empty slots in our cache.

3: Miss; Our tag isn't in our index. This must be compulsory, because we still have an empty slot in this index. We only ever kick out a block when the cache is full, and only to replace that block with a new one; as such, we can't have kicked out a block while there is still empty space in the cache.

|      | Where is the empty space in the cache?         nelpful!       0                                                                                                                                                                                                                                                                                                                                                  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Adelson Chua 5 months ago<br>Check the given cache state. There are cache slots that have a valid bit of 0. That's the empty<br>space.<br>good comment 0                                                                                                                                                                                                                                                         |

|      | Junsang Yoon 5 months ago<br>aren't we accessing index 00 in the 2), which has both valid bits of 1?<br>helpful! 0                                                                                                                                                                                                                                                                                               |

|      | Adelson Chua 5 months ago<br>You look at the overall cache state when determining what type of miss it is.                                                                                                                                                                                                                                                                                                       |

|      | @1270_f6<br>If the address was in the cache, but isn't anymore (got evicted) and the cache is still not full:<br>Conflict miss                                                                                                                                                                                                                                                                                   |

|      | If the address was in the cache, but isn't anymore (got evicted) and the cache is full: Capacity miss                                                                                                                                                                                                                                                                                                            |