#### <u>EECS150 – Digital Design</u> <u>Lecture 2 – Combinational Logic</u> <u>Review and FPGAs</u>

January 19, 2012

John Wawrzynek Electrical Engineering and Computer Sciences University of California, Berkeley

http://www-inst.eecs.berkeley.edu/~cs150

Spring 2012

EECS150 lec02-logic-review-FPGAs

Page 1

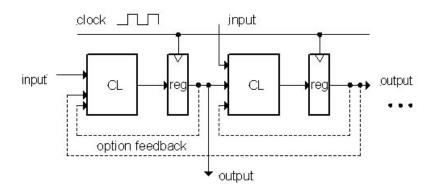

#### **General Model for Synchronous Systems**

- All synchronous digital systems fit this model:

- Collections of combinational logic blocks and state elements connected by signal wires. These form a directed graph with only two types of nodes (although the graph need not be bi-partite.)

- Instead of simple registers, sometimes the state elements are large memory blocks.

# <u>Outline</u>

- Review of three representations for combinational logic: truth tables, gate diagrams, algebraic equations

- Laws of Boolean Algebra

- Canonical Forms

- Boolean Simplification

- multi-level logic

- NAND/NOR Networks

- Field Programmable Gate Arrays (FPGAs) Introduction

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 3

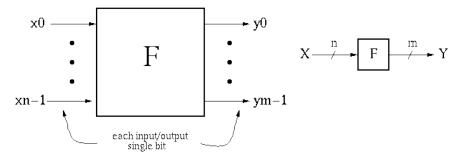

# **Combinational Logic (CL) Defined**

- y<sub>i</sub> = f<sub>i</sub>(x0,..., xn-1), where x, y are {0,1}.

Y is a function of only X.

- If we change X, Y will change immediately (well almost!).

- There is an implementation dependent delay from X to Y.

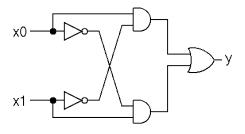

# CL Block Example #1

output 1 if either 0x $x_{0=1} \text{ or } x_{1=1}$ ⊷ У but not both x1

**Boolean Equation:**

$y_0 = (x_0 AND not(x_1))$ OR (not( $x_0$ ) AND  $x_1$ )  $y_{n} = x_{n}x_{1}' + x_{n}'x_{1}$

**Truth Table Description:**

Gate Representation:

How would we prove that all three representations are equivalent?

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 5

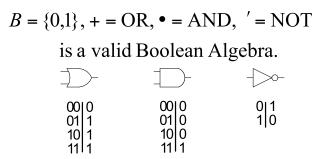

# **Boolean Algebra/Logic Circuits**

- Why are they called "logic circuits"? ٠

- Logic: The study of the principles of reasoning. •

- The 19th Century Mathematician, George Boole, developed a math. system (algebra) involving logic, Boolean Algebra.

- His variables took on TRUE, FALSE

- Later Claude Shannon (father of information theory) showed (in his Master's thesis!) how to map Boolean Algebra to digital circuits:

- Primitive functions of Boolean Algebra: ٠ a b AND

a b OR

0

00

01 1

10 1

11 1

Spring 2012

EECS150 - LecO2-logic-FPGA

00

01

10

0

0

0 11| 1

Page 6

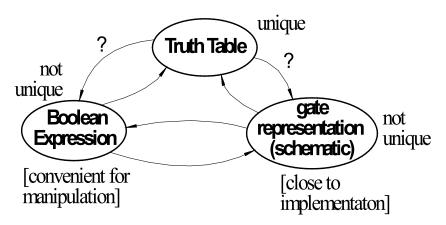

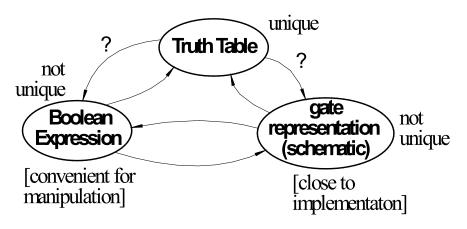

# **Relationship Among Representations**

\* Theorem: Any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using AND, OR, NOT.

How do we convert from one to the other?

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 7

# CL Block Example #2

| • 4-bit adder:                                        | Truth Table Representation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                                                       | a3 a2 a1 a0 b3 b2 b1 b0 r3 r2 r1 r0 c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| $A \xrightarrow{4} R$<br>add<br>$B \xrightarrow{4} c$ | 0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       1       0       0       1       0       0       0       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 |  |  |  |  |  |  |  |  |

| R = A + B,<br>c is carry out                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| In general: 2ª rows for n in                          | •<br>•<br>• • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

In general: 2<sup>n</sup> rows for n inputs. 256 rows! Is there a more efficient (compact) way to specify this function?

EECS150 - LecO2-logic-FPGA

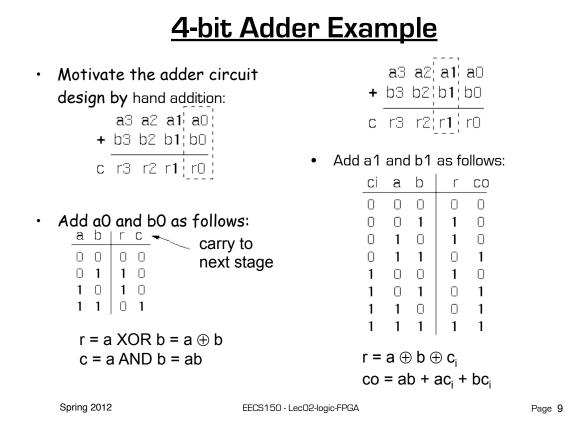

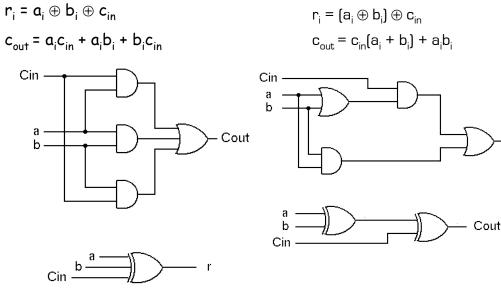

<u>4-bit Adder Example</u>

• In general:

$$\mathbf{r}_{i} = \mathbf{a}_{i} \oplus \mathbf{b}_{i} \oplus \mathbf{c}_{in}$$

$c_{out} = a_i c_{in} + a_i b_i + b_i c_{in} = c_{in}(a_i + b_i) + a_i b_i$

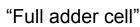

FA сO

a b ci

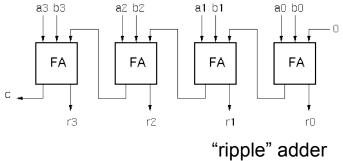

Now, the 4-bit adder: **a**3 b3 a2 b2 a1 b1

EECS150 - LecO2-logic-FPGA

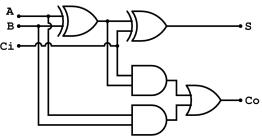

# 4-bit Adder Example

- Graphical Representation of FAcell

- Alternative Implementation (with 2-input gates):

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 11

Cout

# **Boolean Algebra**

Defined as:

Set of elements *B*, binary operators  $\{+, \bullet\}$ , unary operation  $\{'\}$ , such that the following axioms hold :

- 1. *B* contains at least two elements a, b such that  $a \neq b$ .

- 2. Closure : a, b in B,

- a + b in B,  $a \bullet b$  in B, a' in B.

#### 3. Communitive laws :

a + b = b + a,  $a \bullet b = b \bullet a$ .

4. Identities : 0, 1 in B

$a + 0 = a, \quad a \bullet 1 = a.$

5. Distributive laws:

$a + (b \bullet c) = (a + b) \bullet (a + c), \ a \bullet (b + c) = a \bullet b + a \bullet c.$

6. Complement :

$$a + a' = 1, a \bullet a' = 0.$$

#### Logic Functions

#### Do the axioms hold?

- Ex: communitive law: a+b = b+a?

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 13

# Some Laws of Boolean Algebra

Duality: A dual of a Boolean expression is derived by interchanging OR and AND operations, and Os and 1s (literals are left unchanged).

$\{F(x_1, x_2, ..., x_n, 0, 1, +, \bullet)\}^D = \{F(x_1, x_2, ..., x_n, 1, 0, \bullet, +)\}$

Any law that is true for an expression is also true for its dual.

```

Operations with 0 and 1:

1. x + 0 = x x * 1 = x

2. x + 1 = 1 x * 0 = 0

Idempotent Law:

3. x + x = x x = x

Involution Law:

4. [x']' = x

Laws of Complementarity:

5. x + x' = 1 x = x' = 0

Commutative Law:

6. x + y = y + x x = y = y

```

# Laws of Boolean Algebra (cont.)

| Associative Laws:<br>(x + y) + z = x + (y + z)                                                                               | x y z = x (y z)                       |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Distributive Laws:<br>x (y + z) = (x y) + (x z)                                                                              | x +(y z) = (x + y)(x + z)             |

| "Simplification" Theorems:<br>x y + x y' = x<br>x + x y = x                                                                  | (x + y) (x + y') = x<br>x (x + y) = x |

| DeMorgan's Law:<br>(x + y + z +)' = x'y'z'                                                                                   | (x y z)' = x' + y' +z'                |

| Theorem for Multiplying and Fac<br>(x + y) (x' + z) = x z + x' y<br>Consensus Theorem:<br>x y + y z + x' z = (x + y) (y + z) |                                       |

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 15

# <u>Proving Theorems via axioms of</u> <u>Boolean Algebra</u>

Ex: prove the theorem: x y + x y' = x

x y + x y' = x (y + y') distributive law

x (y + y') = x (1) complementary law

x(1) = x identity

x y + x' z = (x + y) (x' + z)

Ex: prove the theorem: X + X Y = X

x + xy = x1 + xy identity x1 + xy = x(1 + y) distributive law x(1 + y) = x(1) identity x(1) = x identity

#### **DeMorgan's Law** x y x' y' | (x + y)' x'y' (x + y)' = x' y'Exhaustive 0011 1 1 Proof 0110 0 0 Õ 1001 0 1100 Ó 0 (x y)' x' + y' хуху (x y)' = x' + y'Exhaustive 0011 1 1 Proof 0110 1 1 1001 1 1 1100 0 0

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 17

# **Relationship Among Representations**

\* Theorem: Any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using AND, OR, NOT.

How do we convert from one to the other?

# **Canonical Forms**

- Standard form for a Boolean expression unique algebraic expression directly from a true table (TT) description.

- Two Types:

- \* Sum of Products (SOP)

- \* Product of Sums (POS)

- <u>Sum of Products</u> (disjunctive normal form, <u>minterm</u> expansion). Example:

| minterms<br>a'b'c'<br>a'b'c<br>a'bc'<br>a'bc<br>ab'c' | a b c     f f'       0 0 0     0 1       0 0 1     0 1       0 1 0     0 1       0 1 0     0 1       0 1 1     1 0       1 0 0     1 0 | One product ( <b>and</b> ) term for each 1 in f:<br>f = a'bc + ab'c' + ab'c +abc' +abc |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| ab'c'<br>ab'c                                         | 10010<br>10110                                                                                                                         | f = a'bc + ab'c' + ab'c +abc' +abc<br>f' = a'b'c' + a'b'c + a'bc'                      |

| abc'<br>abc                                           | 1 1 0   1 0<br>1 1 1   1 0                                                                                                             |                                                                                        |

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 19

# **Canonical Forms**

• **<u>Product of Sums</u>** (conjunctive normal form, <u>maxterm</u> expansion). Example:

| abc  f f' |                                                        |

|-----------|--------------------------------------------------------|

| 00001     |                                                        |

| 00101     |                                                        |

| 01001     |                                                        |

| 01110     |                                                        |

| 10010     |                                                        |

| 10110     | One sum ( <b>or</b> ) term for each 0 in f:            |

| 11010     |                                                        |

| 11110     | f = (a+b+c)(a+b+c')(a+b'+c)                            |

| ·         | f' = (a+b'+c')(a'+b+c)(a'+b+c')                        |

|           | (a'+b'+c)(a+b+c')                                      |

|           | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Mapping from SOP to POS (or POS to SOP): Derive truth table then proceed.

#### **Algebraic Simplification Example**

Ex: full adder (FA) carry out function (in canonical form):

Cout = a'bc + ab'c + abc' + abc

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 21

# **Algebraic Simplification**

Cout = a'bc + ab'c + abc' + abc = a'bc + ab'c + abc' + abc + abc = a'bc + abc + ab'c + abc' + abc = (a' + a)bc + ab'c + abc' + abc= (1)bc + ab'c + abc' + abc= bc + ab'c + abc' + abc + abc= bc + ab'c + abc + abc' + abc= bc + a(b' + b)c + abc' + abc= bc + a(1)c + abc' + abc= bc + ac + ab(c' + c)= bc + ac + ab(1)= bc + ac + ab

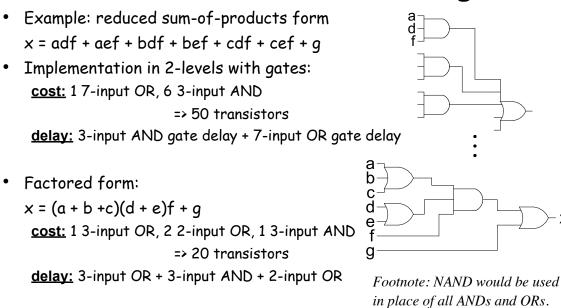

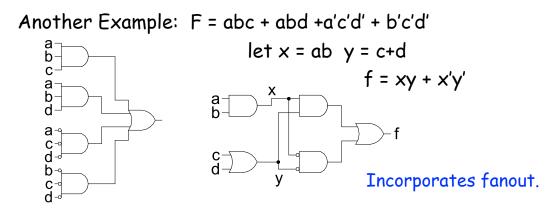

# **Multi-level Combinational Logic**

#### Which is faster?

In general: Using multiple levels (more than 2) will reduce the cost. Sometimes also delay. Spring 2012 EECS150 - Lec02-Jogic-FPGA Page 23

# **Multi-level Combinational Logic**

No convenient hand methods exist for multi-level logic simplification:

- a) CAD Tools use sophisticated algorithms and heuristics

- b) Humans and tools often exploit some special structure (example adder)

# Project platform: Xilinx ML505-110

## **FPGA** Overview

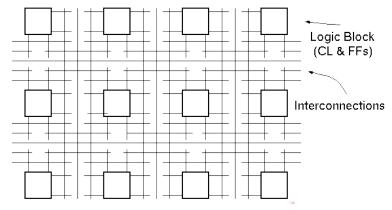

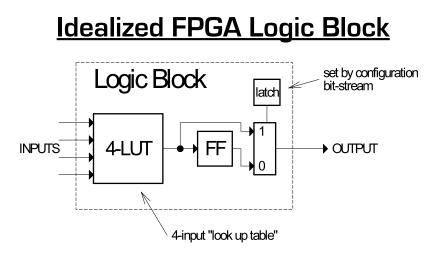

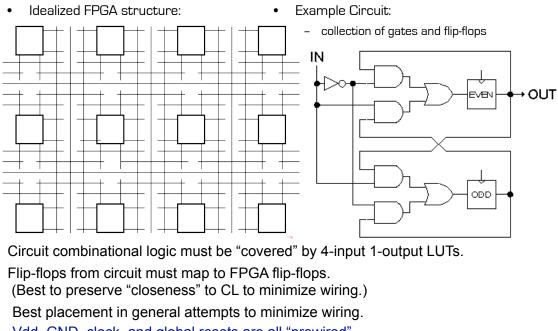

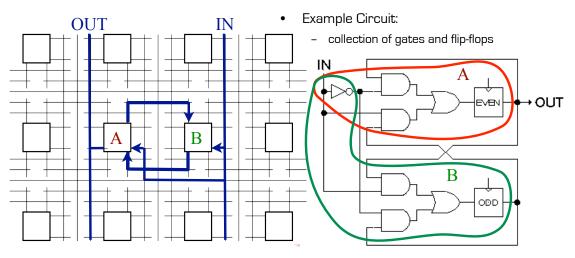

- Basic idea: two-dimensional array of logic blocks and flip-flops with a means for the user to configure (program):

- 1. the interconnection between the logic blocks,

- 2. the function of each block.

Simplified version of FPGA internal architecture:

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 29

#### Why are FPGAs Interesting?

- Technical viewpoint:

- For hardware/system-designers, like ASICs only better! "Tape-out" new design every few minutes/hours.

- Does the "reconfigurability" or "reprogrammability" offer other advantages over fixed logic?

- Dynamic reconfiguration? In-field reprogramming? Self-modifying hardware, evolvable hardware?

#### Why are FPGAs Interesting?

• Staggering logic capacity growth (10000x):

| Year Introduced | Device    | Logic Cells | "logic gate<br>equivalents" |

|-----------------|-----------|-------------|-----------------------------|

| 1985            | XC2064    | 128         | 1024                        |

| 2011            | XC7V2000T | 1,954,560   | 15,636,480                  |

FPGAs have tracked Moore's Law better than any other programmable device.

Spring 2012

EECS150 lec02-logic-review-FPGAs

Page 31

#### Why are FPGAs Interesting?

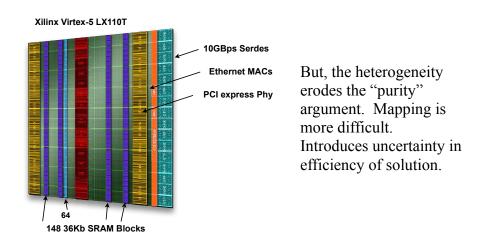

- Logic capacity now only part of the story: on-chip RAM, high-speed I/Os, "hard" function blocks, ...

- Modern FPGAs are "reconfigurable systems"

# FPGAs are in widespread use

# **User Programmability**

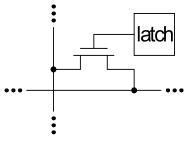

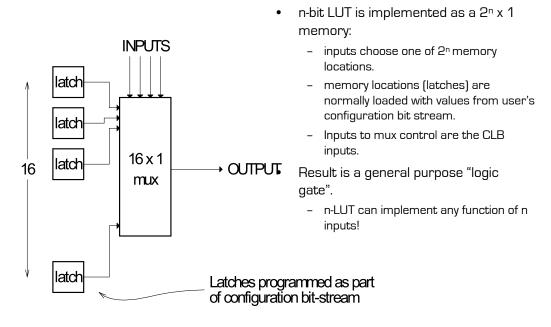

Latch-based (Xilinx, Altera, ...)

- + reconfigurable

- volatile

- relatively large.

- Latches are used to:

- 1. control a switch to make or break cross-point connections in the interconnect

- 2. define the function of the logic blocks

- 3. set user options:

- within the logic blocks

- in the input/output blocks

- global reset/clock

- "Configuration bit stream" is loaded under user control

# **Background (review) for upcoming**

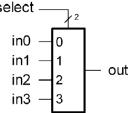

A <u>MUX</u> or multiplexor is a combinational logic circuit that chooses between 2<sup>N</sup> inputs under the control of N control signals.

• A <u>latch</u> is a 1-bit memory (similar to a flip-flop).

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 35

- 4-input look up table (LUT)

implements combinational logic functions

- Register

- optionally stores output of LUT

## **4-LUT Implementation**

Spring 2012

CS 150 - LecO2-logic-FPGA

Page 37

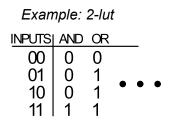

#### LUT as general logic gate

- An n-lut as a direct implementation of a function **truth-table**.

- Each latch location holds the value of the function corresponding to one input combination.

Implements any function of 2 inputs.

How many of these are there? How many functions of n inputs? Example: 4-lut

| INPUTS |                                       |

|--------|---------------------------------------|

| 0000   | F(0,0,0,0) < store in 1st latch       |

| 0001   | $F(0,0,0,1) \leq $ store in 2nd latch |

| 0010   | F(0,0,1,0) <                          |

| 0011   | F(0,0,1,1) <                          |

| 0011   |                                       |

| 0100   | •                                     |

| 0101   | •                                     |

| 0110   | •                                     |

| 0111   |                                       |

| 1000   |                                       |

| 1001   |                                       |

| 1010   |                                       |

| 1011   |                                       |

| 1100   |                                       |

| 1101   |                                       |

| 1110   |                                       |

| 1111   |                                       |

#### FPGA Generic Design Flow

**Design Entry**

Design

Implementation

- Design Entry:

- Create your design files using:

- · schematic editor or

- HDL (hardware description languages: Verilog, VHDL)

- Design Implementation:

- Logic synthesis (in case of using HDL entry) followed by,

- Partition, place, and route to create configuration bit-stream file

- Design verification:

- Optionally use simulator to check function,

- Load design onto FPGA device (cable connects PC to development board), optional "logic scope" on FPGA

- · check operation at full speed in real environment.

Spring 2012

CS 150 - LecO2-logic-FPGA

Page 39

Desian

Verification

#### **Example Partition, Placement, and Route**

Vdd, GND, clock, and global resets are all "prewired".

#### **Example Partition, Placement, and Route**

Two partitions. Each has single output, no more than 4 inputs, and no more than 1 flip-flop. In this case, inverter goes in both partitions.

Note: the partition can be arbitrarily large as long as it has not more than 4 inputs and 1 output, and no more than 1 flip-flop.

Spring 2012

CS 150 - LecO2-logic-FPGA

Page 41

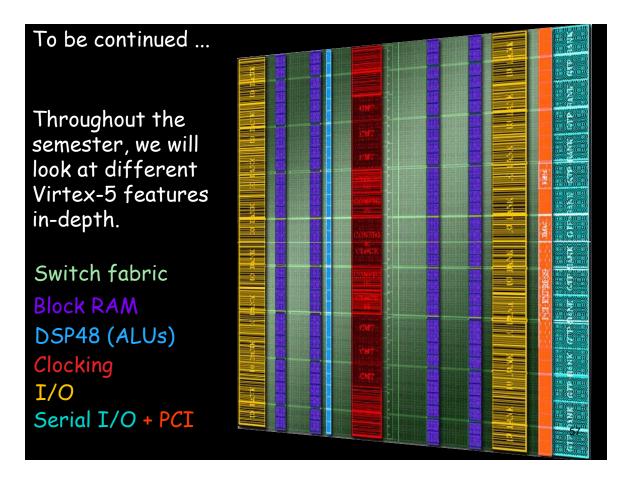

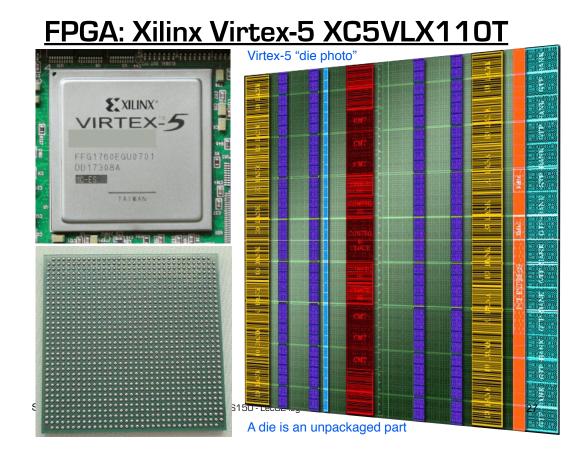

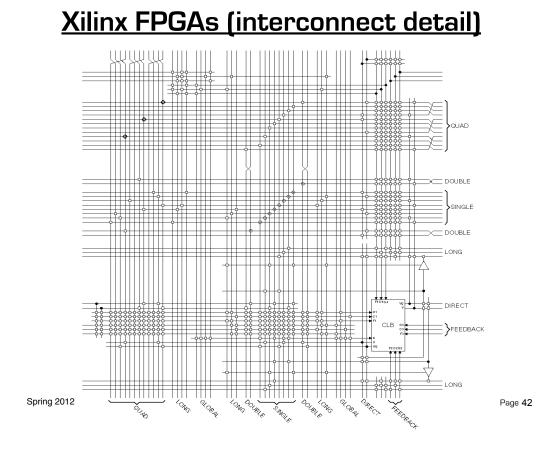

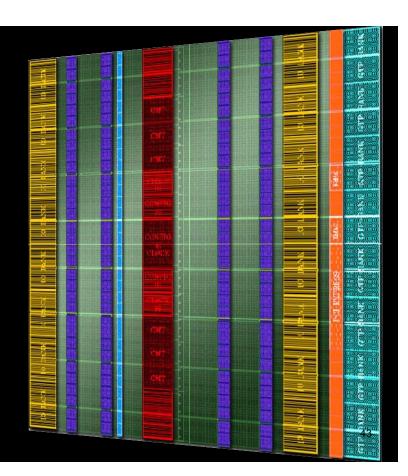

Colors represent different types of resources:

Logic Block RAM DSP (ALUs) Clocking I/O Serial I/O + PCI

A routing fabric runs throughout the chip to wire everything together.

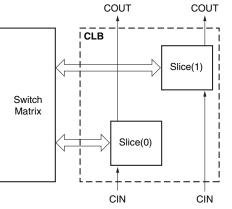

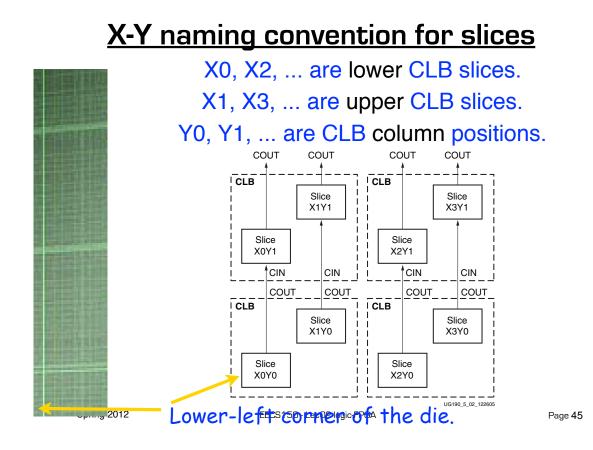

# **Configurable Logic Blocks (CLBs)**

Slices define regular connections to the switching fabric, and to slices in CLBs above and below it on the die.

Page 44

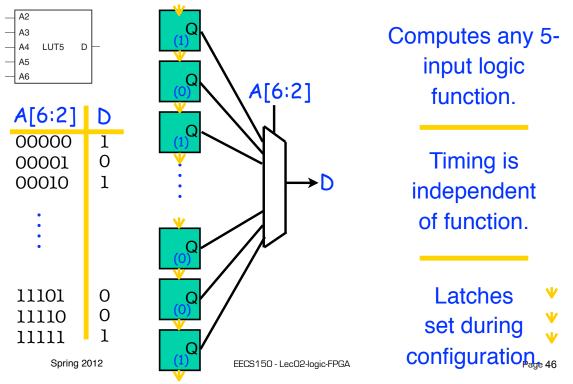

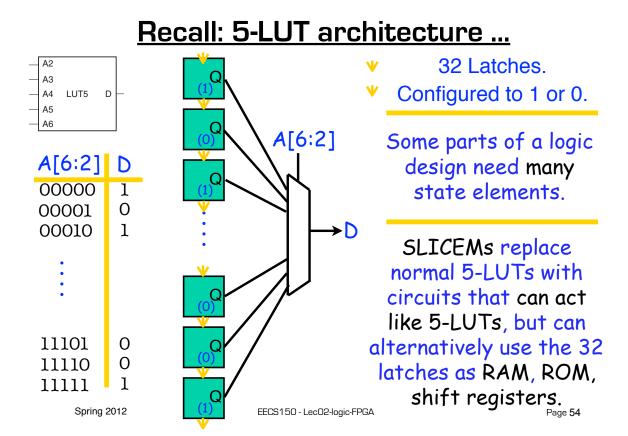

# Atoms: 5-input Look Up Tables (LUTs)

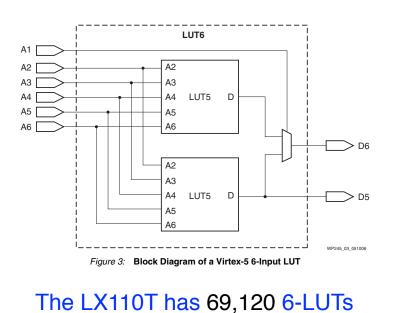

## Virtex-5 6-LUTs: Composition of 5-LUTs

6-LUT delay is 0.9 ns

Spring 2012

May be used as one 6-input LUT (D6 out) ...

... or as two 5-input LUTS (D6 and D5)

Combinational logic (post configuration) Page 47

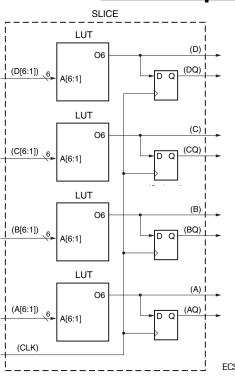

# The simplest view of a slice

EECS150 - LecO2-logic-FPGA

Four 6-LUTs

Four Flip-Flops

Switching fabric may see combinational and registered outputs.

An actual Virtex-5 slice adds many small features to this simplified diagram. We show them one by one ... ECS150-Lec02-logicFPGA Page 48

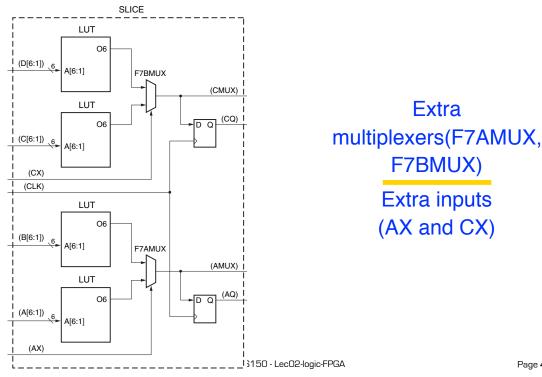

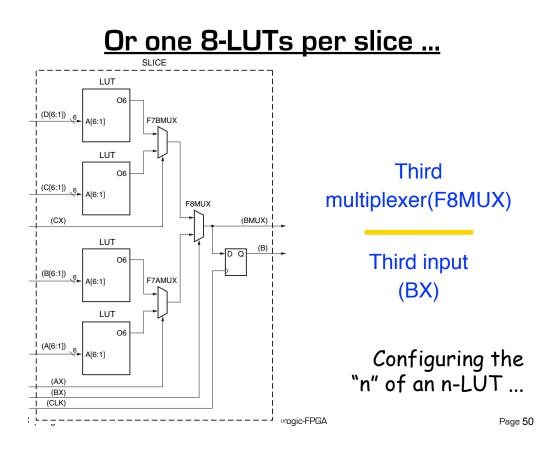

#### Two 7-LUTs per slice ...

Page 49

**Extra**

## Extra muxes to chose LUT option ...

From eight 5-LUTs ... to one 8-LUT.

Combinational or registered outs.

Flip-flops unused by LUTs can be used standalone.

Page 51

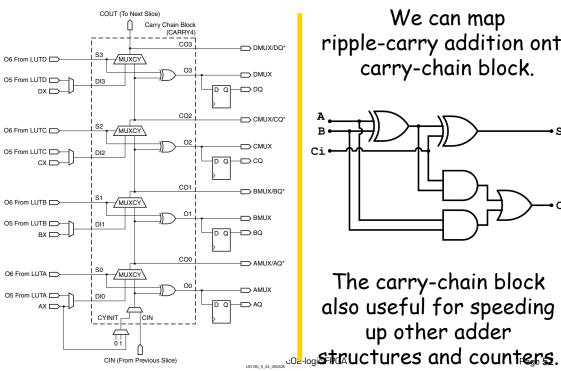

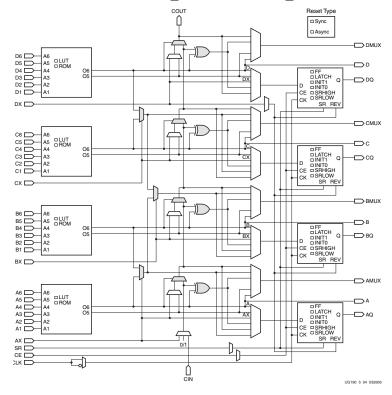

# Virtex 5 Verical Logic

We can map ripple-carry addition onto carry-chain block.

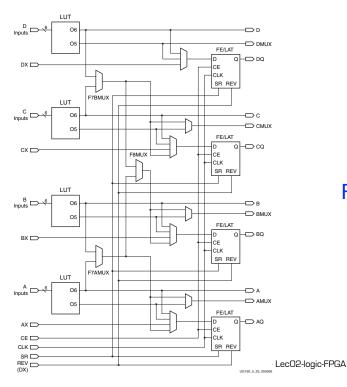

## Putting it all together ... a SLICEL.

The previous slides explain all SLICEL features.

About 50% of the 17,280 slices in an LX110T are SLICELs.

The other slices are SLICEMs, and have extra features.<sub>Page 53</sub>

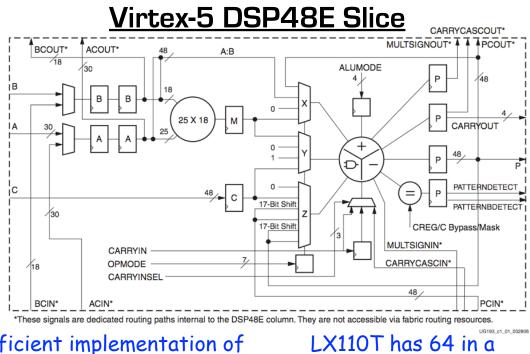

# Efficient implementation of LX110T has 64 multiply, add, bit-wise logical. single column.

Spring 2012

EECS150 - LecO2-logic-FPGA

Page 55

| Device     | Configurable Logic Blocks (CLBs) |                                   |                                |                                 | Block RAM Blocks     |       |             | PowerPC             | Endpoint |                              | Max RocketlO<br>Transceivers <sup>(6)</sup> |     | Total | Max                         |       |

|------------|----------------------------------|-----------------------------------|--------------------------------|---------------------------------|----------------------|-------|-------------|---------------------|----------|------------------------------|---------------------------------------------|-----|-------|-----------------------------|-------|

|            | Array<br>(Row x Col)             | Virtex-5<br>Slices <sup>(1)</sup> | Max<br>Distributed<br>RAM (Kb) | DSP48E<br>Slices <sup>(2)</sup> | 18 Kb <sup>(3)</sup> | 36 Kb | Max<br>(Kb) | CMTs <sup>(4)</sup> |          | Blocks for<br>PCI<br>Express | Ethernet<br>MACs <sup>(5)</sup>             | GTP | GTX   | I/O<br>Banks <sup>(8)</sup> | User  |

| XC5VLX30   | 80 x 30                          | 4,800                             | 320                            | 32                              | 64                   | 32    | 1,152       | 2                   | N/A      | N/A                          | N/A                                         | N/A | N/A   | 13                          | 400   |

| XC5VLX50   | 120 x 30                         | 7,200                             | 480                            | 48                              | 96                   | 48    | 1,728       | 6                   | N/A      | N/A                          | N/A                                         | N/A | N/A   | 17                          | 560   |

| XC5VLX85   | 120 x 54                         | 12,960                            | 840                            | 48                              | 192                  | 96    | 3,456       | 6                   | N/A      | N/A                          | N/A                                         | N/A | N/A   | 17                          | 560   |

| XC5VLX110  | 160 x 54                         | 17,280                            | 1,120                          | 64                              | 256                  | 128   | 4,608       | 6                   | N/A      | N/A                          | N/A                                         | N/A | N/A   | 23                          | 800   |

| XC5VLX155  | 160 x 76                         | 24,320                            | 1,640                          | 128                             | 384                  | 192   | 6,912       | 6                   | N/A      | N/A                          | N/A                                         | N/A | N/A   | 23                          | 800   |

| XC5VLX220  | 160 x 108                        | 34,560                            | 2,280                          | 128                             | 384                  | 192   | 6,912       | 6                   | N/A      | N/A                          | N/A                                         | N/A | N/A   | 23                          | 800   |

| XC5VLX330  | 240 x 108                        | 51,840                            | 3,420                          | 192                             | 576                  | 288   | 10,368      | 6                   | N/A      | N/A                          | N/A                                         | N/A | N/A   | 33                          | 1,200 |

| XC5VLX20T  | 60 x 26                          | 3,120                             | 210                            | 24                              | 52                   | 26    | 936         | 1                   | N/A      | 1                            | 2                                           | 4   | N/A   | 7                           | 172   |

| XC5VLX30T  | 80 x 30                          | 4,800                             | 320                            | 32                              | 72                   | 36    | 1,296       | 2                   | N/A      | 1                            | 4                                           | 8   | N/A   | 12                          | 360   |

| XC5VLX50T  | 120 x 30                         | 7,200                             | 480                            | 48                              | 120                  | 60    | 2,160       | 6                   | N/A      | 1                            | 4                                           | 12  | N/A   | 15                          | 480   |

| XC5VLX85T  | 120 x 54                         | 12,960                            | 840                            | 48                              | 216                  | 108   | 3,888       | 6                   | N/A      | 1                            | 4                                           | 12  | N/A   | 15                          | 480   |

| XC5VLX110T | 160 x 54                         | 17,280                            | 1,120                          | 64                              | 296                  | 148   | 5,328       | 6                   | N/A      | 1                            | 4                                           | 16  | N/A   | 20                          | 680   |

| XC5VLX155T | 160 x 76                         | 24,320                            | 1,640                          | 128                             | 424                  | 212   | 7,632       | 6                   | N/A      | 1                            | 4                                           | 16  | N/A   | 20                          | 680   |

| XC5VLX220T | 160 x 108                        | 34,560                            | 2,280                          | 128                             | 424                  | 212   | 7,632       | 6                   | N/A      | 1                            | 4                                           | 16  | N/A   | 20                          | 680   |

| XC5VLX330T | 240 x 108                        | 51,840                            | 3,420                          | 192                             | 648                  | 324   | 11,664      | 6                   | N/A      | 1                            | 4                                           | 24  | N/A   | 27                          | 960   |

| XC5VSX35T  | 80 x 34                          | 5,440                             | 520                            | 192                             | 168                  | 84    | 3,024       | 2                   | N/A      | 1                            | 4                                           | 8   | N/A   | 12                          | 360   |

| XC5VSX50T  | 120 x 34                         | 8,160                             | 780                            | 288                             | 264                  | 132   | 4,752       | 6                   | N/A      | 1                            | 4                                           | 12  | N/A   | 15                          | 480   |

| XC5VSX95T  | 160 x 46                         | 14,720                            | 1,520                          | 640                             | 488                  | 244   | 8,784       | 6                   | N/A      | 1                            | 4                                           | 16  | N/A   | 19                          | 640   |

| XC5VSX240T | 240 x 78                         | 37,440                            | 4,200                          | 1,056                           | 1,032                | 516   | 18,576      | 6                   | N/A      | 1                            | 4                                           | 24  | N/A   | 27                          | 960   |

| XC5VTX150T | 200 x 58                         | 23,200                            | 1,500                          | 80                              | 456                  | 228   | 8,208       | 6                   | N/A      | 1                            | 4                                           | N/A | 40    | 20                          | 680   |

| XC5VTX240T | 240 x 78                         | 37,440                            | 2,400                          | 96                              | 648                  | 324   | 11,664      | 6                   | N/A      | 1                            | 4                                           | N/A | 48    | 20                          | 680   |

| XC5VFX30T  | 80 x 38                          | 5,120                             | 380                            | 64                              | 136                  | 68    | 2,448       | 2                   | 1        | 1                            | 4                                           | N/A | 8     | 12                          | 360   |

| XC5VFX70T  | 160 x 38                         | 11,200                            | 820                            | 128                             | 296                  | 148   | 5,328       | 6                   | 1        | 3                            | 4                                           | N/A | 16    | 19                          | 640   |

| XC5VFX100T | 160 x 56                         | 16,000                            | 1,240                          | 256                             | 456                  | 228   | 8,208       | 6                   | 2        | 3                            | 4                                           | N/A | 16    | 20                          | 680   |

| XC5VFX130T | 200 x 56                         | 20,480                            | 1,580                          | 320                             | 596                  | 298   | 10,728      | 6                   | 2        | 3                            | 6                                           | N/A | 20    | 24                          | 840   |

| XC5VFX200T | 240 x 68                         | 30,720                            | 2,280                          | 384                             | 912                  | 456   | 16,416      | 6                   | 2        | 4                            | 8                                           | N/A | 24    | 27                          | 960   |

#### Table 1: Virtex-5 FPGA Family Members