# EECS150 - Digital Design

# Lecture 17 - Finite State Machines Revisited

March 13, 2012 John Wawrzynek

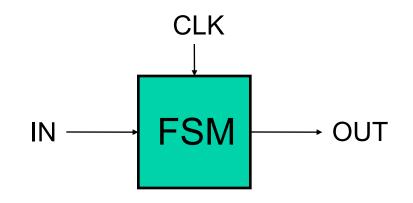

# Finite State Machines (FSMs)

x0

xn-1

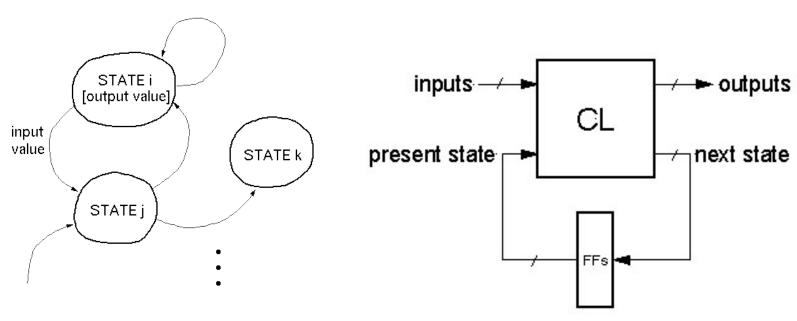

- FSM circuits are a type of sequential circuit:

- output depends on present and past inputs

• effect of past inputs is represented by the current *state*

input value STATE k

STATE j

**FSM**

**-** yn−1

- Behavior is represented by State Transition Diagram:

- traverse one edge per clock cycle.

Spring 2012

EECS150 - Lec17-FSM

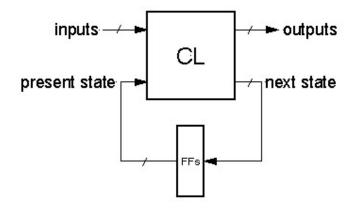

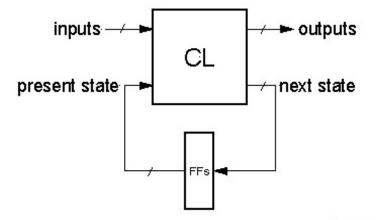

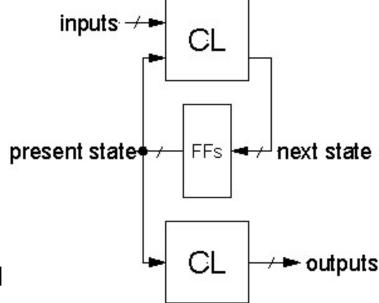

# FSM Implementation

- Flip-flops form state register

- number of states ≤ 2<sup>number of flip-flops</sup>

- CL (combinational logic) calculates next state and output

- Remember: The FSM follows exactly one edge per cycle.

So far we have learned how to implement in Verilog. Now we learn how to design "by hand" to the gate level.

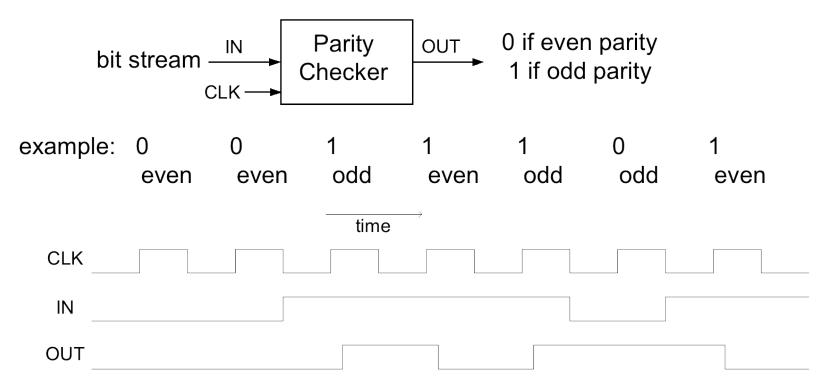

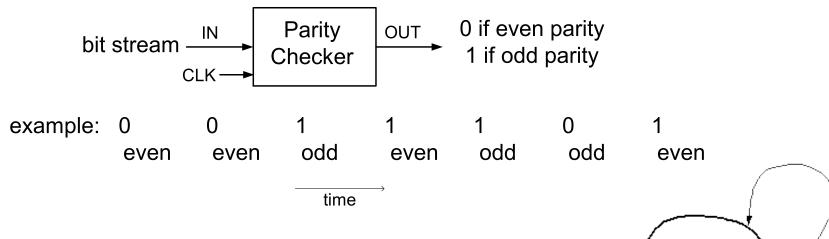

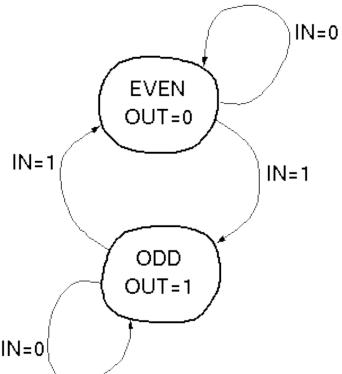

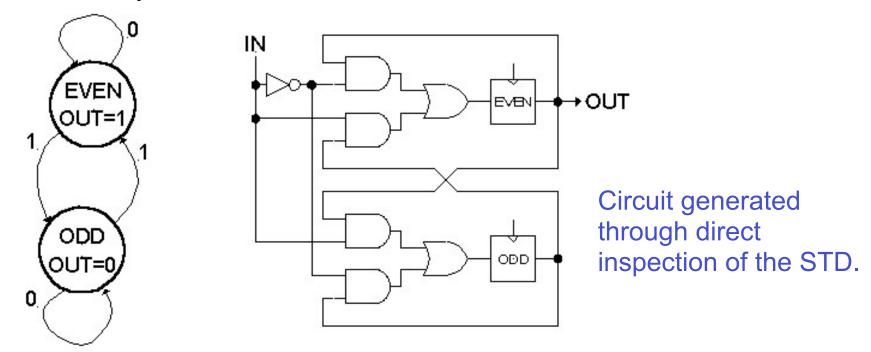

#### Parity Checker Example

A string of bits has "even parity" if the number of 1's in the string is even.

Design a circuit that accepts a bit-serial stream of bits and outputs a 0 if the parity thus far is even and outputs a 1 if odd:

Next we take this example through the "formal design process". But first, can you guess a circuit that performs this function?

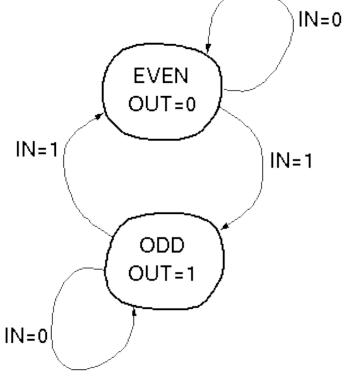

#### "State Transition Diagram"

- circuit is in one of two "states".

- transition on each cycle with each new input, over exactly one arc (edge).

- Output depends on which state the circuit is in.

#### **State Transition Table:**

| present<br>state           | OUT     | IN      | next<br>state              |

|----------------------------|---------|---------|----------------------------|

| EVEN<br>EVEN<br>ODD<br>ODD | 0 0 1 1 | 0 1 0 1 | EVEN<br>ODD<br>ODD<br>EVEN |

Invent a code to represent states:

Let 0 = EVEN state, 1 = ODD state IN=0

| present state (ps) | OUT | IN | next state (ns) |

|--------------------|-----|----|-----------------|

| 0                  | 0   | 0  | 0               |

| 0                  | 0   | 1  | 1               |

| 1                  | 1   | 0  | 1               |

| 1                  | 1   | 1  | 0               |

Derive logic equations from table (how?):

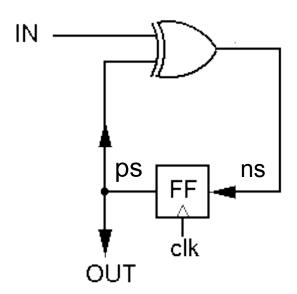

#### Logic equations from table:

OUT = PS NS = PS xor IN

#### Circuit Diagram:

- XOR gate for NS calculation

- DFF to hold present state

- no logic needed for output in this example.

#### Review of Design Steps:

- 1. Specify circuit function (English)

- 2. Draw state transition diagram

- 3. Write down symbolic state transition table

- 4. Write down encoded state transition table

- 5. Derive logic equations

- 6. Derive circuit diagram

Register to hold state

Combinational Logic for Next State and Outputs

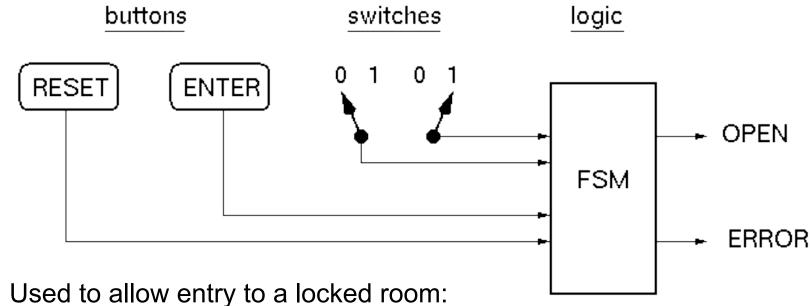

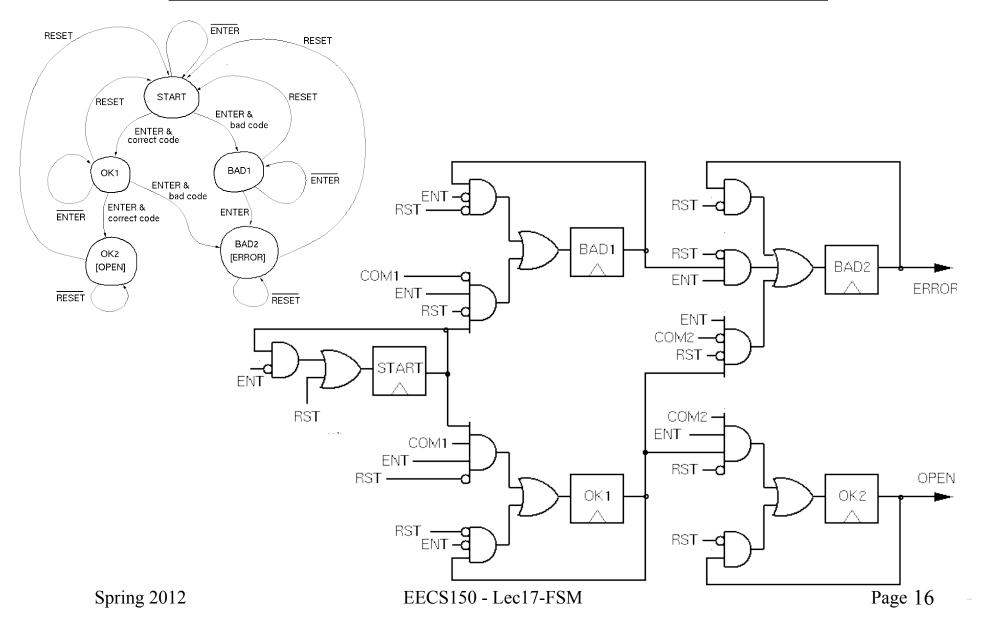

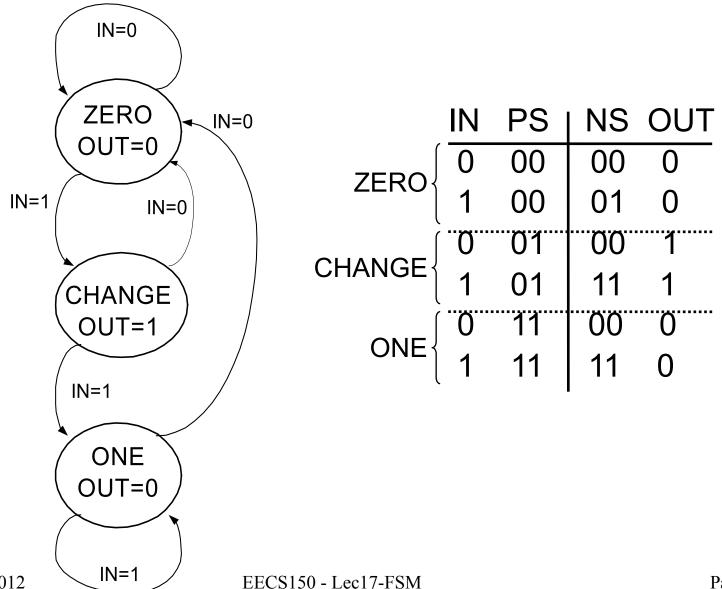

#### Combination Lock Example

- - 2-bit serial combination. Example 01,11:

- 1. Set switches to 01, press ENTER

- 2. Set switches to 11, press ENTER

- 3. OPEN is asserted (OPEN=1).

If wrong code, ERROR is asserted (after second combo word entry). Press Reset at anytime to try again.

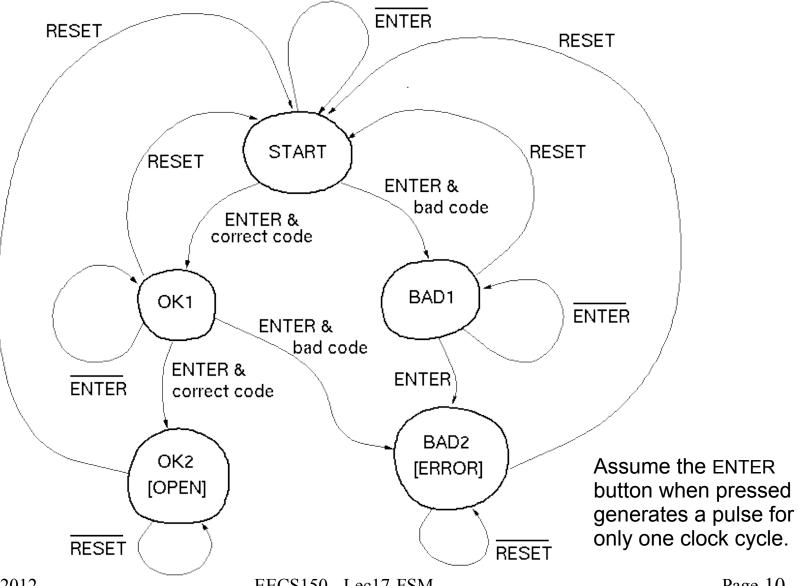

#### **Combinational Lock STD**

Page 10 Spring 2012 EECS150 - Lec17-FSM

#### Symbolic State Transition Table

| RESET | ENTER | COM1 | COM2 | Preset State | Next State | OPEN | ERROR |

|-------|-------|------|------|--------------|------------|------|-------|

| 0     | 0     | *    | *    | START        | START      | 0    | 0     |

| 0     | 1     | 0    | *    | START        | BAD1       | 0    | 0     |

| 0     | 1     | 1    | *    | START        | OK1        | 0    | 0     |

| 0     | 0     | *    | *    | OK1          | OK1        | 0    | 0     |

| 0     | 1     | *    | 0    | OK1          | BAD2       | 0    | 0     |

| 0     | 1     | *    | 1    | OK1          | OK2        | 0    | 0     |

| 0     | *     | *    | *    | OK2          | OK2        | 1    | 0     |

| 0     | 0     | *    | *    | BAD1         | BAD1       | 0    | 0     |

| 0     | 1     | *    | *    | BAD1         | BAD2       | 0    | 0     |

| 0     | *     | *    | *    | BAD2         | BAD2       | 0    | 1     |

| 1     | *     | *    | *    | *            | START      | 0    | 0     |

|       |       |      |      |              |            | 1    |       |

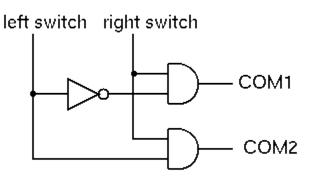

Decoder logic for checking combination (01,11):

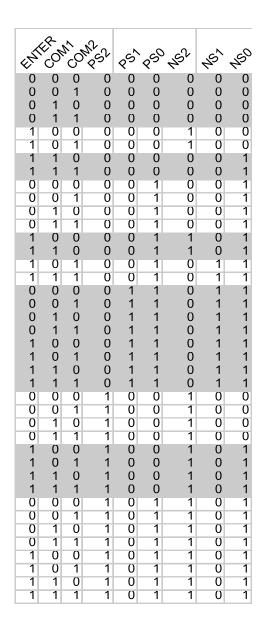

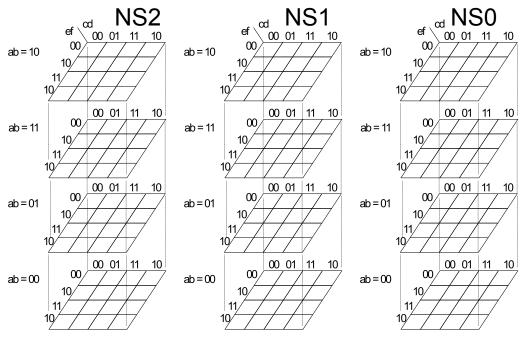

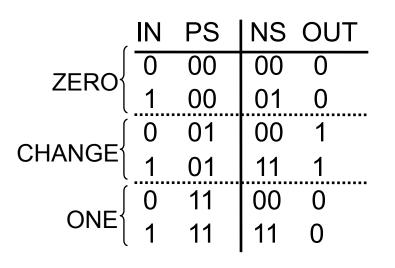

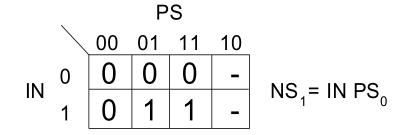

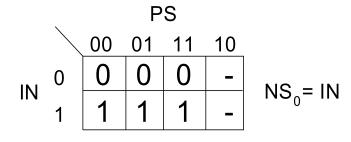

#### **Encoded ST Table**

- Assign states: START=000, OK1=001, OK2=011 BAD1=100, BAD2=101

- Omit reset. Assume that primitive flip-flops has reset input.

- Rows not shown have *don't cares* in output. Correspond to invalid PS values.

What are the output functions for OPEN and ERROR? EECS150 - Lec17-FSM

# **State Encoding**

In general:

# of possible FSM state = 2<sup># of Flip-flops</sup> Example:

state1 = 01, state2 = 11, state3 = 10, state4 = 00

- However, often more than log<sub>2</sub>(# of states) FFs are used, to simplify logic at the cost of more FFs.

- Extreme example is one-hot state encoding.

# State Encoding

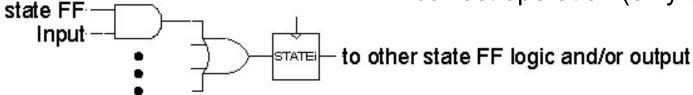

- One-hot encoding of states.

- One FF per state.

Ex: 3 States

STATE1: 001 STATE2: 010 STATE3: 100

- Why one-hot encoding?

- Simple design procedure.

- Circuit matches state transition diagram (example next page).

- Often can lead to simpler and faster "next state" and output logic.

- Why not do this?

- Can be costly in terms of Flip-flops for FSMs with large number of states.

- FPGAs are "Flip-flop rich", therefore one-hot state machine encoding is often a good approach.

#### One-hot encoded FSM

Even Parity Checker Circuit:

In General:

FFs must be initialized for correct operation (only one 1)

#### One-hot encoded combination lock

# **FSM Implementation Notes**

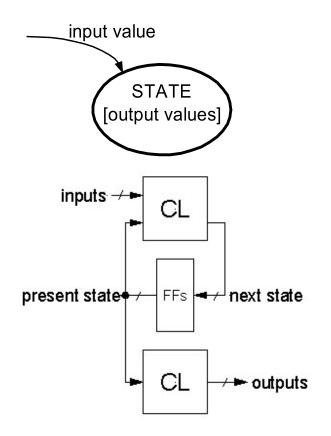

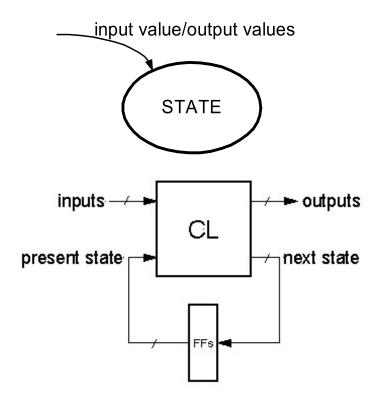

General FSM form:

All examples so far generate output based only on the present state:

Commonly name *Moore Machine*(If output functions include both present state and input then called a *Mealy Machine*)

#### Finite State Machines

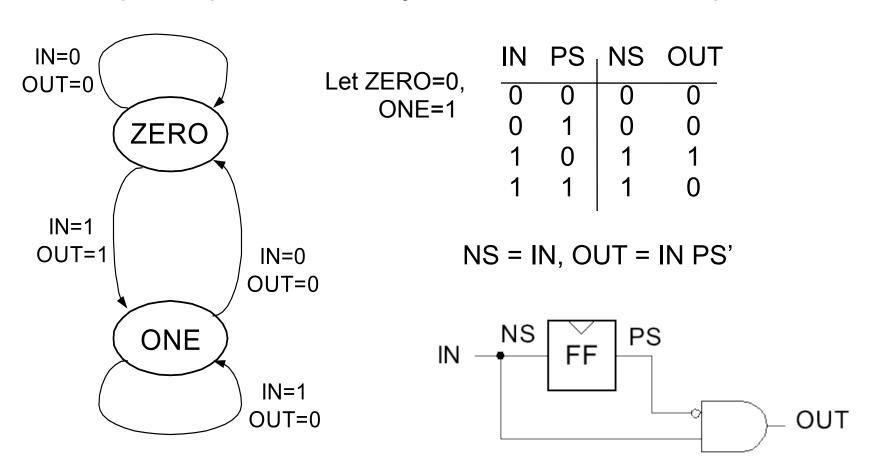

Example: Edge Detector

Bit are received one at a time (one per cycle), such as:  $000111010 \longrightarrow time$

Design a circuit that asserts its output for one cycle when the input bit stream changes from 0 to 1.

Try two different solutions.

# State Transition Diagram Solution A

Spring 2012

Page 19

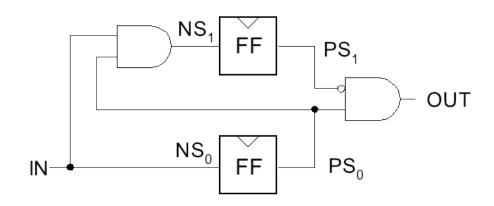

#### Solution A, circuit derivation

#### Solution B

Output depends not only on PS but also on input, IN

What's the *intuition* about this solution?

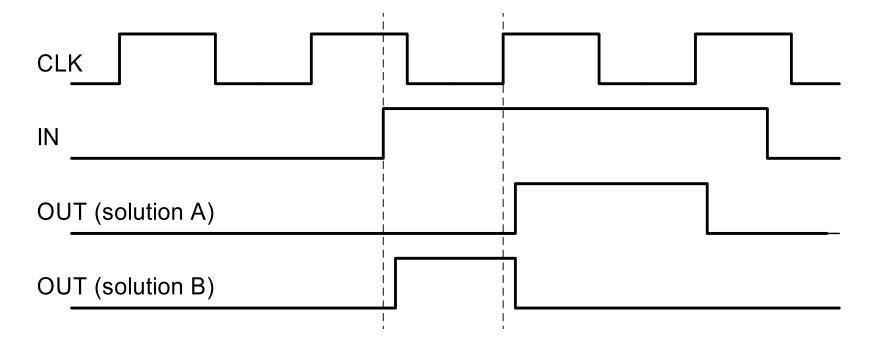

# Edge detector timing diagrams

- Solution A: output follows the clock

- Solution B: output changes with input rising edge and is asynchronous wrt the clock.

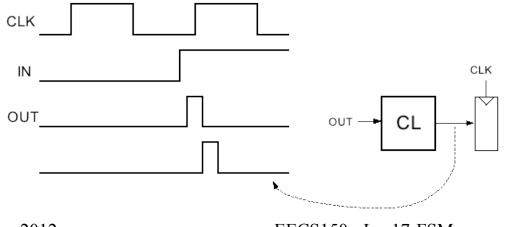

# FSM Comparison

#### Solution A

#### **Moore Machine**

- output function only of PS

- maybe <u>more</u> states (why?)

- synchronous outputs

- no glitches

- one cycle "delay"

- full cycle of stable output

#### Solution B

#### **Mealy Machine**

- output function of both PS & input

- maybe fewer states

- asynchronous outputs

- if input glitches, so does output

- output immediately available

- output may not be stable long enough to be useful (below):

If output of Mealy FSM goes through combinational logic before being registered, the CL might delay the signal and it could be missed by the clock edge.

Spring 2012

EECS150 - Lec17-FSM

Page 23

#### FSM Recap

#### **Moore Machine**

#### **Mealy Machine**

Both machine types allow one-hot implementations.

# Final Notes on Moore versus Mealy

- 1. A given state machine *could* have *both* Moore and Mealy style outputs. Nothing wrong with this, but you need to be aware of the timing differences between the two types.

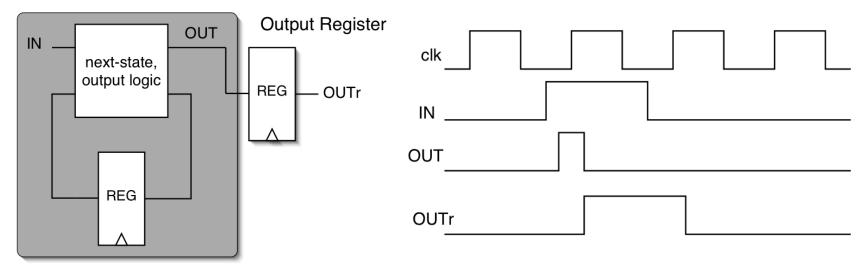

- 2. The output timing behavior of the Moore machine can be achieved in a Mealy machine by "registering" the Mealy output values:

Mealy Machine

Spring 2012 EECS150 - Lec17-FSM Page 25

# General FSM Design Process with Verilog Design Steps: Implementation

- 1. Specify **circuit function** (English)

- 2. Draw state transition diagram

- 3. Write down symbolic state transition table

- 4. Assign encodings (bit patterns) to symbolic states

- 5. Code as Verilog behavioral description

- ✓ Use parameters to represent encoded states.

- ✓ Use separate always blocks for register assignment and CL logic block.

- ✓ Use case for CL block. Within each case section assign all outputs and next state value based on inputs. Note: For Moore style machine make outputs dependent only on state not dependent on inputs.

#### FSMs in Verilog

#### Mealy Machine

#### **Moore Machine**

```

always @(posedge clk)

always @(posedge clk)

if (rst) ps <= ZERO;

if (rst) ps <= ZERO;</pre>

else ps <= ns;</pre>

else ps <= ns;</pre>

always @(ps in)

always @(ps in)

IN=0

case (ps)

OUT=0

case (ps)

ZERO: if (in) begin

ZERO: begin

out = 1'b1;

ZERO

IN=0

out = 1'b0;

ns = ONE:

if (in) ns = CHANGE;

end

ZERO

else ns = ZERO;

else begin

IN=0

IN=1

OUT=0

end

out = 1'b0;

OUT=1

IN=0

CHANGE: begin

OUT=0

ns = ZERO;

IN=1

out = 1'b1;

IN=0

end

ONE

if (in) ns = ONE;

ONE: if (in) begin

else ns = ZERO;

out = 1'b0;

IN=1

CHANGE

end

ns = ONE;

OUT=0

OUT=1

ONE: begin

end

out = 1'b0;

else begin

if (in) ns = ONE;

out = 1'b0;

IN=1

else ns = ZERO;

ns = ZERO;

default: begin

end

ONE

out = 1/bx;

default: begin

OUT=0

ns = default;

out = 1'bx;

end

ns = default;

IN=1

end

```