# CS 152/252A Spring 2023 Computer Architecture

# Final

- You have 170 minutes unless you have DSP accommodations. Exam questions are roughly in the order they were covered in lecture. If a question is used for a clobber, it's labeled either (MT1) or (MT2) depending on the exam it clobbers.

- You must write your student ID on the bottom-left of every page of the exam (except this first one). You risk losing credit for any page you don't write your student ID on.

- For questions with length limits, do not use semicolons or dashes to lengthen your explanation.

| • | The exam is closed book, no calculator, and closed notes, other than three double-sided cheat sheet that you may reference. |

|---|-----------------------------------------------------------------------------------------------------------------------------|

| • | For multiple choice questions,                                                                                              |

|   | means mark all options that apply                                                                                           |

|   | means mark a single choice                                                                                                  |

|   |                                                                                                                             |

| First name                          |  |

|-------------------------------------|--|

| Last name                           |  |

| SID                                 |  |

| Exam Room                           |  |

| Name and SID of person to the right |  |

| Name and SID of person to the left  |  |

| Discussion TAs (or None)            |  |

While the statement of the Honor Code itself is brief, it is an affirmation of our highest ideals as Golden Bears.

Honor code: "As a member of the UC Berkeley community, I act with honesty, integrity, and respect for others."

By signing below, I affirm that all work on this exam is my own work, and honestly reflects my own understanding of the course material. I have not referenced any outside materials (other than one double-sided cheat sheet), nor collaborated with any other human being on this exam. I understand that if the exam proctor catches me cheating on the exam, that I may face the penalty of an automatic "F" grade in this class and a referral to the Center for Student Conduct.

| Signature: |  |  |

|------------|--|--|

| Jignature. |  |  |

### THIS PAGE IS INTENTIONALLY LEFT BLANK

# Q1. [20 pts] Iron Law & Pipelining (MT 1)

For questions (a) to (d), determine whether each given statement is true. If false, point out and replace the incorrect part.

| -          | [3 pts] Ad          | ding a branch delay slot might (1) <u>increase</u> (2) <u>instructions-per-program</u> because (3) the branch predictor might                                                                                             |

|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                     |                                                                                                                                                                                                                           |

|            | Which op            | tion best describes the statement above?                                                                                                                                                                                  |

|            | $\bigcirc$          | The statement is true.                                                                                                                                                                                                    |

|            |                     | The statement is false because part (1) is wrong.                                                                                                                                                                         |

|            | 0                   | The statement is false because part (2) is wrong.                                                                                                                                                                         |

|            |                     | The statement is false because part (3) is wrong.                                                                                                                                                                         |

|            | If the state        | ement is false, replace the incorrect part (under 1 sentence) so that the statement becomes true:                                                                                                                         |

|            |                     |                                                                                                                                                                                                                           |

| <b>(b)</b> | to (3) <u>add</u>   | a classic 5-stage pipeline, supporting precise exceptions might (1) <u>increase</u> (2) <u>cycles-per-instruction</u> due <u>ed logic complexity</u> .                                                                    |

| (b)        | to (3) <u>add</u>   | tion best describes the statement above?                                                                                                                                                                                  |

| (b)        | to (3) <u>add</u>   | tion best describes the statement above?  The statement is true.                                                                                                                                                          |

| (b)        | to (3) <u>add</u>   | tion best describes the statement above?  The statement is true.  The statement is false because part (1) is wrong.                                                                                                       |

| (b)        | to (3) <u>add</u>   | tion best describes the statement above?  The statement is true.  The statement is false because part (1) is wrong.  The statement is false because part (2) is wrong.                                                    |

| (b)        | to (3) add Which op | tion best describes the statement above?  The statement is true.  The statement is false because part (1) is wrong.  The statement is false because part (2) is wrong.  The statement is false because part (3) is wrong. |

| <b>(b)</b> | to (3) add Which op | tion best describes the statement above?  The statement is true.  The statement is false because part (1) is wrong.  The statement is false because part (2) is wrong.                                                    |

| (c)          | [3 pts] Moving from a single-threaded core to SMT-enabled core might (1) <u>increase</u> (2) <u>time-per-cycle</u> due to (3) <u>duplicated microarchitecture structures</u> (PC, ArchRF,) and scheduling logic.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Which option best describes the statement above?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | The statement is true.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | The statement is false because part (1) is wrong.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | The statement is false because part (2) is wrong.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | The statement is false because part (3) is wrong.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | If the statement is false, replace the incorrect part (under 1 sentence) so that the statement becomes true:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ( <b>d</b> ) | [3 pts] Stripmining on a vector processor might (1) <u>increase</u> (2) <u>instructions-per-program</u> due to (3) <u>handling cases where</u> the iteration count is not divisible by the vector length.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              | Which option best describes the statement above?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | • The statement is true.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | The statement is false because part (1) is wrong.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | The statement is false because part (2) is wrong.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | The statement is false because part (3) is wrong.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | If the statement is false, replace the incorrect part (under 1 sentence) so that the statement becomes true:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (e)          | [4 pts] A 5-stage pipeline that has a 1-cycle ALU and a multi-cycle <b>unpipelined</b> FPU has WAW and structural hazards. We would like to pipeline the FPU to potentially help with these issues.  (i) [2 pts] Does pipelining the FPU help with WAW hazards?  Yes No                                                                                                                                                                                                                                                                                                                                                                        |

|              | (ii) [2 pts] Does pipelining the FPU help with structural hazards? • Yes O No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>(f)</b>   | [4 pts] Assume an out-of-order core is executing a store instruction before a load instruction to different addresses (i.e. instruction $0 = $ store to address A, instruction $1 = $ load to address B). For this particular core, the core designer allows for the load to complete before the store (the load is reordered before the store) if the store takes longer than the load to issue or execute. By completing before the store, the load is allowed to bring its data into the cache, potentially evicting older data. Note that the load can only complete, i.e the register for the load will not be modified until it commits. |

|              | Assume the older store throws an exception <b>after</b> the younger load completes. Is this behavior still valid for precise exceptions?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | Yes O No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### Q2. [20 pts] Microcode Grab Bag (MT 1)

The questions in this section may be answered independently of one another.

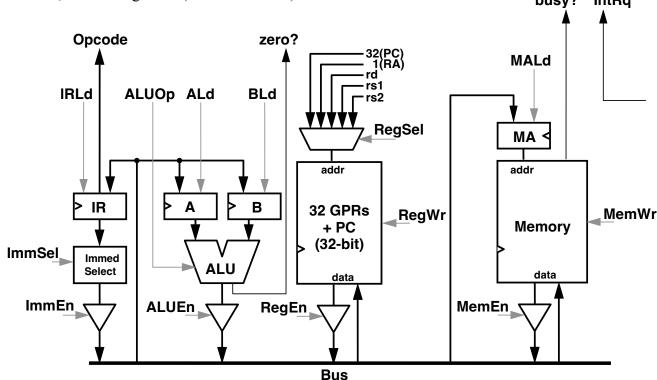

It may be helpful to refer to **Appendix A** on microcoding while answering this question.

(a) [4 pts] The developer before you had tried to implement an instruction in microcode. However, since they didn't take CS 152/252A, their implementation might have a bug! They've left you the instruction and pseudocode, as well as their potentially buggy microcode.

#### **Instruction**:

```

BUGGY rd, rs1, rs2

Pseudocode:

if (R[rs1] != 0) {

R[rd] = R[rd] + M[R[rs2]];

}

```

Microcode implementation:

| Line | Pseudocode      | IR      | Reg<br>Sel | Reg<br>Wr | Reg<br>En | A<br>Ld | B<br>Ld | ALUOp  | ALU<br>En | MA<br>Ld | Mem<br>Wr | Mem<br>En | Imm<br>Sel | Imm<br>En | μBr | Next State |

|------|-----------------|---------|------------|-----------|-----------|---------|---------|--------|-----------|----------|-----------|-----------|------------|-----------|-----|------------|

| 1    | A <- R[rs1]     | Ld<br>O | rs1        | 0         | 1         | 1       | *       | *      | 0         | *        | 0         | 0         | *          | 0         | N   |            |

| 2    | if A == 0, jump | 0       | rs2        | 0         | 1         | *       | *       | COPY_A | 0         | 1        | 0         | 0         | *          | 0         | ΕZ  | FETCH0     |

|      | MA <- R[rs2]    |         |            |           |           |         |         |        |           |          |           |           |            |           |     |            |

| 3    |                 | 0       | *          | 0         | 0         | 1       | *       | *      | *         | 0        | *         | 1         | *          | 0         | N   |            |

| 4    | B <- R[rd]      | 0       | rd         | 0         | 1         | 0       | 1       | *      | 0         | *        | 0         | 0         | *          | 0         | N   |            |

| 5    | R[rd] <- A + B  | 0       | rd         | 1         | 0         | *       | *       | ADD    | 1         | *        | 0         | 0         | *          | 0         | J   | FETCH0     |

- (i) [2 pts] If there is an incorrect line of microcode in the above implementation, what line contains an error? If no lines contain errors, please mark "None of the above".

- Line 1

- O Line 2

- Line 3

- O Line 4

- O Line 5

- None of the above

- (ii) [2 pts] Why is the line you marked above incorrect? You may write at most 2 sentences of explanation.

**Note**: if you marked "None of the above" for the previous subpart, leave this part blank.

Line 3 should be a S (spin) for uBr instead of N (next). This is since we must wait for memory to load into A, which requires us to spin on that line until the memory value has arrived. (**Note:** This was the intended error. However, there were two additional, accidental errors: ALUEn should be 0 to prevent the case of both memory and ALU writing to the bus at the same time; MemWr should be 0 to prevent writing garbage or some other value to the memory address. Credit was given if the student selected the correct option in part (i) and had at least one of these reasons.)

| SID: |  |  |  |

|------|--|--|--|

| SID: |  |  |  |

### (b) [16 pts] Reverse Engineering Microcode

The aforementioned developer was, unfortunately, also a firm believer in self-documenting code and chose not to explain what some of the microcoded instructions do! In this part, we consider an implementation of the microcoded instruction mystery. The microcode for this instruction can be found on page 7 of your exam booklet.

- (i) [9 pts] Analyze the encoded control signals for the mystery instruction and complete the pseudocode in the space provided in the table on page 7. If a row encodes multiple pseudo-operations, write both operations in the same pseudocode box. Unless the pseudocode for a row is already provided, you need to fill out the pseudocode for every row with microcode signals in the table.

- (ii) [3 nts] In one sentence (or less), name or describe the high-level operation that this instruction implements

| No credit will be given for simply translating the pseudocode to English.                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| This is an implementation of the strlen function. —or—  This instruction counts the number of sequential, non-zero valued bytes in a buffer. |

| (iii) [2 pts] What is/are the input register(s) of the mystery instruction?                                                                  |

| rs1 rs2                                                                                                                                      |

| ☐ rd<br>☐ A                                                                                                                                  |

| ☐ B                                                                                                                                          |

| (iv) [2 pts] What is/are the output register(s) of the mystery instruction?                                                                  |

|                                                                                                                                              |

| rs2                                                                                                                                          |

| □ A                                                                                                                                          |

| ☐ B                                                                                                                                          |

Microcode Implementation of the MYSTERY Instruction

| Next State | *                  | *        | *        |   | FETCH0                        | *        | *   | *   | *      | * | FETCH0 | *     | *  | AGAIN |

|------------|--------------------|----------|----------|---|-------------------------------|----------|-----|-----|--------|---|--------|-------|----|-------|

| µBr        | z                  | S        | Ω        |   | 7                             | z        | z   | z   | z      | တ | EZ     | z     | z  | ٦     |

| lmm<br>En  | 0                  | 0        | 0        |   | 0                             | 0        | 0   | 0   | 0      | 0 | 0      | 0     | 0  | 0     |

| lmm<br>Sel | *                  | *        | *        |   | *                             | *        | *   | *   | *      | * | *      | *     | *  | *     |

| Mem<br>En  | 0                  | _        | 0        |   | 0                             | 0        | 0   | 0   | 0      | - | 0      | 0     | 0  | 0     |

| Mem<br>Wr  | 0                  | 0        | 0        |   | 0                             | 0        | 0   | 0   | 0      | 0 | 0      | 0     | 0  | 0     |

| MA         | _                  | 0        | *        |   | *                             | *        | *   | *   | -      | 0 | *      | *     | *  | *     |

| ALU<br>En  | 0                  | 0        | _        |   | 0                             | _        | _   | 0   | _      | 0 | 0      | _     | 0  | _     |

| ALUOp      | *                  | *        | INC_A_4  |   | *                             | COPY_A   | SUB | *   | COPY_A | * | COPY_B | INC_A | *  | INC_B |

| R P        | *                  | *        | *        |   | *                             | -        | *   | *   | *      | _ | 0      | 0     | _  | *     |

| P P        | _                  | 0        | 0        |   | *                             | 0        | *   | _   | 0      | 0 | 0      | -     | 0  | 0     |

| Reg<br>En  | -                  | 0        | 0        |   | 0                             | 0        | 0   | _   | 0      | 0 | 0      | 0     | -  | 0     |

| Reg<br>Wr  | 0                  | 0        | 1        |   | 0                             | 0        | _   | 0   | 0      | 0 | 0      | 0     | 0  | 1     |

| Reg<br>Sel | PC                 | *        | PC       |   | *                             | *        | Rd  | Rs1 | *      | * | *      | *     | Rd | Rd    |

| 모          | *                  | _        | 0        |   | *                             | 0        | 0   | 0   | 0      | 0 | 0      | 0     | 0  | 0     |

| Pseudocode | MA ← PC;<br>A ← PC | IR ← Mem | PC ← A+4 |   | microbranch<br>back to FETCH0 |          |     |     |        |   |        |       |    |       |

| State      | FETCH0:            |          |          | : | NOP0:                         | MYSTERY: |     |     | AGAIN: |   |        |       |    |       |

Microcode Implementation of the MYSTERY Instruction

|            |                                        |                     |          |                               | _                | _                        | _                     | _                 | _                |                         | _         |                      |                             |  |  |

|------------|----------------------------------------|---------------------|----------|-------------------------------|------------------|--------------------------|-----------------------|-------------------|------------------|-------------------------|-----------|----------------------|-----------------------------|--|--|

| Next State | *                                      | *                   | *        | FETCH0                        | *                | *                        | *                     | *                 | *                | FETCH0                  | *         | *                    | AGAIN                       |  |  |

| µBr        | z                                      | S                   | D        | 7                             | z                | z                        | z                     | z                 | S                | EZ                      | z         | z                    | ſ                           |  |  |

| lmm<br>En  | 0                                      | 0                   | 0        | 0                             | 0                | 0                        | 0                     | 0                 | 0                | 0                       | 0         | 0                    | 0                           |  |  |

| lmm<br>Sel | *                                      | *                   | *        | *                             | *                | *                        | *                     | *                 | *                | *                       | *         | *                    | *                           |  |  |

| Mem<br>En  | 0                                      | _                   | 0        | 0                             | 0                | 0                        | 0                     | 0                 | _                | 0                       | 0         | 0                    | 0                           |  |  |

| Mem<br>Wr  | 0                                      | 0                   | 0        | 0                             | 0                | 0                        | 0                     | 0                 | 0                | 0                       | 0         | 0                    | 0                           |  |  |

| MA         | 1                                      | 0                   | *        | *                             | *                | *                        | *                     | _                 | 0                | *                       | *         | *                    | *                           |  |  |

| ALU<br>En  | 0                                      | 0                   | _        | 0                             | _                | _                        | 0                     | -                 | 0                | 0                       | -         | 0                    | _                           |  |  |

| ALUOp      | *                                      | *                   | INC_A_4  | *                             | COPY_A           | SUB                      | *                     | COPY_A            | *                | COPY_B                  | INC_A     | *                    | INC_B                       |  |  |

| P P        | *                                      | *                   | *        | *                             | _                | *                        | *                     | *                 | _                | 0                       | 0         | _                    | *                           |  |  |

| A<br>Ld    | 1                                      | 0                   | 0        | *                             | 0                | *                        | 1                     | 0                 | 0                | 0                       | 1         | 0                    | 0                           |  |  |

| Reg<br>En  | l                                      | 0                   | 0        | 0                             | 0                | 0                        | _                     | 0                 | 0                | 0                       | 0         | 1                    | 0                           |  |  |

| Reg<br>Wr  | 0                                      | 0                   | 1        | 0                             | 0                | _                        | 0                     | 0                 | 0                | 0                       | 0         | 0                    | 1                           |  |  |

| Reg<br>Sel | ЭЫ                                     | *                   | ЪС       | *                             | *                | Rd                       | Rs1                   | *                 | *                | *                       | *         | Rd                   | Rd                          |  |  |

| R          | *                                      | _                   | 0        | *                             | 0                | 0                        | 0                     | 0                 | 0                | 0                       | 0         | 0                    | 0                           |  |  |

| Pseudocode | $MA \leftarrow PC; \\ A \leftarrow PC$ | $IR \leftarrow Mem$ | PC ← A+4 | microbranch<br>back to FETCH0 | $B \leftarrow A$ | $R[Rd] \leftarrow A - B$ | $A \leftarrow R[Rs1]$ | $MA \leftarrow A$ | $B \leftarrow M$ | if EZ(B)<br>goto FETCH0 | A ← A + 1 | $B \leftarrow R[Rd]$ | R[Rd] ← B + 1<br>goto AGAIN |  |  |

| State      | FETCH0:                                |                     |          | <br>NOP0:                     | MYSTERY:         |                          |                       | AGAIN:            |                  |                         |           |                      |                             |  |  |

### Q3. [12 pts] Caches (MT 1)

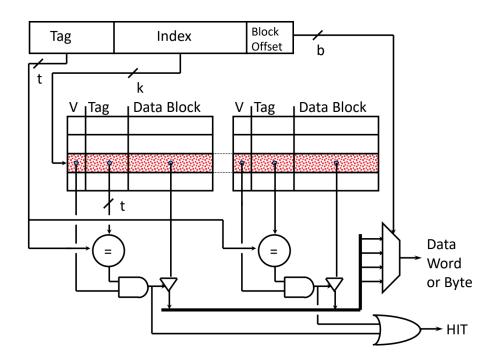

Way prediction is an optimization technique used in set-associative caches. The principle is that we predict which cache way is most likely going to be accessed for a particular memory request. If our prediction is correct, there is no need to check the other ways in the cache. If it is incorrect, we proceed as though with a normal set associative access.

- (a) First, consider a two way set associative cache which is designed with either way-prediction (one data way is read at a time) or concurrent data access (both data ways are read at the same time).

- (i) [2 pts] True or False: In all circumstances, conventional concurrent data access caches have an AMAT *less than or equal* to that of way-predicted cache.

True

False

In no more than 2 sentences, justify your answer:

Even with 100% prediction accuracy, the way-predicted cache will perform a tag check and data access, which is the same as the concurrent access cache.

(ii) [2 pts] True or False: A concurrent data access cache will consume *equal or more* power than a way predicted cache in all circumstances.

True

False

In no more than 2 sentences, justify your answer:

In the case of a correct prediction, the way-predicting cache only has to activate 1 way, but in all cases the concurrent access cache will activate all the ways.

Figure 1: General 2-Way Set Associative Cache

(b) (i) [2 pts] Consider a 16 kB two-way set associative cache without way prediction. Given a hit time of 5 cycles, a hit rate of 80%, and an L2 access time of 30 cycles, what is the AMAT of this cache?

| 5+0.2*30 = 11 |

|---------------|

|---------------|

|       | 2+0.4*30 = 14                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (iii) | [1 pt] Now consider a 16 kB two-way set associative cache with way prediction. What is the hit rate of this cache?  60% 70% 80%                                          |

|       | None of the above                                                                                                                                                        |

| (iv)  | [3 pts] What is the AMAT of this cache?                                                                                                                                  |

| (v)   | (0.6*2 + 0.4*5) + 0.2*30 = 9.2 [1 pt] In the case of a data cache, which of the following is the preferred input to the way-predictor (reduces latency to cache access)? |

|       |                                                                                                                                                                          |

|       | <ul><li>The data address</li><li>PC</li></ul>                                                                                                                            |

| (vi)  |                                                                                                                                                                          |

## Q4. [18 pts] Virtual Memory (MT 1)

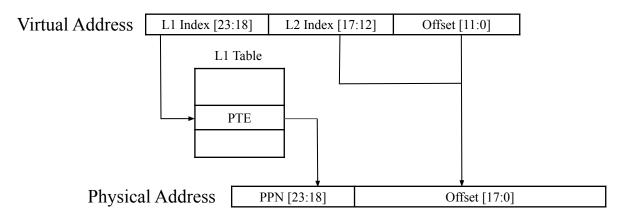

Recall from discussion that superpages are memory pages of large sizes. Most general purpose processors support superpages because of many benefits they can bring to the table. Processes can specify if they would like to allocate superpages or "regular pages" for their workload. This question will explore superpaging in more detail.

As a quick refresher, here is a diagram showing how superpages are translated in a system with two-level page tables, where the Page Table Entry in the L1 table points to a superpage.

|  | (a) | VM | Conce | pt | Blitz |

|--|-----|----|-------|----|-------|

|--|-----|----|-------|----|-------|

| VM Concept Blitz        |                                                                                                                                                                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (i) [2 pts] Let's recap | p some virtual memory concepts. Select all that are true.                                                                                                                                                                                   |

| Paging All mo Virtual   | is with virtual memory can give the illusion of more memory than is physically available. provides a layer of security.  dern systems must have virtual memory.  memory is expensive from a hardware and runtime perspective.  of the above |

| (ii) [2 pts] Let's cons | ider some superpaging concepts. Select all that are true.                                                                                                                                                                                   |

| A syste With so         | raging reduces hardware complexity.  em that supports superpaging is less prone to external fragmentation.  uperpaging, TLB memory scope increases.  uperpaging, disk traffic can increase.                                                 |

| ( ) None of             | of the above                                                                                                                                                                                                                                |

11

SID: \_

#### (b) [10 pts] **Super Translation**

Consider a system that uses **32-bit** words, **10-bit** virtual addresses, **16-byte** pages, and **three-level** page tables. This system supports superpages. The system memory has a latency of **90 ns**. A secondary storage (disk) is attached to the system. The disk has a latency of **2.5 ms** and a speed of **0.1 byte/ns**.

In addition to contents, each PTE contains 1 bit indicating whether the pointed page is on disk, and 1 bit indicating if that page is a superpage. If a page is on disk, it needs to be transferred into memory before its content can be read. Note that here we have simplified the page fault handling process.

Below are the virtual addresses of two memory accesses, the content of the Page Table Base Register, and a table showing the contents of a portion of physical memory used for page tables. Recall that the content of a PTE stores the page number of the next-level page table.

| Access Order | Virtual Address |

|--------------|-----------------|

| 1            | 0x0FA           |

| 2            | 0x349           |

| Page Table Base Register |  |

|--------------------------|--|

| 0x30                     |  |

| Addr | Contents | Superpage? | On Disk? |

|------|----------|------------|----------|

| 0x00 | 0x04     | 0          | 0        |

| 0x04 | 0x06     | 0          | 1        |

| 0x08 |          |            |          |

| 0x0C | 0x20     | 1          | 0        |

| 0x10 |          |            |          |

| 0x14 |          |            |          |

| 0x18 | 0xA1     | 0          | 1        |

| 0x1C |          |            |          |

| 0x20 |          |            |          |

| 0x24 | 0x15     | 0          | 1        |

| 0x28 | 0x0A     | 0          | 1        |

| 0x2C | 0x78     | 0          | 0        |

| 0x30 | 0x05     | 0          | 0        |

| 0x34 |          |            |          |

| 0x38 |          |            |          |

| 0x3C | 0x90     | 1          | 1        |

| 0x40 |          |            |          |

| 0x44 |          |            |          |

| 0x48 | 0x12     | 1          | 1        |

| 0x4C | 0x01     |            |          |

| 0x50 | 0x09     | 1          | 0        |

| 0x54 |          |            |          |

| 0x58 |          |            |          |

| 0x5C | 0x02     | 0          | 1        |

| (i) | [4 pts] What | ic the nhyci    | cal address | of the | first memory | access? |

|-----|--------------|-----------------|-------------|--------|--------------|---------|

| (1) | 14 DIST What | . IS the bilysi | cai address | or the | mst memorv   | access? |

(ii) [4 pts] What is the physical address of the second memory access?

(iii) [2 pts] Which of the two memory accesses has a **lower** latency? Here, latency is defined as the time between when an access begins the translation process and when the target byte is retrieved from memory. Assume that no other latency is involved except the ones mentioned above.

*Hint: disk access time = latency + size-of-transfer / rate-of-transfer*

|  | First memory access | $\bigcirc$ | Second memory acces |

|--|---------------------|------------|---------------------|

|--|---------------------|------------|---------------------|

| (c) | Sup   | erpage Scenarios                                                                                                                                                                                                                                                                         |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | In th | ne following scenarios, which paging mechanism would be better and why?                                                                                                                                                                                                                  |

|     | (i)   | [2 pts] Context switching among many apps that have a working set of 1 MB on a system with 4 MB pages and 16 MB superpages.                                                                                                                                                              |

|     |       | O Superpaging Regular Paging O Neither is better than the other                                                                                                                                                                                                                          |

|     |       | In <b>no more than 2 sentences</b> , justify your answer:                                                                                                                                                                                                                                |

|     |       | We do not need superpages for the size of the working sets because it ends up wasting memory. This would result in potentially hitting disk more with enough apps running in parallel.                                                                                                   |

|     | (ii)  | [2 pts] Training a machine learning model with a massive dataset (4 GB) – requiring multiple iterations through the                                                                                                                                                                      |

|     | ` '   | data – on a system with 4 MB pages and 16 MB superpages.                                                                                                                                                                                                                                 |

|     |       | ● Superpaging ○ Regular Paging ○ Neither is better than the other                                                                                                                                                                                                                        |

|     |       | In <b>no more than 2 sentences</b> , justify your answer:                                                                                                                                                                                                                                |

|     |       | The spatial locality of the workload, paired with the need for more memory scope at the TLB level, points to superpaging. With larger TLB scope, CPI is less (no need for as many expensive page table walks during memory accesses) and hence, a faster completion of the task at hand. |

### Q5. [20 pts] Out-of-Order Pipelines (MT 2)

offs, is your coworker's suggestion a good one?

### (a) [8 pts] Avenue (Issue) Q

In this part, you are working on the design of an out-of-order processor which has separate functional units for integer operations, floating point, and memory. Each functional unit has its own issue queue (also referred to as a reservation station or issue buffer) from which it is able to issue dispatched instructions.

(i) [1 pt] A coworker suggests that it is a good idea to use a large ROB (>200 entries) and size the issue queue of each individual functional unit such that it is the size of the ROB. When considering power, performance, and area trade

|      | ○ Yes ● No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (ii) | [3 pts] In no more than two sentences, justify your answer:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | A 200 entry issue queue for each functional unit is not feasible. Issue queues are expensive from a logic and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | area perspective because they are responsible for evaluating both whether an instruction can issue at all and, amongst the ready candidates, which should issue. Additionally, updating large IQs when information about                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | writebacks becomes available is very expensive as it requires essentially treating the IQ as content addressable memory (equivalently, a very highly associative cache!).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | memory (equivalently, a very linging associative cache:).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | The state of the s |

|      | It doesn't make sense to size each IQ to the ROB as it is very unlikely that we'd ever actually <i>use</i> such capacity as most reasonable programs are a mix of integer, memory, and floating point operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

(iii) [1 pt] Another coworker suggests that the ROB should have more entries than the total sum of all issue queue entries across all functional units. When considering power, performance, and area trade offs, is your coworker's suggestion a good one? You may ignore considerations around scaling the physical register file and free list.

Yes No

(iv) [3 pts] In no more than two sentences, justify your answer:

addressable memory behaviors. Since the ROB sets the maximum number of in-flight instructions in the pipeline

(including undispatched and issued instructions as well as completed but uncommitted instructions!) whereas the

IQ sizes determines the maximum number of instructions which can be considered for issue in a cycle. If the ROB

is smaller or equal to the sum of the issue queues, the issue queues (and thus the amount of ILP available to us!)

will be underutilized as the ROB will fill before we reach capacity. To keep the backend saturated, we want to be

able to refill all IQs whenever an instruction issues as well as to track all possibly instructions as the flow through

execution. We always want to scale the cheaper structure to keep the more expensive structure saturated: why the

ROB grows to fully cover the IQs.

### (b) [12 pts] They see me rollin', they hatin'

In the tables below, update the ROB, rename table, and freelist to reflect the state of the processor after executing the given program and completing any necessary rollbacks using a multi-cycle unwind procedure. Assume that all instructions which can be committed are committed *before* any rollback operations begin. Additionally, assume that the pagefault exception is detected after the sub instruction has already begun executing and that the branch mispredict is resolved at some point after the pagefault exception.

- The free list operates as a FIFO queue; entries are popped from the left and freed entries are pushed on the right.

- When removing an item from the freelist, do not cross out entries; instead, mark an "X" in the row immediately below.

- If an instruction does not write to the register file, mark an "X" in the ROB.

- When completing the rename table, do not cross out entries. Instead, write the new physical register in the next box to the right. You may not need to use all spaces.

The first instruction has been completed in the tables for you. All three of the tables below will be graded.

| PC | Instruction                                                             |

|----|-------------------------------------------------------------------------|

| 00 | addi x2, x2, #1                                                         |

| 04 | ld x2, 0(x2)                                                            |

| 08 | beq x2, x0, label; mispredicted as not taken, resolved very late        |

| 0c | mul x3, x2, x2                                                          |

| 10 | st x3, 0(x2) ; pagefault exception, detected early                      |

| 14 | st $x3$ , $0(x2)$ ; pagefault exception, detected early sub $x2$ , $x2$ |

|    |                                                                         |

| ff | label: /* ommitted */                                                   |

|   |           |    | ROB         |           |             |

|---|-----------|----|-------------|-----------|-------------|

| # | Operation | Rd | Previous Rd | Committed | Rolledback? |

| 0 | addi      | p8 | p0          | Y         | N           |

| 1 | ld        | p2 | p8          | Y         | N           |

| 2 | beq       | X  | X           | Y         | N           |

| 3 | mul       | p9 | p5          | N         | Y           |

| 4 | st        | X  | X           | N         | Y           |

| 5 | sub       | p6 | p2          | N         | Y           |

|    |    |    |    | Freelist |    |    |    |  |

|----|----|----|----|----------|----|----|----|--|

| p8 | p2 | p9 | p6 | p0       | p8 | р6 | p9 |  |

| X  | X  | X  | X  |          |    |    |    |  |

|                | Rena | ame Tab | ole      |        |    |

|----------------|------|---------|----------|--------|----|

| Arch. Register |      | Phys    | ical Reg | gister |    |

| x2             | p0   | p8      | p2       | р6     | p2 |

| x3             | p5   | p9      | p5       |        |    |

| (i) [1 pt] After completing rollback, should an exception be raise | (i | i) | [1 · | nt] | After | completing | rollback. | should a | n exception | be raised | 12 |

|--------------------------------------------------------------------|----|----|------|-----|-------|------------|-----------|----------|-------------|-----------|----|

|--------------------------------------------------------------------|----|----|------|-----|-------|------------|-----------|----------|-------------|-----------|----|

Yes No

The pagefault occurred along a mispredict path. Exceptions caused by rolledback instructions must be suppressed.

(ii) [1 pt] After completing rollback, at what PC should execution continue at? Write exception if execution should continue at the exception handler.

ff

### Q6. [10 pts] Multithreading (MT2)

- (a) Match each of advantages and disadvantages to the most appropriate type of multi-threading. Each advantage/disadvantage should only be used once, so use it for the type of multithreading it *best* applies to. **Keep scratch work away from the multiple choice options for each question.**

- 1. Not possible on a single-issue processor.

- 2. Can, but not necessarily effective at, hiding the throughput losses from both long and very short stalls.

- 3. Useful only for reducing the penalty of very high-cost stalls, where pipeline refill is negligible compared to the stall time.

- 4. Most effective at minimizing both horizontal and vertical waste.

- 5. In general, slows down execution of an individual thread, even a thread that is ready to execute and doesn't have stalls.

|            | stans.                                                                                                                                                                                                     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.         | Doesn't need thread switching to be extremely low overhead.                                                                                                                                                |

| <b>(i)</b> | [2 pts] Coarse-grained multithreading: Advantage:                                                                                                                                                          |

|            | $\bigcirc \ 1 \ \bigcirc \ 2 \ \bigcirc \ 3 \ \bigcirc \ 4 \ \bigcirc \ 5 \ \bullet \ 6$                                                                                                                   |

|            | Disadvantage:                                                                                                                                                                                              |

|            | $\bigcirc$ 1 $\bigcirc$ 2 $\bigcirc$ 3 $\bigcirc$ 4 $\bigcirc$ 5 $\bigcirc$ 6                                                                                                                              |

| (ii)       | [2 pts] Fine-grained multithreading:                                                                                                                                                                       |

|            | Advantage:                                                                                                                                                                                                 |

|            | $\bigcirc 1  \bullet  2  \bigcirc  3  \bigcirc  4  \bigcirc  5  \bigcirc  6$                                                                                                                               |

|            | Disadvantage:  ○ 1 ○ 2 ○ 3 ○ 4 ● 5 ○ 6                                                                                                                                                                     |

| (iii)      | [2 pts] Simultaneous multithreading:                                                                                                                                                                       |

| (111)      | Advantage:                                                                                                                                                                                                 |

|            | $\bigcirc \ 1 \ \bigcirc \ 2 \ \bigcirc \ 3 \ \bullet \ 4 \ \bigcirc \ 5 \ \bigcirc \ 6$                                                                                                                   |

|            | Disadvantage:  1 ○ 2 ○ 3 ○ 4 ○ 5 ○ 6                                                                                                                                                                       |

| E44        |                                                                                                                                                                                                            |

|            | s] Suppose we have a superscalar out-of-order CPU and want to add support for simultaneous multithreading to it. ch of the following CPU components need to be duplicated to maintain program correctness? |

|            | _                                                                                                                                                                                                          |

|            | Program Counter (PC) register                                                                                                                                                                              |

|            | ☐ Physical registers ☐ Functional units                                                                                                                                                                    |

|            |                                                                                                                                                                                                            |