# CS 152/252A

## Spring 2023 Computer Architecture

## Midterm 1

- You have 120 minutes. You're not expected to finish the exam. We provide a variety of questions so you can demonstrate your knowledge on the topics you know best.

- You must write your student ID on the bottom-left of every page of the exam (except this first one). You risk losing credit for any page you don't write your student ID on.

- For questions with length limits, do not use semicolons or dashes to lengthen your explanation.

- The exam is closed book, no calculator, and closed notes, other than two double-sided cheat sheet that you may reference.

| For 1      | multiple choice questions,          |  |

|------------|-------------------------------------|--|

|            | means mark all options that apply   |  |

| $\bigcirc$ | means mark a single choice          |  |

|            | First name                          |  |

|            | Last name                           |  |

|            | SID                                 |  |

|            | Exam Room                           |  |

|            | Name and SID of person to the right |  |

|            | Name and SID of person to the left  |  |

Honor code: "As a member of the UC Berkeley community, I act with honesty, integrity, and respect for others."

By signing below, I affirm that all work on this exam is my own work, and honestly reflects my own understanding of the course material. I have not referenced any outside materials (other than one double-sided cheat sheet), nor collaborated with any other human being on this exam. I understand that if the exam proctor catches me cheating on the exam, that I may face the penalty of an automatic "F" grade in this class and a referral to the Center for Student Conduct.

Discussion TAs (or None)

#### Point Distribution

| Q1. | Iron Law: Doesn't Bend or Break                       | 15      |

|-----|-------------------------------------------------------|---------|

| Q2. | ISAs (oh my)                                          | 15      |

| Q3. | Pipelining: Bypass Extravaganza                       | 30      |

| Q4. | Make More Cache                                       | 30      |

| Q5. | Microding: That's So Fetch                            | 24      |

| Q6. | Virtual Memory + Caches                               | 25 + 10 |

| Q7. | (CS252 Only) Virtual Memory: Build Your Own Hierarchy | 15      |

|     | Total                                                 | 164     |

#### THIS PAGE IS INTENTIONALLY LEFT BLANK

### Q1. [15 pts] Iron Law: Doesn't Bend or Break

(a) [5 pts] What are the tradeoffs if we add support for the following CISC instruction by turning our 5-stage RISC pipeline into a **6-stage pipeline**, with a second decode stage after the original decode stage?

The instruction:

```

MEMADD rd, rs1, rs2

```

Its functionality:

```

M[R[rd]] = R[R[rs1]] + R[R[rs2]]

```

The proposed way of implementing this instruction is the following:

- Read R[rs1], R[rs2], and R[rd] from the register file.

- Read R[R[rs1]] and R[R[rs2]] from the register file.

- Compute R[R[rs1]] + R[R[rs2]].

- Store the above result into memory, i.e. into M[R[rd]].

#### **Important assumptions:**

Assume the register file supports at most 3 reads at a time.

Assume the instruction is only given inputs that make it execute correctly (no edge cases or exceptions).

For each of the following terms of the Iron Law, state whether the term will Increase, Decrease, or No Change and explain why with at most 2 sentences.

(i) Instructions / program

Increase

Decrease

No Change

Decrease. Rather than writing out multiple RISC instructions that accomplish the same functionality, we can call this single CISC instruction.

(ii) Cycles / instruction

Increase

Decrease

No Change

Increase. We will likely have to stall more often due to multiple instructions wanting to read from the register file. This is a structural hazard that can be solved by stalls in our case, which increases our CPI. OR: Increase, since having an additional pipeline stage will result in a larger penalty on a branch mispredict. (NOTE: In this question, we assume that we cannot add more read ports to the register file).

| Time / cycle                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Increase                                                                                                                                                                                                                                                                                             |

| O Decrease                                                                                                                                                                                                                                                                                           |

| No Change                                                                                                                                                                                                                                                                                            |

| Increase. The decode stage may take longer than before in order to include the more complex logic of decoding this CISC instruction. OR: No change, if the decode stage even with the added complexity is still less than the longest stage (e.g. potentially memory).                               |

| lowing subparts in this question, assume the RISC-V pipeline currently only has support for <i>decoding</i> floating point so but <b>not</b> actually executing them. For example, if the programmer writes a floating point instruction, the instruction tly be equivalent to a NOP (no operation). |

| stion, we'll consider the tradeoffs in how we might be able to add a floating point unit to the RISC-V pipeline in order be able to execute floating point instructions.                                                                                                                             |

| s] What are the tradeoffs if we add an <b>unpipelined</b> floating point unit to the RISC-V pipeline?                                                                                                                                                                                                |

| each of the following terms of the Iron Law, state whether the term will <b>Increase, Decrease, or No Change</b> an ain why with <b>at most 2</b> sentences.                                                                                                                                         |

| Instructions / program                                                                                                                                                                                                                                                                               |

| ○ Increase                                                                                                                                                                                                                                                                                           |

| O Decrease                                                                                                                                                                                                                                                                                           |

| No Change                                                                                                                                                                                                                                                                                            |

| No change. Adding an FP unit affects the pipeline, not the program. OR: Decrease. We can replace software float emulation with less FP instructions.                                                                                                                                                 |

| Cycles / instruction                                                                                                                                                                                                                                                                                 |

| ○ Increase                                                                                                                                                                                                                                                                                           |

| Decrease                                                                                                                                                                                                                                                                                             |

| No Change                                                                                                                                                                                                                                                                                            |

| No change. The FP unit can be added in parallel with the ALU in the execute stage without changing the number of cycles per instruction.                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                      |

| Increase                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                            |

| O Decrease                                                                                                                                                                                                                                                                                                                                                                                 |

| O No Change                                                                                                                                                                                                                                                                                                                                                                                |

| Increase. Since the FP unit is unpipelined, all stages must take at least as long as the FP unit. Due to the FP unit's complexity, this will likely increase the time per stage (time per cycle). OR: No change. If the FP unit is not very complex and has low throughput, then adding it may not actually impact the critical path, resulting in no actual change to the time per cycle. |

| What are the tradeoffs if we add a <b>pipelined</b> floating point unit to the RISC-V pipeline?                                                                                                                                                                                                                                                                                            |

| h of the following terms of the Iron Law, state whether the term will <b>Increase</b> , <b>Decrease</b> , <b>or No Change</b> a why with <b>at most 2</b> sentences.                                                                                                                                                                                                                       |

| structions / program                                                                                                                                                                                                                                                                                                                                                                       |

| ○ Increase                                                                                                                                                                                                                                                                                                                                                                                 |

| O Decrease                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul><li>No Change</li></ul>                                                                                                                                                                                                                                                                                                                                                                |

| No change. Adding an FP unit affects the pipeline, not the program. OR: Decrease. We can replace software float emulation with less FP instructions.                                                                                                                                                                                                                                       |

| ycles / instruction                                                                                                                                                                                                                                                                                                                                                                        |

| Increase                                                                                                                                                                                                                                                                                                                                                                                   |

| O Decrease                                                                                                                                                                                                                                                                                                                                                                                 |

| O No Change                                                                                                                                                                                                                                                                                                                                                                                |

| Increase. Adding the FP unit will result in more pipeline stages. As a result, on FP data hazards, we will likely need to stall for stages than before, thus increasing CPI. (Note: We could potentially add bypassing or earlier writeback for integer instructions compared to FP instructions, therefore not impacting the latency of integer instructions.)                            |

| me / cycle                                                                                                                                                                                                                                                                                                                                                                                 |

| Increase                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul><li>Decrease</li></ul>                                                                                                                                                                                                                                                                                                                                                                 |

| <ul><li>No Change</li></ul>                                                                                                                                                                                                                                                                                                                                                                |

| No change. Since the FP unit is pipelined, we can maintain the time per cycle by increasing the number of stages in the pipeline to accommodate the FP unit taking longer (but this time, pipelined!).                                                                                                                                                                                     |

| 1 · · ·                                                                                                                                                                                                                                                                                                                                                                                    |

SID: \_\_\_\_\_

## Q2. [15 pts] ISAs (oh my)

Suppose we have the following program:

```

int remainder(int a, int b) {

while (a >= b) {

a = a - b;

}

return a;

}

```

For a RISC architecture, Our RISC-V compiler generates the following assembly code:

```

loop:

blt x1, x2, done

sub x1, x1, x2

j loop

done:

...

```

Meanwhile, our Stack architecture includes the following instructions:

| add Instruction | Definition                                                               |

|-----------------|--------------------------------------------------------------------------|

| PUSH addr       | load value at addr; push value onto stack                                |

| POP addr        | pop stack; store value to addr                                           |

| SLT             | pop two values from the stack;                                           |

| SLI             | if the first is less than the second, push 1 onto the stack, else push 0 |

| SUB             | pop two values from the stack; subtract the second from the first;       |

| ЗОВ             | push result onto stack                                                   |

| BNEZ label      | pop value from stack; if it's not zero, branch to label;                 |

| DNEZ label      | else, continue with next instruction                                     |

| JUMP label      | continue execution at location label                                     |

Our stack compiler generates the following assembly code (assume a is initially stored at 0x8000 and b is initially stored at 0x8004:

```

loop:

PUSH 0x8004

PUSH 0x8000

SLT

BNEZ done

PUSH 0x8004

PUSH 0x8000

SUB

POP 0x8000

JUMP loop

done:

```

Assume that RISC-V instructions are 4 bytes each. Assume a Stack instruction occupies three bytes if it takes an address or label; other instructions occupy one byte. Assume data vales are 4 bytes each.

| (a) [2 pts] How many bytes is the RISC program?                          |

|--------------------------------------------------------------------------|

| O 10                                                                     |

| <ul><li>12</li></ul>                                                     |

| O 14                                                                     |

| O 16                                                                     |

| <b>(b)</b> [2 pts] How many bytes is the Stack program?                  |

| O 13                                                                     |

| O 73                                                                     |

| <b>2</b> 3                                                               |

| ○ 33                                                                     |

| Assume $a=7$ and $b=3$ .                                                 |

| (c) [2 pts] How many instruction bytes are fetched in the RISC program?  |

| O 18                                                                     |

| O 24                                                                     |

| <ul><li>28</li></ul>                                                     |

| ○ 36                                                                     |

| (d) [2 pts] How many instruction bytes are fetched in the Stack program? |

| ○ 33                                                                     |

| O 52                                                                     |

| O 46                                                                     |

| <b>6</b> 56                                                              |

| (e) [2 pts] How many data bytes are loaded/stored in the RISC program?   |

| • 0                                                                      |

| O 16                                                                     |

| O 32                                                                     |

| O 40                                                                     |

| (f) [2 pts] How many data bytes are loaded/stored in the Stack program?  |

| O 16                                                                     |

| O 32                                                                     |

| <ul><li>48</li></ul>                                                     |

| O 52                                                                     |

|                                                                          |

|       | n Law to justify your answer in at most 2 sentences.                                                                                                                                                                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPI a | ISC program has less instructions per program compared to the Stack program, assuming that time per cycle is equivalent for both. Thus, the RISC program will take less time and be than the Stack version of the program. |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                            |

(g) [3 pts] Which ISA is better for the given implementations?

## Q3. [30 pts] Pipelining: Bypass Extravaganza

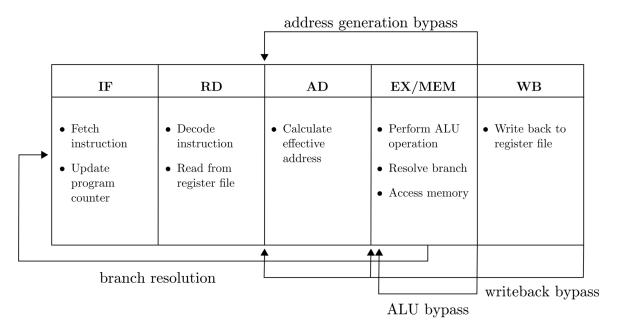

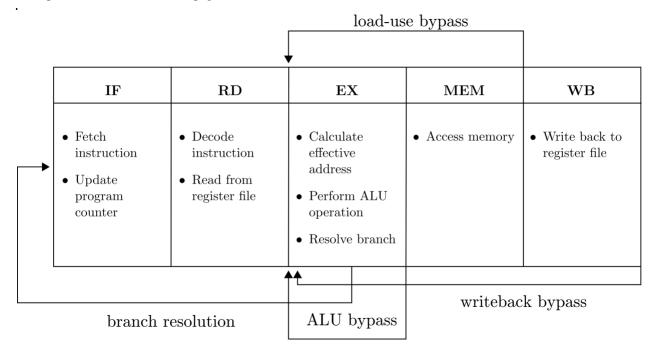

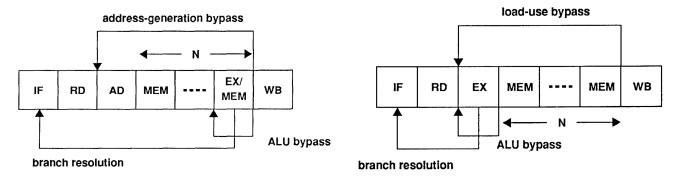

We introduce the Address Generation Interlock (AGI) pipeline below, which eliminates the load-use hazard of our more conventional Load-Use Interlock (LUI) pipeline. In turn, we deal with an address generation hazard, which warrants the address generation bypass path. In this problem, we will analyze the performance of this pipeline.

Parts (a) through (c) in this problem will be analyzing the following code snippet applied on the AGI pipeline. Register s0 holds the address of an array whose elements are addresses that point randomly to other elements of the array. Assume that the register file does not support reading the new value of a register in the same cycle that it is being written, and that none of the load operations access memory outside of the array bounds.

- (a) [2 pts] What does the code snippet above seem to be doing?

- Vector addition

- O Computing the sum of array elements

- Pointer chasing

- Initializing a C struct

- (b) Analyze the code on the AGI pipeline. Assume that **the address generation bypass has not been added** to the pipeline for this part. We will be working with an **always-taken branch predictor**. Assume memory accesses take one cycle.

- (i) [6 pts] Fill in the pipeline diagram on the following page for **TWO iterations of the loop**, assuming that the branch condition evaluates to true both times.

- (ii) [3 pts] What is the CPI (cycles per instruction) for the **100 iterations of the loop** on the AGI pipeline? (Do not include the initial add and addi instructions.)

|    | Instructions       | _ | 7 | က | 4  | 2  | 9  | 7 | 8 | 6 | 10 | 7 | 12 | 13 | 4 | 15 | 16 | 17 | 18 | 19 |  |  |

|----|--------------------|---|---|---|----|----|----|---|---|---|----|---|----|----|---|----|----|----|----|----|--|--|

| _  | 1 add t2, x0, s0   | Ц | Q | 4 | XM | M  |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 7  | addi t1, x0, 0     |   | L | ۵ | ∢  | ΣX | ≥  |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| က  | 3 addi t0, x0, 100 |   |   | ш | Ω  | ∢  | ΣX | ≥ |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 4  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 2  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 9  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 7  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| œ  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 6  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 10 |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 7  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 12 |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 13 |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 4  |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 15 |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 16 |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 17 |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| 18 |                    |   |   |   |    |    |    |   |   |   |    |   |    |    |   |    |    |    |    |    |  |  |

| SID:     | Instructions        | _ | 7 | က | 4      | 2        | 9 | 7    | ω | 6 | 10 11 | 12  | 13 | 4 | 15 | 16 | 1 | 18 | 19 |   |  |  |

|----------|---------------------|---|---|---|--------|----------|---|------|---|---|-------|-----|----|---|----|----|---|----|----|---|--|--|

| 7        | add t2, x0, s0      | Щ | Ω | ⋖ | ×      | >        |   |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| 7        | addi t1, x0, 0      |   | щ | Ω | ^<br>∢ | ∑<br>X   | > |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| က        | addi t0, x0, 100    |   |   | ш | Ω      | <b>×</b> | X | >    |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| 4        | 4 lw t2, 4(t2)      |   |   |   | Щ      | ۵        | × | MX X | > |   |       |     |    |   |    |    |   |    |    |   |  |  |

| ro       | 5 lw t2, -4(t2)     |   |   |   |        | ш        |   | ۵    | ۵ | × | W WX  |     |    |   |    |    |   |    |    |   |  |  |

| 9        | addi t1, t1, 1      |   |   |   |        |          | ш | ш    | ш |   | X     | >   | _  |   |    |    |   |    |    |   |  |  |

| 7        | 7 bne t0, t1, LOOP  |   |   |   |        |          |   |      |   | ь | D A   | X   | >  |   |    |    |   |    |    |   |  |  |

| œ        | 8 lw t2, 4(t2)      |   |   |   |        |          |   |      |   |   | F D   | ∢ - | X  | > |    |    |   |    |    |   |  |  |

| တ        | 9 lw t2, -4(t2)     |   |   |   |        |          |   |      |   |   | ш     | Ω   | Ω  | Ω | 4  | X  | > |    |    |   |  |  |

| <b>9</b> | 11 addi t1, t1, 1   |   |   |   |        |          |   |      |   |   |       | ш   | Ш  | L | Ω  | ∢  | X | >  |    |   |  |  |

| 7        | 11 bne t0, t1, LOOP |   |   |   |        |          |   |      |   |   |       |     |    |   | Щ  | Ω  | 4 | X  | >  |   |  |  |

| 12       | :                   |   |   |   |        |          |   |      |   |   |       |     |    |   |    | ш  | : | :  | :  | ÷ |  |  |

| 13       |                     |   |   |   |        |          |   |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| 4        |                     |   |   |   |        |          |   |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| 15       |                     |   |   |   |        |          |   |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| 16       |                     |   |   |   |        |          |   |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| 17       |                     |   |   |   |        |          |   |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| 18       |                     |   |   |   |        |          |   |      |   |   |       |     |    |   |    |    |   |    |    |   |  |  |

| (c) | We now add the address generation bypass path to the pipeline. | We still use an always-taken branch predictor, and we |

|-----|----------------------------------------------------------------|-------------------------------------------------------|

|     | assume memory accesses take one cycle.                         |                                                       |

|     | 40                                                             |                                                       |

(i) [2 pts] What hazard(s) does the address generation bypass path resolve?

Structural

Data

Control

(ii) [4 pts] What is the CPI (cycles per instruction) for the **100 iterations of the loop** on the AGI pipeline after adding the address generation bypass path? (Do not include the initial add and addi instructions.) For your convenience, we have provided another pipeline diagram two pages ahead as scratch space, but it will not be graded.

5/4

(d) [5 pts] In which of the following independent scenario(s) might we prefer the AGI pipeline over our conventional LUI pipeline? Assume that if our data cache memory accesses take N cycles, then we pipeline the MEM stage N times.

Give a **maximum total three sentence justification** on your selection(s). Below is a diagram of the LUI pipeline. Answer options continue on the next page.

Below are diagrams for the AGI and LUI pipelines respectively that illustrates a multiple cycle (thus, pipelined) MEM stage.

|                 | With perfect branch prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | When we need to consume less area with our design                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | When data cache memory accesses take multiple cycles, paired with good branch prediction                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | None of the above                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | Because branch resolution is in a later stage for the AGI pipeline, this adds an extra cycle of delay for mispredicted branches and necessitates a good branch predictor. When we need to use the result of a load, we must stall N cycles for the LUI pipeline, but we can use it immediately for the AGI pipeline.                                                                                                                                                             |

| ( <b>e</b> ) Co | nsider the following code snippet:                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | <pre>lw t1, 0(t2) addi t2, t2, 0x100</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>(</b> i      | ) [3 pts] Suppose that the <i>lw</i> instruction raises a memory address exception, while the <i>addi</i> instruction raises integer overflow exception. For which of the following pipeline designs would this code snippet cause an imprec exception to occur? Select all that apply.                                                                                                                                                                                          |

|                 | Assume that exceptions are handled immediately when they are raised and if two exceptions are raised simultaneously, then the exception corresponding to the earlier instruction is prioritized.                                                                                                                                                                                                                                                                                 |

|                 | A single cycle non-pipelined machine                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | The AGI pipeline above                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | A modified LUI pipeline with the MEM stage split into M1 and M2 stages (memory writes and exception occur in M2)                                                                                                                                                                                                                                                                                                                                                                 |

|                 | None of the above                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (i              | ) [5 pts] Which of the following hardware modifications would add precise exception support to the design(s) the raised imprecise exceptions? Select all that apply. Assume that all modifications you select will be implemented conjunction.                                                                                                                                                                                                                                   |

|                 | Give a <b>maximum total two sentence justification</b> on how your selected modification(s) would resolve the imprec exception(s).                                                                                                                                                                                                                                                                                                                                               |

|                 | Stall throwing ALU-related exceptions by one cycle                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | Hold exception flags in pipeline until commit point                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | Add an additional read port to the regfile and to memory                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | None of the above: all pipelines support precise exceptions for this code snippet                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | The issue is that the X stage exception gets thrown before the MEM stage exception because of the extra M1 stage, so we should hold the flags in a pipeline to preserve the chronology, and finally throw the exception when we reach the commit point, which is M2. Though stalling the ALU-related exception would help us just for this code snippet instance, it lends to other imprecise exception issues, and the additional read port is just wasteful for this scenario. |

SID: \_\_\_\_\_

|    | Instructions       | _ | 7 | က | 4  | 2  | 9  | 7 | œ | 6 | 9 | 7 | 12 | 13 | 4 | 12 | 16 | 17 | 18 | 19 |  |  |

|----|--------------------|---|---|---|----|----|----|---|---|---|---|---|----|----|---|----|----|----|----|----|--|--|

| -  | add t2, x0, s0     | Щ | ۵ | ∢ | ΣX | >  |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 7  | 2 addi t1, x0, 0   |   | Щ | Ω | ∢  | Σ× | >  |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| က  | 3 addi t0, x0, 100 |   |   | ட | Ω  | ⋖  | ΣX | ≥ |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 4  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 5  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 9  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 7  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| œ  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 6  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 10 |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 7  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 12 |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 13 |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 4  |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 15 |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 16 |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 17 |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| 18 |                    |   |   |   |    |    |    |   |   |   |   |   |    |    |   |    |    |    |    |    |  |  |

| SID      | Instructions        | 1 | 7 | က | 4  | 2  | 9      | 7      | 8 | 9        | 10 11 | 1 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 |  |  |

|----------|---------------------|---|---|---|----|----|--------|--------|---|----------|-------|------|----|----|----|----|----|----|----|--|--|

| 1        | add t2, x0, s0      | Щ | Ω | ⋖ | ΜX | >  |        |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

| 7        | addi t1, x0, 0      |   | ш | Ω | ∢  | ΣX | >      |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

| ო        | addi t0, x0, 100    |   |   | ш | ۵  | <  | ΣX     | >      |   |          |       |      |    |    |    |    |    |    |    |  |  |

| 4        | 4 lw t2, 4(t2)      |   |   |   | ш  | ۵  | ^<br>< | N<br>X | > |          |       |      |    |    |    |    |    |    |    |  |  |

| Ŋ        | lw t2, -4(t2)       |   |   |   |    | ш  | Ω      | ۵      | × | ><br>WX  | >     |      |    |    |    |    |    |    |    |  |  |

| 9        | addi t1, t1, 1      |   |   |   |    |    | ш      | ш      | ۵ | ×        | W WX  | >    |    |    |    |    |    |    |    |  |  |

| 7        | 7 bne t0, t1, LOOP  |   |   |   |    |    |        |        | ш | <i>Р</i> | X     | >    |    |    |    |    |    |    |    |  |  |

| <b>∞</b> | lw t2, 4(t2)        |   |   |   |    |    |        |        |   | ь        | О     | X    | >  |    |    |    |    |    |    |  |  |

| တ        | 9 lw t2, -4(t2)     |   |   |   |    |    |        |        |   |          | П     | 0    | 4  | ×  | >  |    |    |    |    |  |  |

| 15       | 10 addi 11, 11, 1   |   |   |   |    |    |        |        |   |          | Щ     | ш.   |    | ⋖  | ×  | >  |    |    |    |  |  |

| 7        | 11 bne t0, t1, LOOP |   |   |   |    |    |        |        |   |          |       |      | Щ  | Ω  | 4  | X  | >  |    |    |  |  |

| 12       |                     |   |   |   |    |    |        |        |   |          |       |      |    | LL | :  | :  | ÷  | ÷  |    |  |  |

| 13       |                     |   |   |   |    |    |        |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

| 14       |                     |   |   |   |    |    |        |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

| 15       | 10                  |   |   |   |    |    |        |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

| 16       |                     |   |   |   |    |    |        |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

| 17       | h                   |   |   |   |    |    |        |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

| 18       |                     |   |   |   |    |    |        |        |   |          |       |      |    |    |    |    |    |    |    |  |  |

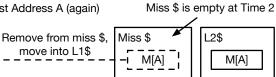

## Q4. [30 pts] Make More Cache

| (i) Tag                                                  |                                                                       |                    |                      |              |              |

|----------------------------------------------------------|-----------------------------------------------------------------------|--------------------|----------------------|--------------|--------------|

| 1                                                        |                                                                       |                    |                      |              |              |

| (ii) Index                                               |                                                                       |                    |                      |              |              |

| 2                                                        |                                                                       |                    |                      |              |              |

| iii) Offset                                              |                                                                       |                    |                      |              |              |

| 5                                                        |                                                                       |                    |                      |              |              |

| iscussed in Part (a).                                    | mpty 2-way set-assoo<br>Assume that we fill V<br>bit index, and 4 bit | Vay 0 before Way 1 | . The address with r |              |              |

| Address                                                  | Set 0, Way 0                                                          | Set 0, Way 1       | Set 1, Way 0         | Set 1, Way 1 | Hit (Y/N)    |

|                                                          |                                                                       | Set 0, Way 1       | Set 1, way 0         | Set 1, way 1 | IIII (1/N)   |

| 0b1000 1000                                              | $(A) \frac{0x4}{}$                                                    |                    |                      |              | N            |

|                                                          |                                                                       |                    |                      |              |              |

| 0ъ0000 0000                                              |                                                                       | 0x0                |                      |              | N            |

| 0b0000 0000<br>0b1000 0010                               |                                                                       | 0x0                |                      |              | (B) Y        |

|                                                          |                                                                       | 0x0                | 0x2                  |              | (B) <b>Y</b> |

| 0ь1000 0010                                              |                                                                       | 0x0<br>(F)         | 0x2                  | 0.20         | (B) Y        |

| 0b1000 0010<br>0b0101 0010                               | (H) 0x2                                                               |                    | 0x2                  | 0x0<br>(C)   | (B) Y  N  N  |

| 0b1000 0010<br>0b0101 0010<br>0b0001 0000                | (H) 0x2                                                               |                    | 0x2                  |              | (B) Y  N  N  |

| 0b1000 0010<br>0b0101 0010<br>0b0001 0000<br>0b0100 0000 | (H) 0x2                                                               | (F)                | 0x2                  |              | (B) Y  N  N  |

(c) [2 pts] Determine the average memory access time (AMAT) of the following program description. Assume the hit time of the L1 cache is 4ns and the L2 access time is 20ns. Of your 10 memory accesses, 2 are L1 hits. Assume all L1 misses are resolved in the L2.

0x2

N

(G)

(F)

0x0

Only your answer in the small box will be graded; you may use the bigger box on the next page for work, but it will not be graded.

20 ns AMAT = HitTime + MissRate \* MissPenalty AMAT = 4ns + (8/10)\*20ns = 4 + 16 = 20nsAMAT = 20ns

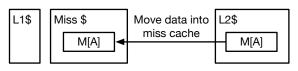

(d) [4 pts] Now let's consider the effect of adding a miss cache to our cache hierarchy. A miss cache, similar to a victim cache, is a small, fully associative cache that is placed between the L1 and L2 caches. When a cache line is first requested, it is placed in the miss cache instead of the L1 cache. If the L1 cache misses on the line again while it is still present in the miss cache, it is moved into the L1 cache.

When an address is requested, the processor first checks the L1 cache for the line, then the miss cache, and then, the L2 cache.

Additionally, the L1 cache and miss cache are exclusive. That is, you will not find the same cache line present in both the miss cache and the L1 cache — a line may exist in at most one cache at a time.

M[A]

Time 0: Request Address A

Select all that apply for what is true about a miss cache.

- A miss cache naturally adheres to the following replacement policies: MRU (most recently used), when moving data to the L1, and FIFO (first-in-first-out), when evicting due to full capacity.

- A miss cache is always helpful, but we may not always add it to our design because it consumes area.

- A miss cache aims to prevent L1 cache pollution by filtering out data that is less spatially local.

L1\$

- A miss cache aims to prevent L1 cache pollution by filtering out data that is less temporally local.

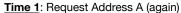

- (e) [9 pts] We will now analyze the same access pattern from part (b) with the addition of a miss cache, which is explained in part (c).

Again, fill in the following table with the hexadecimal tags that populate each cache line. We will not grade the contents of the table and will only grade your answer to part (i) below the table.

Assume an initially empty 2-way set-associative L1 cache with a FIFO replacement policy. Assume that we fill Way 0 before Way 1. The address with respect to the L1 cache has the following division: 3 bit tag, 1 bit index, and 4 bit offset. Assume an initially empty fully associative miss cache, also with a FIFO replacement policy. The address with respect to the miss cache has the following division: 4 bit tag and 4 bit offset.

|             |                   |                   | Cache Acc         | ess Table         |                 |             |             |              |

|-------------|-------------------|-------------------|-------------------|-------------------|-----------------|-------------|-------------|--------------|

| Address     | L1 Set 0<br>Way 0 | L1 Set 0<br>Way 1 | L1 Set 1<br>Way 0 | L1 Set 1<br>Way 1 | Hit<br>(Y/N)    | MC<br>Way 0 | MC<br>Way 1 | Hit<br>(Y/N) |

| 0b1000 1000 |                   |                   |                   |                   |                 | 0x8         |             | (F) N        |

| 0ъ0000 0000 |                   |                   |                   |                   |                 |             | (A)<br>0x0  | N            |

| 0b1000 0010 | 0x4               |                   |                   |                   | (I) <b>N</b>    |             |             | (B) <b>Y</b> |

| 0b0101 0010 |                   |                   |                   |                   |                 | (G)<br>0x5  |             | N            |

| 0ъ0001 0000 |                   |                   |                   |                   |                 |             | 0x1         | N            |

| 0b0100 0000 | (C)               |                   |                   |                   |                 | 0x4         |             | N            |

| 0b1000 1101 |                   |                   |                   |                   | (D)<br><u>Y</u> | (H)         |             |              |

| 0b0010 0000 |                   |                   |                   |                   |                 |             | 0x2         | N            |

| 0b0011 0000 |                   |                   |                   |                   |                 | (E)<br>0x3  |             | N            |

(i) What are the hexadecimal tags or hit values (in Y/N) for the cells labeled as A-H?

(f) [4 pts] Determine the average memory access time (AMAT) of the following program description using this miss cache-based system. Once again, assume the hit time of the L1 cache is 4ns, and the L2 access time is 20ns. Additionally, assume the miss cache access time is 10ns. Of your 10 memory accesses, 2 are L1 hits. Another 2 are resolved in the miss cache. Assume all L1 and miss cache misses are resolved in the L2.

Only your answer in the small box will be graded; you may use the bigger box for work, but it will not be graded.

```

AMAT w.r.t L1$ = HitTime + MissRate * MissPenalty

AMAT w.r.t L1$ = 4ns + (8/10)*(AMAT w.r.t. Miss $)

AMAT w.r.t Miss $ = 10ns + (6/8)*20ns = 25ns

AMAT w.r.t L1$ = 4ns + (8/10)*(10ns + (6/8)*20ns) = 4ns + (8/10)*25ns = 24ns

```

SID: \_\_\_\_\_

### Q5. [24 pts] Microding: That's So Fetch

**Skip Registering** provides conditional execution without branches and control dependencies. Each instruction is associated with a third register, rs3, called a **skip register**. If the skip register evaluates to zero, the instruction executes normally. If the skip register evaluates to a non-zero value, the instruction is treated as a no-op.

We extend the RISC-V ISA to add skip registering as follows. We allow any of the 32 RISC-V register (x0 through x31) to be used as a skip register. We also change the encoding of RISC-V instructions to allow them to be skip registered on the value of any of the 32 RISC-V registers.

We denote skip registered instructions in assembly by prefixing them with the skip register in parenthesis before the instruction. For example:

denotes that the li instruction is skip registered on the register x0. Since x0 always evaluates to 0, the li instruction will be executed and x1 will be set to 1. If, after the execution of the previous instruction, the following instruction is executed:

The value of x1 will remain unchanged at 1 because the skip register (x1) evaluates to a non-zero value and the instruction is treated as a no-op.

With these changes, we can implement conditional execution without branches. For example, consider the C code:

```

if (x1 == 0) { // x2 != 0

x3 = x4;

} else { // x2 == 0

x3 = x5;

}

```

where the values of C variables x1, x2, x3, x4, x5 are stored in the RISC-V registers x1, x2, x3, x4, x5. With skip registering, we can express this code in assembly without a branch instruction, and using x2 as an intermediate:

```

(x0) sltiu x2, x1, 1 // x2 = 1 if x1 == 0, else x2 = 0

(x1) mov x3, x4 // executes if x1 == 0

(x2) mov x3, x5 // executes if x1 != 0 (i.e. x2 == 0)

```

#### (a) What Does This Skippy Code Do?

Given the following block of skip-registered RISC-V code:

```

(x0) li x1, 1

(x0) sltiu x2, x1, 1  // x2 = 1 if x1 == 0, else x2 = 0

(x0) li x5, 0

(x0) li x6, 0

(x1) addi x6, x6, 4

(x2) addi x6, x6, 2

# Comment A

(x0) add x5, x5, x6

(x1) li x7, 0

(x2) li x7, 5

# Comment B

```

Answer the following questions:

- (i) [2 pts] At Comment A, what is the value of x5?

- (ii) [2 pts] At Comment A, what is the value of x6?

- (iii) [2 pts] At Comment B, what is the value of x5?

- (iv) [2 pts] At Comment B, what is the value of x7?

5

#### (b) [12 pts] Microcoded Implementation

To implement skip registering, we must update FETCH0 to ensure instructions with non-zero valued skip registers are not run, while instructions with *zero* valued skip registers *are* run.

Implement this new fetch instruction starting at FETCH0 in the microcode table provided on page 21 of the exam booklet.

**Important:** Your microcode implementation should only use the **optimal, minimal** amount of lines possible to achieve this skip-registering fetch functionality.

Helpful notes:

- As a reminder, all instructions under this skip registering scheme will be associated with an additional register rs3. Although this change is not reflected in Handout 1, the RegSel mux has been extended to include rs3, enabling this new instruction argument to be accessed from the bits of an instruction just as how we can access rd, rs1, and rs2 when applicable.

- You may also find it helpful to draw inspiration from the original, non-skip register enabled implementation of FETCH0 included on page 21 of the exam booklet.

- Focus first on making your implementation correct. Then, focus on making your correct implementation optimal.

Old Microcode Implementation of FETCH0 for a Non-Skip Registered System

| ŀ         |                        | -               |                    |

|-----------|------------------------|-----------------|--------------------|

| Ld Sel Wr | Ld Ld ALOOP ALO MA Mer | Ld Wr En Sel En | l µBr   wext state |

| * PC 0    | * *                    | 0 * 0           | *                  |

| * 0       | 0 0 *                  | 1 * 0           | *<br>•             |

| 0 PC 1    | * INC_A_4 1 * 0        | * 0             | *                  |

New Microcode Implementation of FETCH0 for a Skip Registered System

| Next State |         |  |  |  |  |

|------------|---------|--|--|--|--|

| µBr        |         |  |  |  |  |

| lmm<br>En  |         |  |  |  |  |

| lmm<br>Sel |         |  |  |  |  |

| Mem<br>En  |         |  |  |  |  |

| Mem<br>Wr  |         |  |  |  |  |

| MA         |         |  |  |  |  |

| ALU<br>En  |         |  |  |  |  |

| ALUOp      |         |  |  |  |  |

| P P        |         |  |  |  |  |

| A          |         |  |  |  |  |

| Reg<br>En  |         |  |  |  |  |

| Reg        |         |  |  |  |  |

| Reg<br>Sel |         |  |  |  |  |

| E R        |         |  |  |  |  |

| Pseudocode |         |  |  |  |  |

| State      | FETCH0: |  |  |  |  |

Old Microcode Implementation of FETCH0 for a Non-Skip Registered System

| State      |     |                  |                   |          |   |          |           |

|------------|-----|------------------|-------------------|----------|---|----------|-----------|

| Next State |     | *                |                   |          | * | *        | * *       |

| μBr        | -   | z                |                   |          | S | S        | S O       |

| lmm<br>i   | En  | 0                |                   |          | 0 | 0        | 0 0       |

| mm         | Se  | *                |                   |          | * | *        | * *       |

| Mem        | Eu  | 0                |                   |          | 1 | 1        | - 0       |

| Mem        | Wr  | 0                |                   |          | 0 | 0        | 0         |

| MA -       | Γq  | _                |                   |          | 0 | 0        | 0 *       |

| ALU        | Eu  | 0                |                   |          | 0 | 0        | 0 -       |

| ALUOp      |     | *                |                   |          | * | *        | * INC_A_4 |

| <u>а</u>   | Ld  | *                |                   |          | * | *        | * *       |

| ∢ ]        |     | _                |                   | L        | > | <b>O</b> | 0         |

| Reg        | En  | _                |                   | C        | > | >        | ) 0       |

| Reg        | Wr  | 0                |                   | 0        |   |          | ~         |

| Reg        | Sel | PC               |                   | *        |   |          | PC        |

| 쓰 :        | Γq  | *                |                   | _        |   |          | 0         |

| Pseudocode |     | MA ← PC;         | $A \leftarrow PC$ | IR ← Mem |   |          | PC ← A+4  |

| State      |     | FETCH0: MA ← PC; |                   |          |   |          |           |

New Microcode Implementation of FETCH0 for a Skip Registered System

| _          |                                |              |              |            |                         |                        |

|------------|--------------------------------|--------------|--------------|------------|-------------------------|------------------------|

| Next State | *                              | *            | *            | *          | FETCH0                  | *                      |

| µBr        | Z                              | S            | z            | Z          | ZN                      | Q                      |

| lmm<br>En  | 0                              | 0            | 0            | 0          | 0                       | 0                      |

| lmm<br>Sel | *                              | *            | *            | *          | *                       | *                      |

| Mem<br>En  | 0                              | L            | 0            | 0          | 0                       | 0                      |

| Mem<br>Wr  | 0                              | 0            | 0            | 0          | 0                       | 0                      |

| MA         | 1                              | 0            | *            | *          | *                       | *                      |

| ALU<br>En  | 0                              | 0            | <del>-</del> | 0          | 0                       | 0                      |

| ALUOp      | *                              | *            | INC_A_4      | *          | COPY_A                  | *                      |

| В          | *                              | *            | *            | *          | *                       | *                      |

| A<br>Ld    | 1                              | 0            | 0            | _          | *                       | *                      |

| Reg<br>En  | 1                              | 0            | 0            | 1          | 0                       | 0                      |

| Reg<br>Wr  | 0                              | 0            | _            | 0          | 0                       | 0                      |

| Reg<br>Sel | DG                             | *            | PC           | Rs3        | *                       | *                      |

| Ld R       | *                              | <del>-</del> | 0            | 0          | 0                       | 0                      |

| Pseudocode | FETCH0:   MA ← PC;<br>  A ← PC | IR ← Mem     | PC ← A+4     | A ← R[Rs3] | if (NZA)<br>goto FETCH0 | Jump to<br>instruction |

| State      | FETCH0:                        |              |              |            |                         |                        |

#### (c) Can we do better?

(i) [4 pts] Why might skip registering be more useful for a very deeply pipelined CPU instead of a microcoded CPU? You may assume the microcoded CPU uses the implementation presented in class. Limit your answer to 2 sentences (do not use semicolons or dashes to lengthen your response).

Support for skip registers adds at least 2 additional microinstructions per instruction fetch, which isn't worth the overhead of eliminating micro-branches since branches in microcode are relatively cheap. For a pipelined CPU, skip registering avoids the need to bubble incorrectly fetched instructions and avoids the memory penalties of control logic.

ID: 23

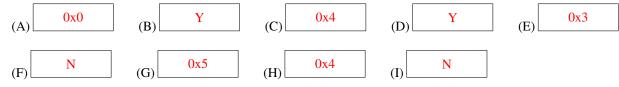

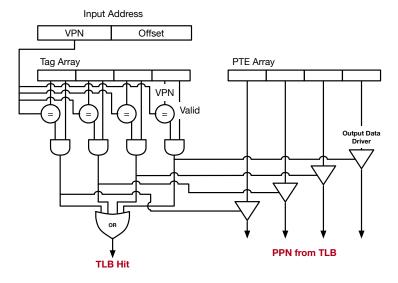

## Q6. [25 + 10 pts] Virtual Memory + Caches

You are given a VIPT (virtually-indexed, physically-tagged) cache implementation (4-way set associative cache) with the following address partitioning for both the cache input and virtual address.

tag bits [31:11] index bits [10:6] line offset [5:0]

Table 4: Cache Address Partitioning

VPN bits [31:9] page offset [8:0]

Table 5: Virtual Address Partitioning

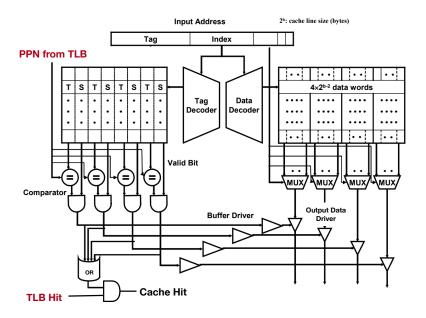

Below you are given a simplified VIPT cache implementation and corresponding TLB that is accessed in parallel. Remember that in a VIPT cache, the tag check is completed using the PPN (physical page number) obtained from a TLB/page-table-walk.

Figure 1: 4-way Fully Set-Associative TLB Implementation

Figure 2: 4-way Set-Associative VIPT Cache Implementation

(a) [11 pts] For simplicity, assume that the TLB always hits, and that there are no page faults (PPN is always valid within a PTE (page table entry)). As seen in the diagrams, the TLB access happens in parallel with the cache lookup, and the "TLB Hit" signal is later used to determine whether the cache entry is valid. Given the block delay expressions for individual components given below and the diagrams of the VIPT cache and TLB, answer the following questions. Keep in mind that the ceil(X) operation returns the smallest integer value that is greater than or equal to X.

| Component                 | Delay equation (ps)                                                                                     |

|---------------------------|---------------------------------------------------------------------------------------------------------|

| Decoder                   | $30 \times (\text{num index bits}) + 80$                                                                |

| Memory array              | $30 \text{ x ceil}(\log_2(\text{num sets})) + 30 \text{ x ceil}(\log_2(\text{num bits per set})) + 100$ |

| Comparator                | 30  x (num tag bits) + 70                                                                               |

| N-to-1 MUX                | $50 \times \text{ceil}(\log_2(N)) + 100$                                                                |

| Output-data/buffer driver | 180                                                                                                     |

| OR Gate                   | 50                                                                                                      |

| AND Gate                  | 40                                                                                                      |

(i) [3 pts] For the longest path from the VPN tag check to the output data in the data cache.

What are the components along the path, along with the delay of the path in ps?

```

VPN -> Comparator (30 x 23 bits + 70 = 760) -> AND Gate (40) -> Buffer Driver (180) -> Comparator (30 x 21 bits + 70 = 700) -> AND Gate (40) + 2 x Buffer Driver (2 x 180) -> Data Output (2080 ps)

```

(ii) [3 pts] For the longest path from the Input Address index to the output data in the data cache. What are the components along the path, along with the delay of the path in ps?

```

Index -> Tag Decoder (30 x 5 bits + 80 = 230) -> Memory Array (30 x 5 + 30 x 7 + 100) -> Comparator (30 x 21 + 70) -> AND Gate (40) + 2 x Buffer Driver (2 x 180) -> Data Output (1790 ps)

```

(iii) [3 pts] For the longest path from the VPN tag check to the cache hit signal in the data cache. What are the components along the path, along with the delay of the path in ps?

```

VPN -> Comparator (30 x 23 bits + 70 = 760) -> AND Gate (40) -> Buffer Driver (180) -> Comparator (30 x 21 bits + 70 = 700) -> AND Gate (40) -> OR Gate (50 ps) -> AND Gate (40 ps) -> Cache Hit (1810 ps)

```

- (iv) [2 pts] Of the three paths given, which is the critical path? Other paths do not need to be considered for the critical path in this question, even though the list given above is not a comprehensive list of all possible paths.

- (i) VPN tag check -> Output data

- (ii) Cache idx -> Output data

- (iii) VPN tag check -> Cache hit

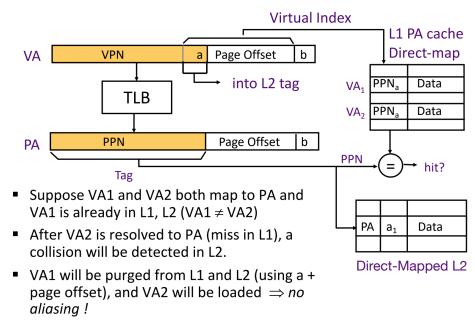

- (b) [4 pts] Does this implementation of a VIPT cache with a parallel TLB have aliasing issues? If so, what is causing the aliasing? If not, explain why aliasing would not be an issue. You may write at most 2 sentences of explanation.

Here aliasing is caused by bits 10+9 overlapping between the cache index and the VPN bits. As a result, two different virtual addresses that map to the same physical address may be present in the cache at the same time, but in different indexed sets due to their differing index bits.

- (c) Regardless of your answer to part b, assume that the cache does indeed have aliasing issues. To solve them, the overall cache organization can be modified.

- (i) [6 pts] Assuming fixed page size and fixed overall cache size, what modifications can be done to the cache and TLB organization to ensure there are no aliasing issues? You may write at most 3 sentences of explanation.

You can put the TLB resolve the PPN before the cache indexing/decoding occurs. This would turn the cache into a physically-indexed and physically-tagged cache, removing any aliasing issues resulting from the VIPT cache. You can also increase the associativity and reduce the sets

(ii) [4 pts] What is the estimated impact on critical path? You may write at most 2 sentences of explanation.