### CS162 Operating Systems and Systems Programming Lecture 9

### Monitors (Continued) Scheduling Core Concepts and Classic Policies

Professor Natacha Crooks https://cs162.org/

Slides based on prior slide decks from David Culler, Ion Stoica, John Kubiatowicz, Alison Norman and Lorenzo Alvisi

# Recall: Monitors are better!

# Use *locks* for mutual exclusion and *condition variables* for scheduling constraints

### Monitor: a lock and zero or more condition variables for managing concurrent access to shared data

A monitor is a paradigm for concurrent programming

- Some languages like Java provide this natively

- Most others use actual locks and condition variables

# Recall: Wait & Signal Pattern

```

...

acquire(&buf_lock)

...

cond_signal(&buf_CV);

...

release(&buf_lock));

```

```

acquire(&buf_lock);

...

while (isEmpty(&queue)) {

cond_wait(&buf_CV,&buf_lock);

}

...

lock.Release();

```

# Hoare Semantics

```

Thread A Thread B

...

acquire(&buf_lock)

...

cond_signal(&buf_CV);

...

release(&buf_lock));

...

release(&buf_lock));

...

lock.Release();

```

- 1. When call signal, handover buf\_lock to thread B.

- 2. Thread B gets immediately scheduled (nothing can run in between).

- 3. Thread B eventually releases lock.

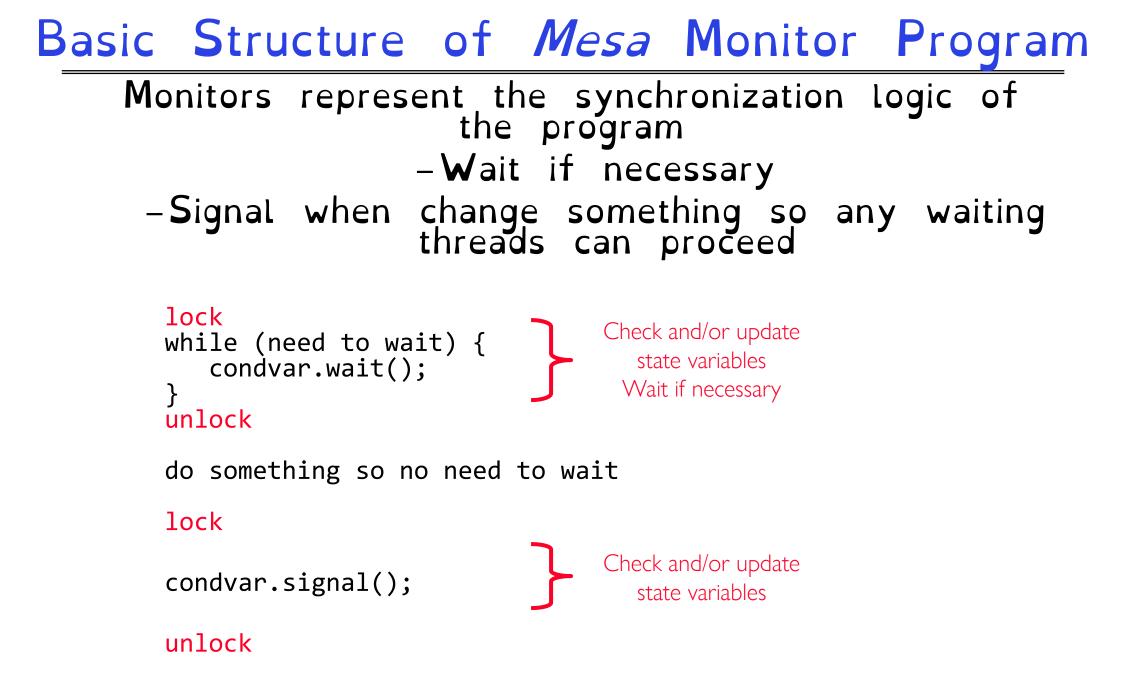

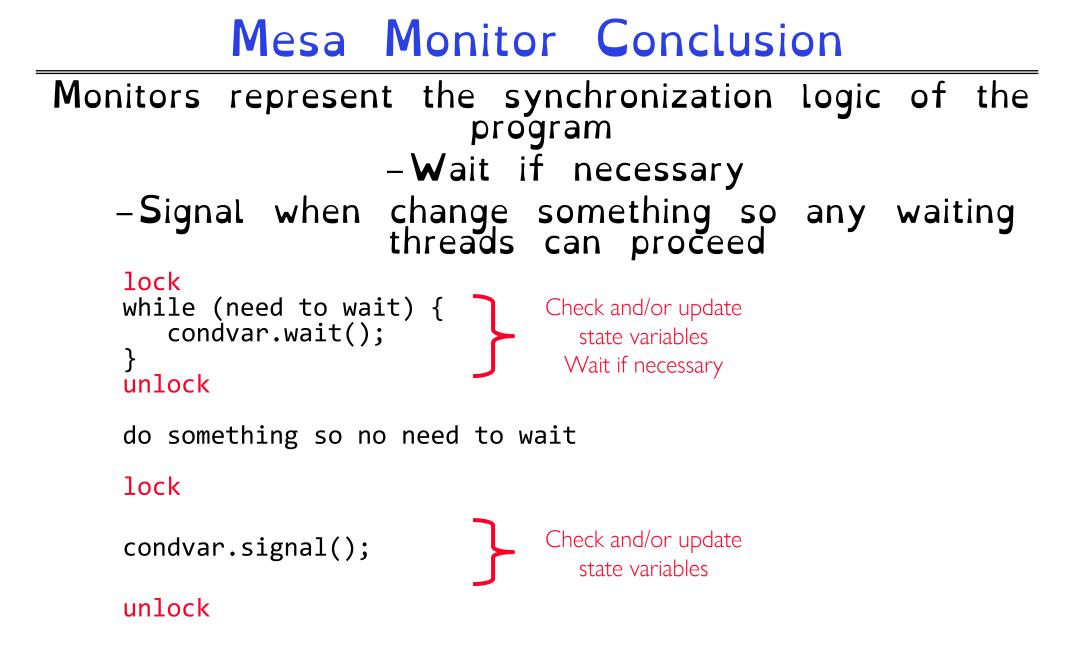

# Mesa Semantics

# Thread A ... acquire(&buf\_lock) ... cond\_signal(&buf\_CV); ... release(&buf\_lock));

### Thread B

```

acquire(&buf_lock);

```

```

while (isEmpty(&queue)) {

cond_wait(&buf_CV,&buf_lock);

}

```

```

lock.Release();

```

When call signal, keep lock. Place Thread B on READY queue (no special priority)

Thread A eventually releases buf\_lock.

Thread B eventually gets scheduled and acquires buf\_lock. Thread C may have run in between.

Thread B eventually releases buf\_lock.

# Readers/Writers Problem

Motivation: Consider a shared database - Two classes of users: » Readers - never modify database » Writers - read and modify database - Is using a single lock on the whole database sufficient? » Like to have many readers at the same time » Only one writer at a time

Crooks CS162 © UCB Fall 2022

# Basic Readers/Writers Solution

Correctness Constraints: -Readers can access database when no writers -Writers can access database when no readers or writers -Only one thread manipulates state variables at a time

### Basic structure of a solution:

```

Reader()

Wait until no writers

Access data base

Check out - wake up a waiting writer

Writer()

Wait until no active readers or writers

Access database

Check out - wake up waiting readers or writer

```

# Basic Readers/Writers Solution

### State variables (Protected by a lock called "lock"): » int AR: Number of active readers; initially = 0 » int WR: Number of waiting readers; initially = 0 » int AW: Number of active writers; initially = 0 » int WW: Number of waiting writers; initially = 0 » Condition okToRead = NIL » Condition okToWrite = NIL

## Code for a Reader

```

Reader() {

// First check self into system

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

cond wait(&okToRead,&lock);// Sleep on cond var

WR--;

// No longer waiting

}

AR++;

// Now we are active!

release(&lock);

// Perform actual read-only access

AccessDatabase(ReadOnly);

// Now, check out of system

acquire(&lock);

// No longer active

AR--;

if (AR == 0 && WW > 0) // No other active readers

cond signal(&okToWrite);// Wake up one writer

release(&lock);

```

# Code for a Writer

```

Writer() {

// First check self into system

acquire(&lock);

while ((AW + AR) > 0) { // Is it safe to write?

// No. Active users exist

WW++;

cond wait(&okToWrite,&lock); // Sleep on cond var

// No longer waiting

WW - - ;

// Now we are active!

AW++;

release(&lock);

// Perform actual read/write access

AccessDatabase(ReadWrite);

// Now, check out of system

acquire(&lock);

// No longer active

AW - -;

// Give priority to writers

if (WW > 0) {

cond signal(&okToWrite);// Wake up one writer

} else if (WR > 0) { // Otherwise, wake reader

cond broadcast(&okToRead); // Wake all readers

release(&lock);

```

Use an example to simulate the solution

Initially:

$$AR = 0$$

,  $WR = 0$ ,  $AW = 0$ ,  $WW = 0$

```

R1 comes along (no waiting threads)

AR = 0, WR = 0, AW = 0, WW = 0

Reader()

acquire(&lock)

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R1 comes along (no waiting threads)

AR = 0, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

((AW + WW) > 0) { // Is it safe to read?

while

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R1 comes along (no waiting threads)

AR = 1, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R1 comes along (no waiting threads)

AR = 1, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R1 accessing dbase (no other threads)

AR = 1, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

WR++; // No. Writers exist

cond_wait(&okToRead,&lock);// Sleep on cond var

WR--; // No longer waiting

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly)

acquire(&lock);

AR--;

if (AR == 0 \&\& WW > 0)

```

cond signal(&okToWrite);

release(&lock);

```

Simulation of Readers/Writers Solution

R2 comes along (R1 accessing dbase)

AR = 1, WR = 0, AW = 0, WW = 0

Reader()

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R2 comes along (R1 accessing dbase)

AR = 1, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while

((AW + WW) > 0) { // Is it safe to read?

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R2 comes along (R1 accessing dbase)

AR = 2, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R2 comes along (R1 accessing dbase)

AR = 2, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

R1 and R2 accessing dbase

AR = 2, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

WR++; // No. Writers exist

cond_wait(&okToRead,&lock);// Sleep on cond var

WR--; // No longer waiting

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly)

```

```

acquire(&lock);

AR--;

if (AR == 0 && WW > 0)

Assume readers take a while to

```

Assume readers take a while to access database Situation: Locks released, only AR is non-zero

```

Simulation of Readers/Writers Solution

W1 comes along (R1 and R2 are still accessing dbase)

AR = 2, WR = 0, AW = 0, WW =

0

Writer()

acquire(&lock);

while ((AW + AR) > 0)

WW++;

cond wait (&okToWrite, &lock);/

// Sleep on cond var

longer waiting

WW - - \overline{T}

No

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW---

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {

cond broadcast (&okToRead);

release(&lock);

```

```

Simulation of Readers/Writers Solution

W1 comes along (R1 and R2 are still accessing dbase)

AR = 2, WR = 0, AW = 0, WW =

Ú

Writer() {

acquire(&lock);

while ((AW + AR

WW++;

cond_wait(&okToWrite,&lock);/

No

// Sleep on cond var

longer waiting

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW--

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {

cond broadcast (&okToRead);

release(&lock);

```

- W1 comes along (R1 and R2 are still accessing dbase)

- AR = 2, WR = 0, AW = 0, WW = 1

```

Writer() {

acquire(&lock);

while ((AW + AR) > 0) {

WW++;

cond wait(&okToWrite,&lock);//

Sleep on cond var

No longer waiting

WW - -;

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW-

(WW > 0)

cond signal(&okToWrite);

else_if (WR > 0) {____

cond broadcast (&okToRead);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R3 comes along (R1 and R2 accessing dbase, W1 waiting)

AR = 2, WR = 0, AW = 0, WW = 1

Reader()

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

cond wait(&okToRead,&lock);// Sleep on cond var

// No longer waiting

WR - - \overline{;}

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R3 comes along (R1 and R2 accessing dbase, W1 waiting)

AR = 2, WR = 0, AW = 0, WW = 1

Reader() {

acquire(&lock);

{ // Is it safe to read?

> 0)

while

(AW + WW)

// No. Writers exist

WR++;

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R3 comes along (R1 and R2 accessing dbase, W1 waiting)

AR = 2, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) { // Is it safe to read?

// No. Writers exist

WR++;

// Now we are active!

AR++;

lock.release();

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R3 comes along (R1, R2 accessing dbase, W1 waiting)

AR = 2, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

WR++;

// No. Writers exist

cond wait(&okToRead,&lock);// Sleep on cond var

WR - -;

// No longer waiting

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R1 and R2 accessing dbase, W1 and R3 waiting

AR = 2, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 && WW > 0)

Status:

R1 and R2 still reading

W1 and R3 waiting on okToWrite and okToRead, respectively

```

```

Simulation of Readers/Writers Solution

R2 finishes (R1 accessing dbase, W1 and R3 waiting)

AR = 2, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R2 finishes (R1 accessing dbase, W1 and R3 waiting)

AR = 1, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R2 finishes (R1 accessing dbase, W1 and R3 waiting)

AR = 1, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

cond wait(&okToRead,&lock);// Sleep on cond var

// No longer waiting

WR - - \overline{;}

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - - ;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R2 finishes (R1 accessing dbase, W1 and R3 waiting)

AR = 1, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

cond wait(&okToRead,&lock);// Sleep on cond var

// No longer waiting

WR - - \overline{;}

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R1 finishes (W1 and R3 waiting)

AR = 1, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

### Simulation of Readers/Writers Solution R1 finishes (W1, R3 waiting) AR = 0, WR = 1, AW = 0, WW = 1Reader() { acquire(&lock); while $((AW + WW) > 0) \{ // \text{ Is it safe to read} \}$ // No. Writers exist WR++; // Now we are active! AR++; release(&lock); AccessDBase(ReadOnly); acquire(&lock); AR--; if (AR = 0 && WW > 0)cond signal(&okToWrite); release(&lock);

#### Simulation of Readers/Writers Solution R1 finishes (W1, R3 waiting) AR = 0, WR = 1, AW = 0, WW = 1Reader() { acquire(&lock); while $((AW + WW) > 0) \{ // \text{ Is it safe to read} \}$ // No. Writers exist WR++; // Now we are active! AR++; release(&lock); AccessDBase(ReadOnly); acquire(&lock); AR - -;if (AR == 0 & WW > 0)cond signal(&okToWrite); release(&lock);

```

Simulation of Readers/Writers Solution

R1 signals a writer (W1 and R3 waiting)

AR = 0, WR = 1, AW = 0, WW = 1

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

WR++; // No. Writers exist

cond wait(&okToRead,&lock);// Sleep on cond var

WR--; // No longer waiting

AR++;

// Now we are active!

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR - -;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

W1 gets signal (R3 still waiting)

AR = 0, WR = 1, AW = 0, WW = 1

Writer() {

acquire(&lock);

while ((AW + AR) > 0) {

// Is it safe to write?

// No. Active users exist

WW++;

cond wait(&okToWrite,&lock);// Sleep on cond var

No longer waiting

\overline{WW} - -\overline{T}

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW--

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {_____

cond broadcast (&okToRead);

release(&lock);

```

```

Simulation of Readers/Writers Solution

W1 gets signal (R3 still waiting)

AR = 0, WR = 1, AW = 0, WW = 0

Writer() {

acquire(&lock);

ile ((AW + AR) > 0) { // Is it safe to write?

WW++;

cond wait(&okToWrite, &lock);// Sleep on cond var

WW--7

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW--

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {____

cond broadcast (&okToRead);

release(&lock);

```

```

Simulation of Readers/Writers Solution

W1 gets signal (R3 still waiting)

AR = 0, WR = 1, AW = 1, WW = 0

Writer() {

acquire(&lock);

ile ((AW + AR) > 0) { // Is it safe to write?

WW++;

cond wait(&okToWrite,&lock);// Sleep on cond var

WW--;

// No longer waiting

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW--

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {_____

cond broadcast (&okToRead);

release(&lock);

```

```

Simulation of Readers/Writers Solution

W1 accessing dbase (R3 still waiting)

AR = 0, WR = 1, AW = 1, WW = 0

Writer() {

acquire(&lock);

ile ((AW + AR) > 0) { // Is it safe to write?

WW++;

cond wait(&okToWrite,&lock);// Sleep on cond var

WW--;

// No longer waiting

AW++;

release(&lock);

AccessDBase(ReadWrite)

acquire(&lock);

AW--

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {

cond broadcast (&okToRead);

release(&lock);

```

```

W1 finishes (R3 still waiting)

AR = 0, WR = 1, AW = 1, WW = 0

Writer() {

acquire(&lock);

ile ((AW + AR) > 0) { // Is it safe to write?

WW++;

cond wait(&okToWrite,&lock);// Sleep on cond var

WW--;

// No longer waiting

while ((AW + AR) > 0) {

WW++;

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {_____

cond broadcast (&okToRead);

```

}

release(&lock);

```

W1 finishes (R3 still waiting)

AR = 0, WR = 1, AW = 0, WW = 0

Writer() {

acquire(&lock);

ile ((AW + AR) > 0) { // Is it safe to write?

WW++;

cond wait(&okToWrite,&lock);// Sleep on cond var

WW--;

// No longer waiting

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock):

AW--

(WW >

cond signal(&okToWrite);

else_if (WR > 0) {____

cond broadcast (&okToRead) ;

release(&lock);

```

```

W1 finishes (R3 still waiting)

AR = 0, WR = 1, AW = 0, WW = 0

Writer() {

acquire(&lock);

ile ((AW + AR) > 0) { // Is it safe to write?

WW++;

cond wait(&okToWrite,&lock);// Sleep on cond var

WW--;

// No longer waiting

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW---

cond signal(&okToWrite);

else_if (WR > 0) {

cond broadcast (&okToRead) ;

release(&lock);

```

```

Simulation of Readers/Writers Solution

W1 signaling readers (R3 still waiting)

AR = 0, WR = 1, AW = 0, WW = 0

Writer() {

acquire(&lock);

ile ((AW + AR) > 0) { // Is it safe to write?

WW++;

cond wait(&okToWrite,&lock);// Sleep on cond var

WW--;

// No longer waiting

while ((AW + AR) > 0) {

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WW++;

WH+;

WH+

AW++;

release(&lock);

AccessDBase(ReadWrite);

acquire(&lock);

AW--

(\dot{W}W > 0)

cond signal(&okToWrite);

else_if (WR > 0) {

cond broadcast(&okToRead);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R3 gets signal (no waiting threads)

AR = 0, WR = 1, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

cond wait(&okToRead,&lock);// Sleep on cond var

// No longer waiting

WR--;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R3 gets signal (no waiting threads)

AR = 0, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

cond wait(&okToRead, &lock);// Sleep on cond var

WR--; // No longer waiting

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

Simulation of Readers/Writers Solution R3 accessing dbase (no waiting threads) AR = 1, WR = 0, AW = 0, WW = 0Reader() { acquire(&lock); while  $((AW + WW) > 0) \{ // \text{ Is it safe to read} \}$ // No. Writers exist WR++; cond wait(&okToRead,&lock);// Sleep on cond var WR--; // No longer waiting // Now we are active! AR++; release(&lock); AccessDBase(ReadOnly) acquire(&lock); AR--; if (AR == 0 && WW > 0)cond signal(&okToWrite); release(&lock);

```

R3 finishes (no waiting threads)

AR = 1, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDBase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

```

Simulation of Readers/Writers Solution

R3 finishes (no waiting threads)

AR = 0, WR = 0, AW = 0, WW = 0

Reader() {

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

// Now we are active!

AR++;

release(&lock);

AccessDbase(ReadOnly);

acquire(&lock);

AR--;

if (AR == 0 \&\& WW > 0)

cond signal(&okToWrite);

release(&lock);

```

## Questions

Can readers starve? Consider Reader() entry code:

# Questions

Further, what if we turn the signal() into broadcast()

```

AR--; // No longer active

cond_broadcast(&okToWrite); // Wake up sleepers

```

Finally, what if we use only one condition variable (call it "okContinue") instead of two separate ones?

-Both readers and writers sleep on this variable

-Must use broadcast() instead of signal()

#### Code for a Reader

```

Reader() {

// First check self into system

acquire(&lock);

while ((AW + WW) > 0) \{ // \text{ Is it safe to read} \}

// No. Writers exist

WR++;

cond wait(&okToRead,&lock);// Sleep on cond var

WR--;

// No longer waiting

}

AR++;

// Now we are active!

release(&lock);

// Perform actual read-only access

AccessDatabase(ReadOnly);

// Now, check out of system

acquire(&lock);

// No longer active

AR--;

if (AR == 0 && WW > 0) // No other active readers

cond signal(&okToWrite);// Wake up one writer

release(&lock);

```

### Code for a Writer

```

Writer() {

// First check self into system

acquire(&lock);

while ((AW + AR) > 0) { // Is it safe to write?

// No. Active users exist

WW++;

cond wait(&okToWrite,&lock); // Sleep on cond var

// No longer waiting

WW - - ;

// Now we are active!

AW++;

release(&lock);

// Perform actual read/write access

AccessDatabase(ReadWrite);

// Now, check out of system

acquire(&lock);

// No longer active

AW - -;

// Give priority to writers

if (WW > 0) {

cond signal(&okToWrite);// Wake up one writer

} else if (WR > 0) { // Otherwise, wake reader

cond broadcast(&okToRead); // Wake all readers

release(&lock);

```

# C-Language Support for Synchronization

C language: Pretty straightforward synchronization

```

Just make sure you know all the code paths out of a critical section

int Rtn() {

acquire(&lock);

if (exception) {

release(&lock);

return errReturnCode;

release(&lock);

return OK;

}

```

# Concurrency and Synchronization in C

Harder with more locks

```

void Rtn() {

lock1.acquire();

if (error) {

lock1.release();

return;

•••

lock2.acquire();

•••

if (error) {

lock2.release()

lock1.release();

return;

...

lock2.release();

lock1.release();

```

```

C++ Language Support for Synchronization

Languages with exceptions like C++

-Languages that support exceptions are problematic (easy to make a non-local exit

without releasing lock)

void Rtn() {

lock.acquire();

DoFoo();

lock.release();

void DoFoo() {

if (exception) throw errException;

...

}

-Notice that an exception in DoFoo() will exit without releasing the lock!

```

```

C++ Language Support for Synchronization (con't)

Must catch all exceptions in critical sections

-Catch exceptions, release lock, and re-

throw exception:

void Rtn() {

lock.acquire();

try {

DoFoo();

} catch (...) { // catch exception

lock.release(); // release lock

// re-throw the exception

throw;

lock.release();

void DoFoo() {

if (exception) throw errException;

Crooks CS162 © UCB Fall 2022

9.60

```

#### Much better: C++ Lock Guards

```

#include <mutex>

int global_i = 0;

std::mutex global_mutex;

```

```

void safe_increment() {

std::lock_guard<std::mutex> lock(global_mutex);

...

global_i++;

// Mutex released when 'lock' goes out of scope

}

```

Python with Keyword

More versatile than we show here (can be used to close files, database connections, etc.)

```

lock = threading.Lock()

...

with lock: # Automatically calls acquire()

some_var += 1

...

# release() called however we leave block

```

### Java synchronized Keyword

```

Every Java object has an associated lock:

-Lock is acquired on entry and released on exit from a

synchronized method

-Lock is properly released if exception occurs inside a

synchronized method

-Mutex execution of synchronized methods (beware deadlock)

```

```

class Account {

private int balance;

// object constructor

public Account (int initialBalance) {

balance = initialBalance;

}

public synchronized int getBalance() {

return balance;

}

public synchronized void deposit(int amount) {

balance += amount;

}

}

```

# Java Support for Monitors

Along with a lock, every object has a single condition variable associated with it

- To wait inside a synchronized method:

- -void wait();

- -void wait(long timeout);

- To signal while in a synchronized method: -void notify(); -void notify():

- -void notifyAll();

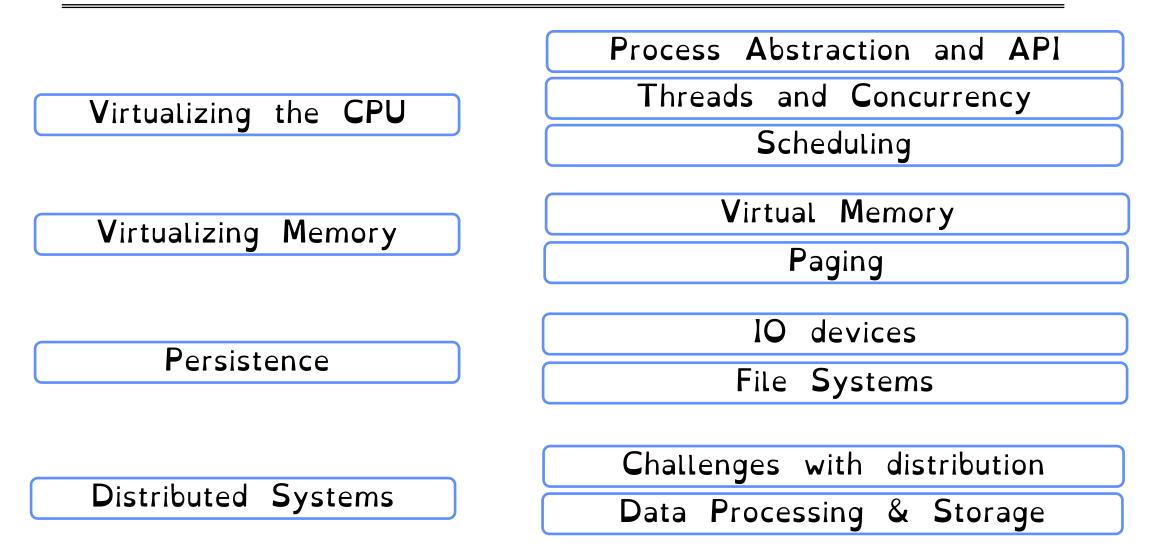

# Where are we going with synchronization?

| Programs                | Shared Programs                                  |

|-------------------------|--------------------------------------------------|

| Higher-<br>level<br>API | Locks Semaphores Monitors Send/Receive           |

| Hardware                | Load/Store Disable Ints Test&Set<br>Compare&Swap |

# Implement various higher-level synchronization primitives using atomic operations

### Topic Breakdown

• What is scheduling?

• What makes a good scheduling policy?

What are existing schedulers and how do they perform?

# The Scheduling Loop!

```

if (readyThreads(TCBs) ) {

nextTCB = selectThread(TCBs);

run(nextTCB);

} else {

run_idle_thread();

}

```

1. Which task to run next?

2. How frequently does this loop run?

3. What happens if run never returns?

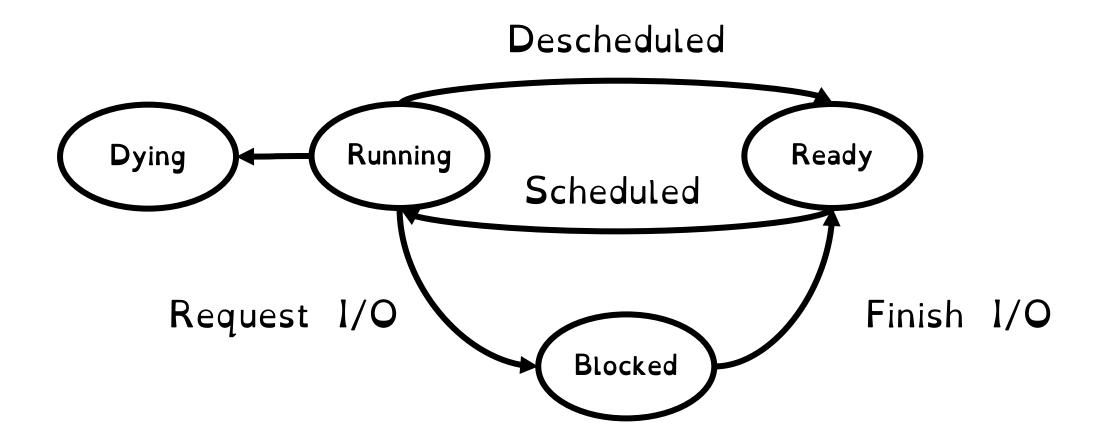

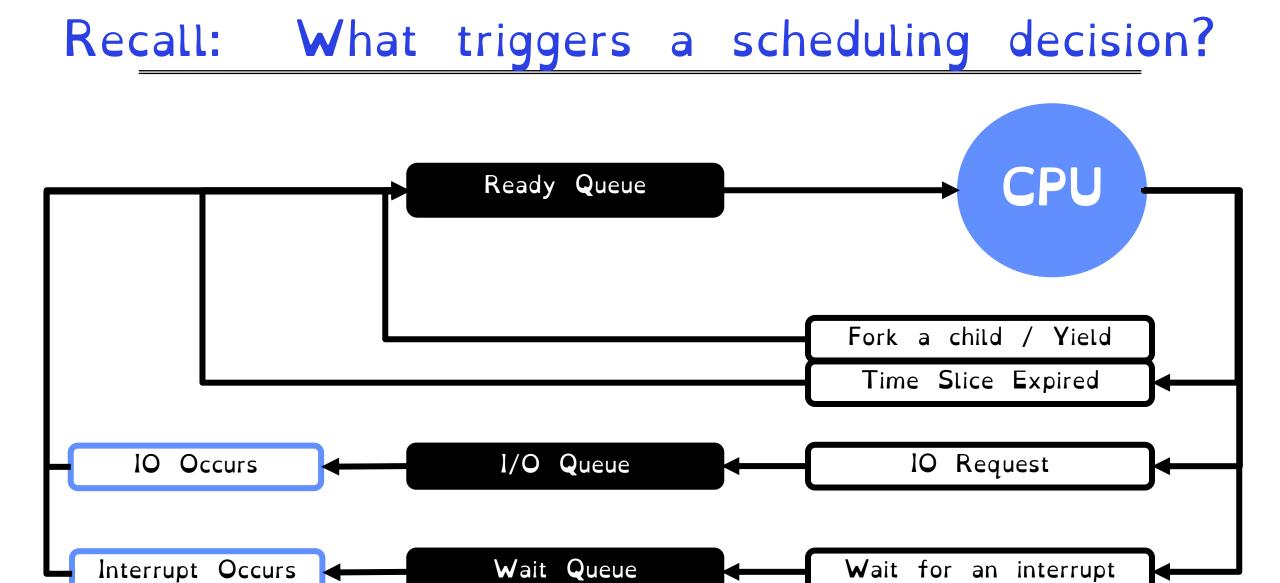

### Recall: Thread Life Cycle

# What makes a good scheduling policy?

#### A hopeless Queue.

The Queue For the UK Queen

6 miles (10 KM) long.

Visible from Space.

A bad but more realistic queue.

The DMV

# What makes a good scheduling policy?

# What does the DMV care about?

# What do individual users care about?

## Important Performance Metrics

Response time (or latency). User-perceived time to do some task

Throughput. The rate at which tasks are completed

Scheduling overhead.

The time to switch from one task to another.

Predictability.

Variance in response times for repeated requests.

## Important Performance Metrics

#### Fairness

#### Equality in the performance perceived by one task

#### **S**tarvation

# The lack of progress for one task, due to resources being allocated to different tasks

## Sample Scheduling Policies

Assume DMV job A takes 1 second, job B takes 2 days Policy Idea: Only ever schedule users with Job A

What is the metric we are optimizing? A) Throughput B) Latency C) Predictability D) Low-Overhead

> Can the schedule lead to starvation? A) Yes B) No

> > Is the schedule fair? A) Yes B) No

## Sample Scheduling Policies

Assume DMV consists only of jobs of type A. Policy Idea: Schedule jobs randomly

What is the metric we are optimizing? A) Throughput B) Latency C) Predictability D) Low-Overhead

> Can the schedule lead to starvation? A) Yes B) No

> > Is the schedule fair? A) Yes B) No

## Sample Scheduling Policies

Assume DMV consists only of 100 different types of jobs. Some jobs need Clerk A, some Clerks A&B, others Clerk C. Policy Idea Every time schedule a job, compute all possible orderings of jobs, pick one that finishes quickest

What is the metric we are optimizing? A) Throughput B) Latency C) Predictability D) Low-Overhead

> Can the schedule lead to starvation? A) Yes B) No

> > Is the schedule fair? A) Yes B) No

## Scheduling Policy Goals/Criteria

Minimise Response Time

#### Maximise Throughput

While remaining fair and starvation-free

### Useful metrics

Waiting time for P Total Time spent waiting for CPU Average waiting time Average of all processes' wait time Response Time for P Time to when process gets first scheduled Completion time Waiting time + Run time Average completion time Average of all processes' completion time

Crooks CS162 © UCB Fall 2022

## Assumptions

Threads are independent!

One thread = One User

# Unrealistic but simplify the problem so it can be solved

#### Only look at work-conserving scheduler => Never leave processor idle if work to do

Workload Assumptions

A workload is a set of tasks for some system to perform, including how long tasks last and when they arrive

**Compute-Bound**

Tasks that primarily perform compute

Fully utilise CPU

#### IO Bound

Mostly wait for IO, limited compute

Often in the Blocked state

## First-Come, First-Served (FCFS)

Run tasks in order of arrival.

Run task until completion (or blocks on IO). No preemption

This is the DMV model.

Also called FIFO

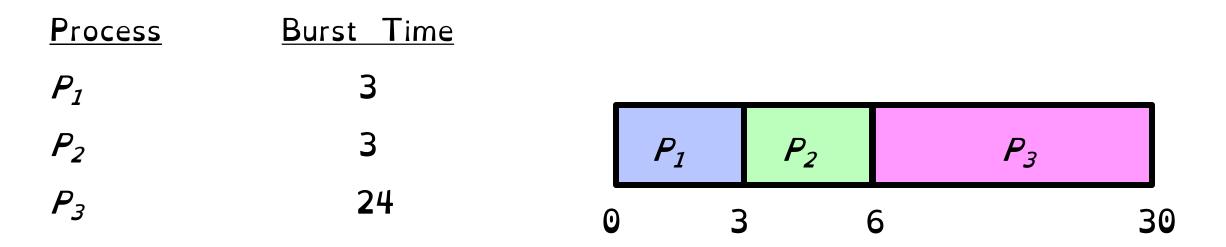

## First-Come, First-Served (FCFS)

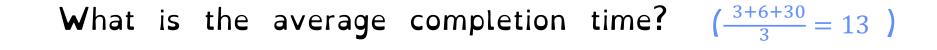

What is the average waiting time?  $\left(\frac{0+3+6}{3}=3\right)$

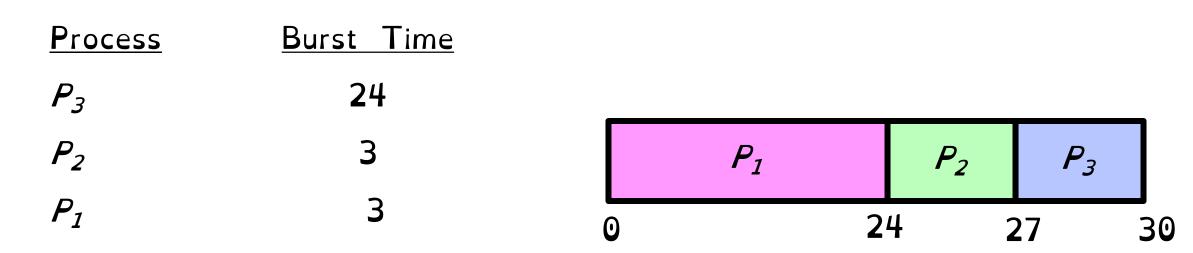

## First-Come, First-Served (FCFS)

What is the average waiting time?  $\left(\frac{0+24+27}{3}=17\right)$

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

#### FIFO/FCFS very sensitive to arrival order

#### Convoy effect

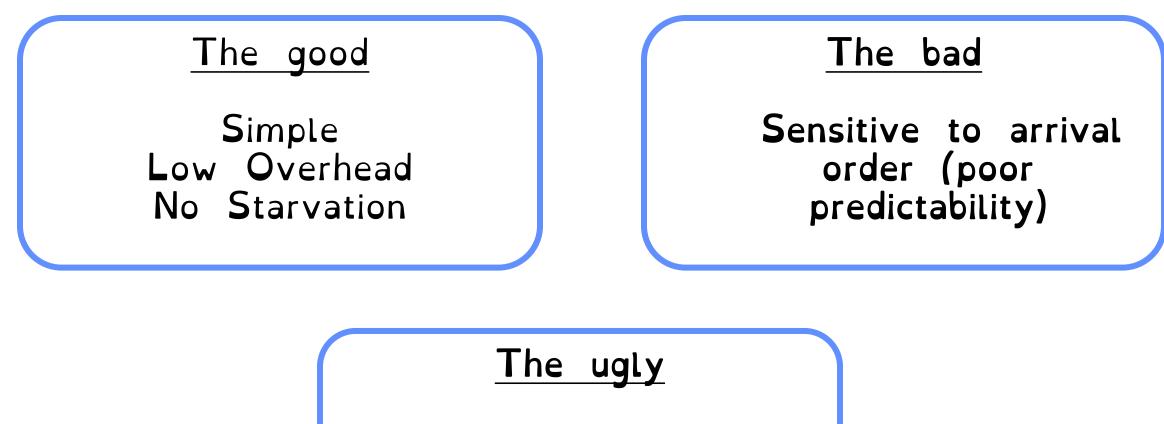

## FCFS/FIFO Summary

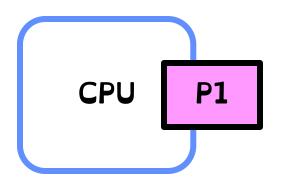

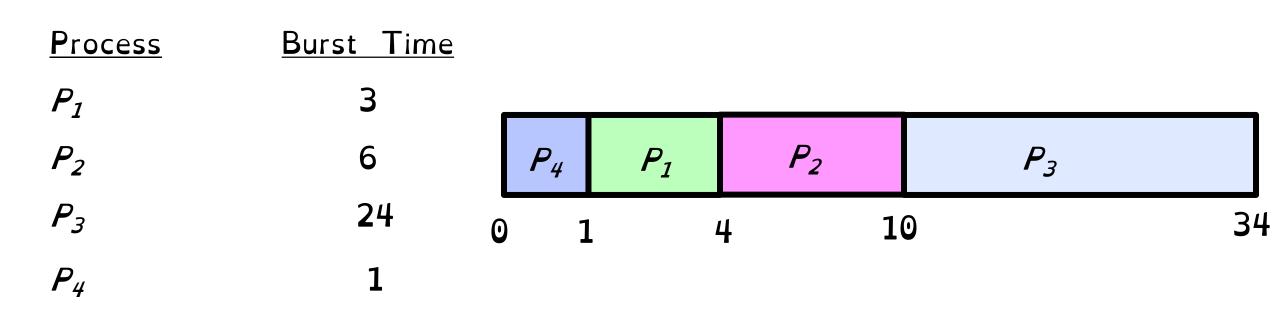

## Shortest Job First

How can we minimise average completion time?

#### By scheduling jobs in order of estimated completion time

#### This is the "10 items or less" line at Safeway

## Shortest Job First

What is the average completion time?  $\left(\frac{1+4+10+34}{4} = 12.25\right)$

# Can prove that SJF generates optimal average completion time if all jobs arrive at the same time

Crooks CS162 © UCB Fall 2022

#### Can SJF lead to starvation?

Yes

#### Any scheduling policy that always favours a fixed property for scheduling leads to starvation

#### Can SJF lead to starvation?

#### Yes

#### Any scheduling policy that always favours a fixed property for scheduling leads to starvation

#### Can SJF lead to starvation?

#### Yes

#### Any scheduling policy that always favours a fixed property for scheduling leads to starvation

#### Is SFJ subject to the convoy effect?

Yes

# Any non-preemptible scheduling policy suffers from convoy effect

#### Is SFJ subject to the convoy effect?

Yes

# Any non-preemptible scheduling policy suffers from convoy effect

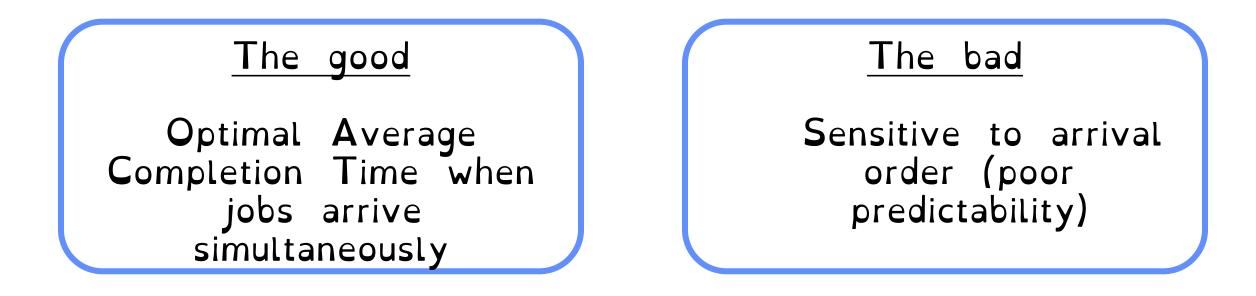

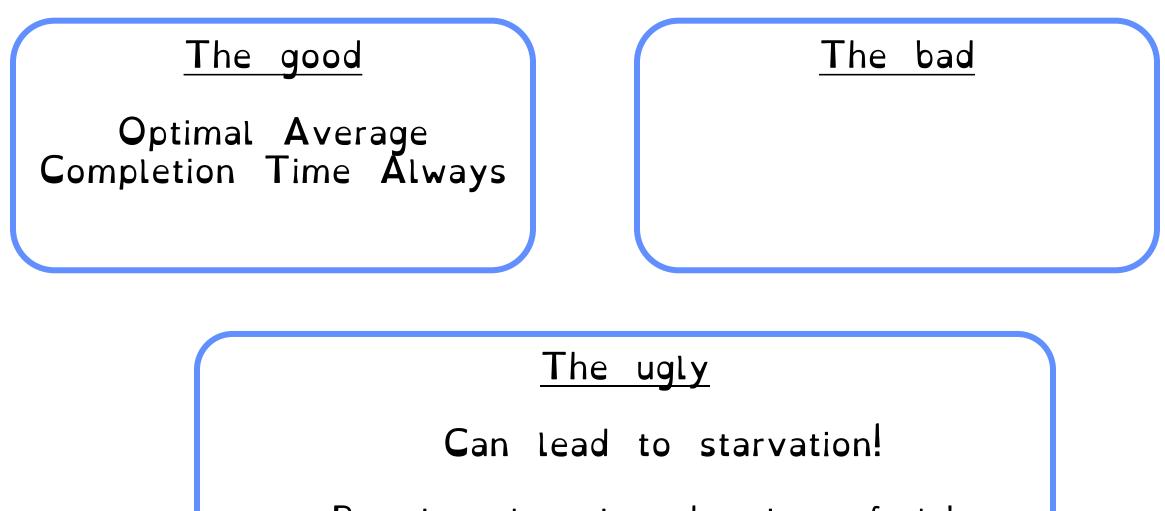

SJF Summary

Crooks CS162 © UCB Fall 2022

#### Introduce the notion of preemption

#### A running task can be de-scheduled before completion.

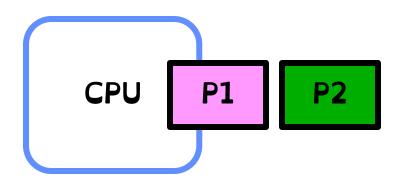

#### STCF

#### Schedule the task with the least amount of time left

Schedule the task with the least amount of time left

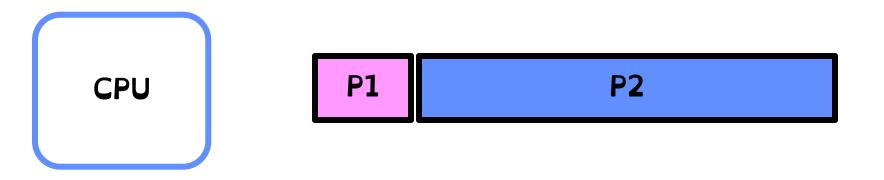

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| $P_1$                 | 3                        | 10                  |

| $P_2$                 | 6                        | 1                   |

| <b>P</b> <sub>3</sub> | 24                       | 0                   |

| $P_4$                 | 16                       | 20                  |

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| $P_{1}$               | 3                        | 10                  |

| $P_2$                 | 6                        | 1                   |

| <b>P</b> <sub>3</sub> | 24                       | 0                   |

| $P_4$                 | 16                       | 18                  |

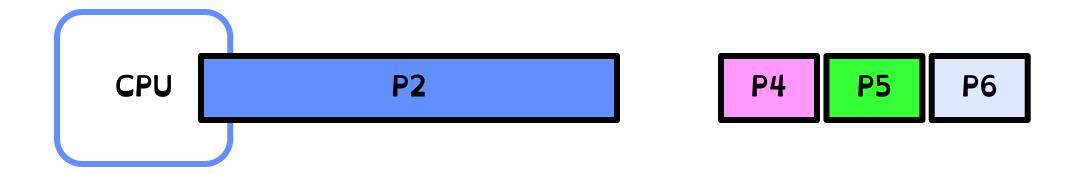

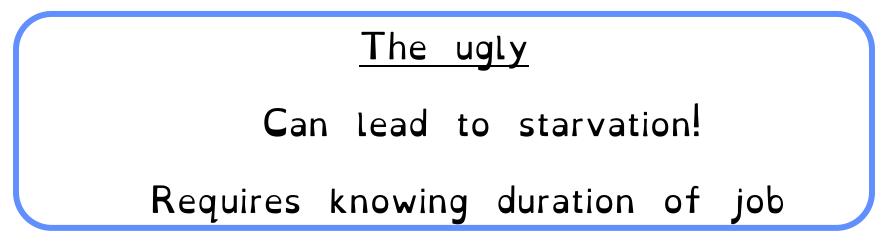

**P3** 0 1

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| $P_{I}$               | 3                        | 10                  |

| <i>P</i> <sub>2</sub> | 6                        | 1                   |

| <i>P</i> <sub>3</sub> | 23                       | 0                   |

| $P_4$                 | 16                       | 18                  |

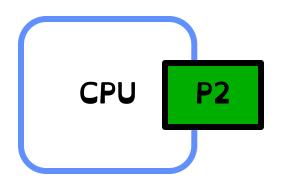

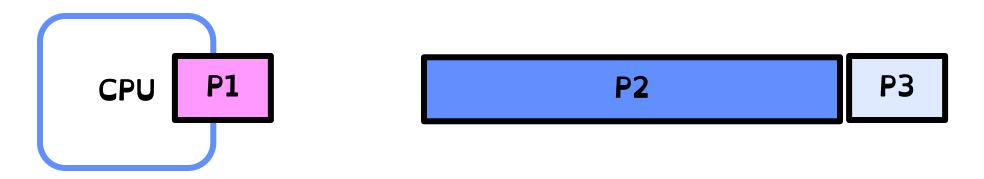

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| $P_1$                 | 3                        | 10                  |

| $P_2$                 | 0                        | 1                   |

| <b>P</b> <sub>3</sub> | 23                       | Ø                   |

| $P_4$                 | 16                       | 20                  |

|   | Р3  | P2 | Р3 |    |

|---|-----|----|----|----|

| C | ) ] |    | 7  | 10 |

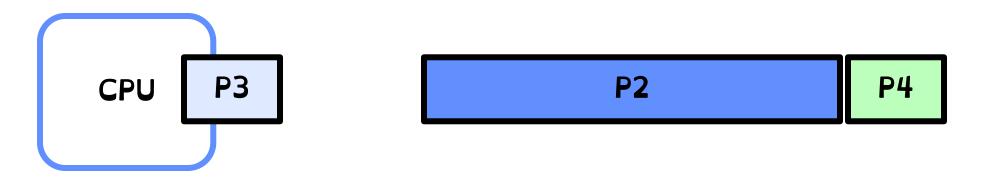

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| <i>P</i> <sub>1</sub> | 3                        | 10                  |

| $P_2$                 | 0                        | 1                   |

| <b>P</b> <sub>3</sub> | 20                       | 0                   |

| $P_4$                 | 16                       | 18                  |

|   | P3 | P2 |   | Р3 | P1 |    |

|---|----|----|---|----|----|----|

| 0 | -  | L  | 7 | 10 | 0  | 13 |

## Shortest Time to Completion First (STCF)

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| $P_1$                 | 0                        | 10                  |

| $P_2$                 | 0                        | 1                   |

| <b>P</b> <sub>3</sub> | 15                       | 0                   |

| <b>P</b> <sub>4</sub> | 16                       | 18                  |

|   | P3 | P2 |   | Р3 | P1 |    | Р3 |         |

|---|----|----|---|----|----|----|----|---------|

| C | )  | 1  | 7 | 10 |    | 13 | 1  | _<br>L8 |

## Shortest Time to Completion First (STCF)

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| $P_1$                 | 0                        | 10                  |

| $P_2$                 | 0                        | 1                   |

| <b>P</b> <sub>3</sub> | 0                        | Ø                   |

| $P_4$                 | 15                       | 18                  |

|   | P3 |   | P2 | Р3 | P1 |    | P3 |    |

|---|----|---|----|----|----|----|----|----|

| C |    | 1 | 7  | 7  | 10 | 13 | 3  | 33 |

## Shortest Time to Completion First (STCF)

| <u>Process</u>        | <u>Burst Time (left)</u> | <u>Arrival Time</u> |

|-----------------------|--------------------------|---------------------|

| $P_1$                 | 0                        | 10                  |

| $P_2$                 | 0                        | 1                   |

| <b>P</b> <sub>3</sub> | 0                        | 0                   |

| $P_4$                 | 15                       | 18                  |

|   | Р3 | P2  | Р3  | P1 | F  | 93 | P4 |

|---|----|-----|-----|----|----|----|----|

| C |    | 1 7 | 7 1 | 0  | 13 | 3  | 2  |

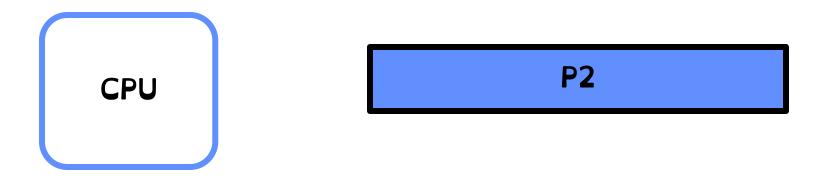

## Are we done?

#### Can STCF lead to starvation?

#### Yes

#### Any scheduling policy that always favours a fixed property for scheduling leads starvation

#### No change!

## Are we done?

## Is STCF subject to the convoy effect? No!

#### STCF is a preemptible policy

## STCF Summary

## Taking a step back

| Property                                  | FCFS | SJF          | STCF |

|-------------------------------------------|------|--------------|------|

| Optimise<br>Average<br>Completion<br>Time |      | $\checkmark$ |      |

| Prevent<br>Starvation                     |      |              |      |

| Prevent<br>Convoy<br>Effect               |      |              |      |

| Psychic Skills<br>Not Needed              |      |              |      |

Can we design a non-psychic, starvation-free scheduler with good response time?

Crooks CS162 © UCB Fall 2022

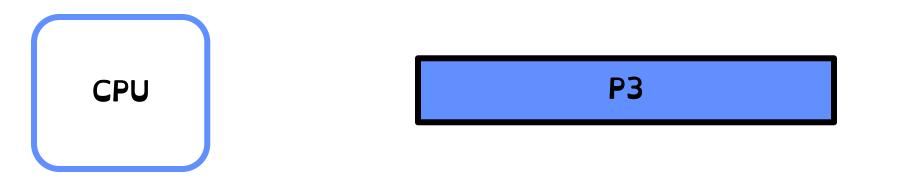

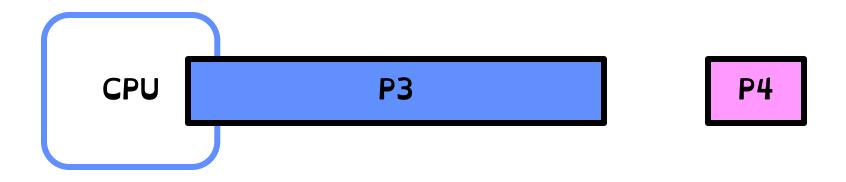

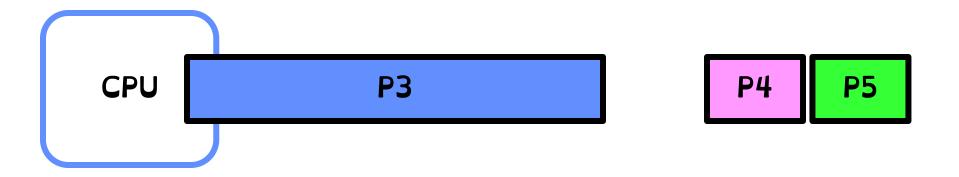

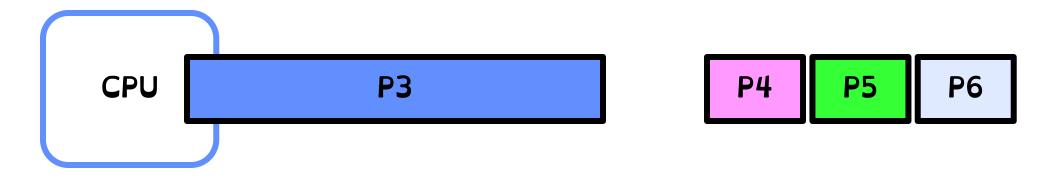

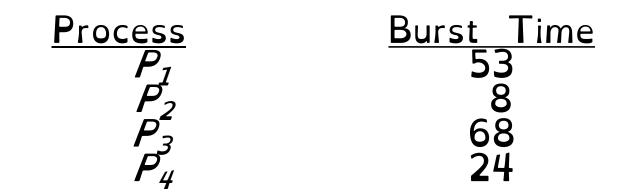

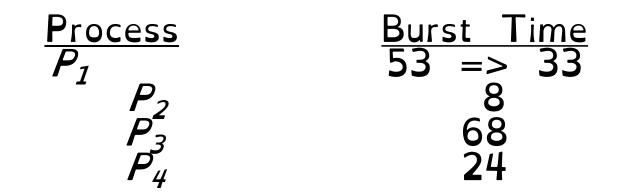

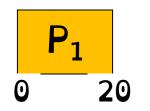

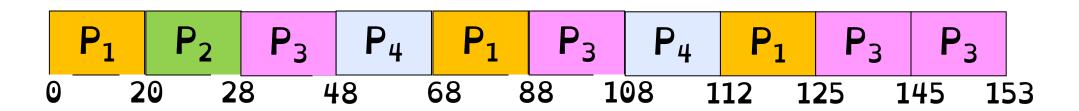

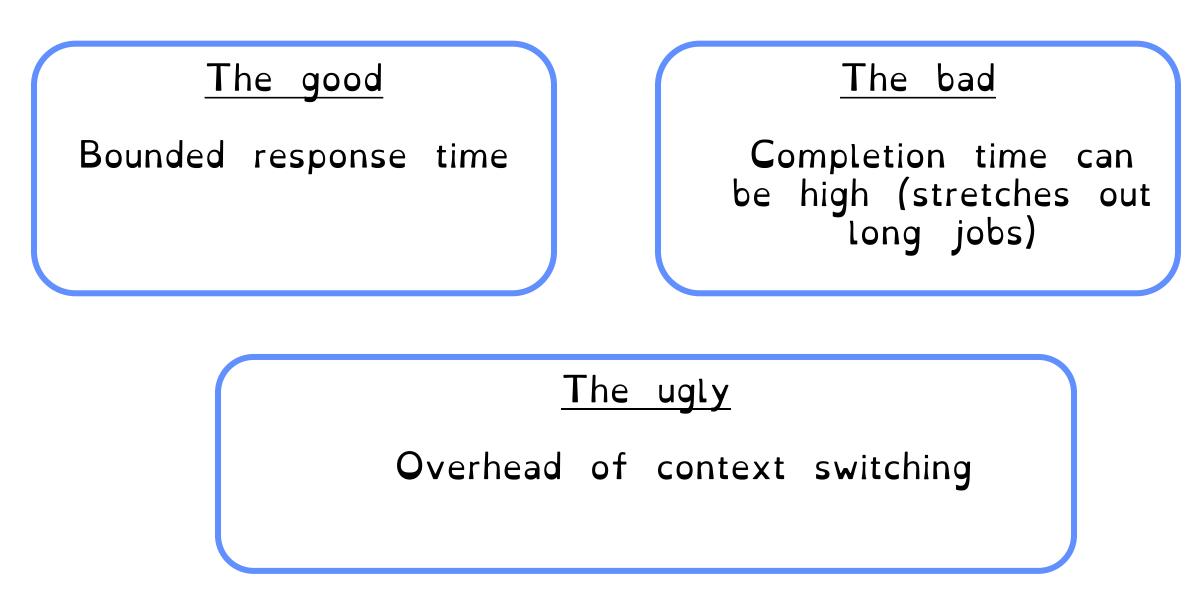

## Round-Robin Scheduling

#### RR runs a job for a time slice (a scheduling quantum)

Once time slice over, Switch to next job in ready queue. => Called time-slicing

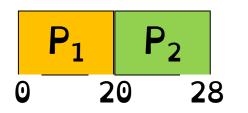

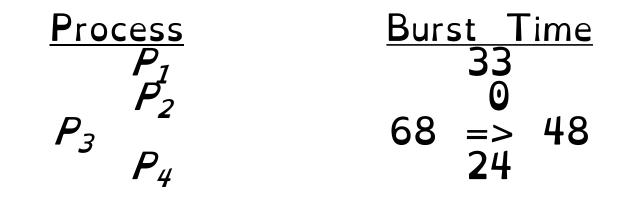

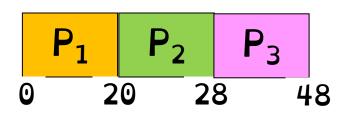

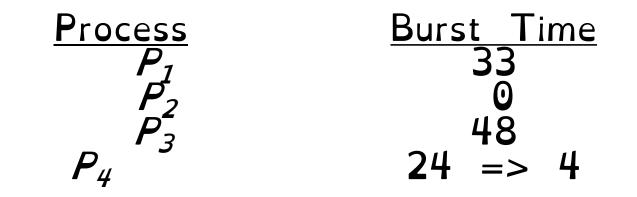

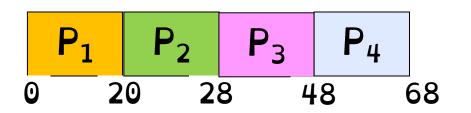

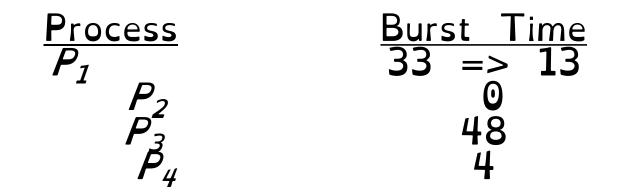

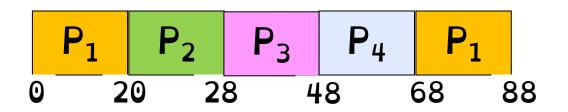

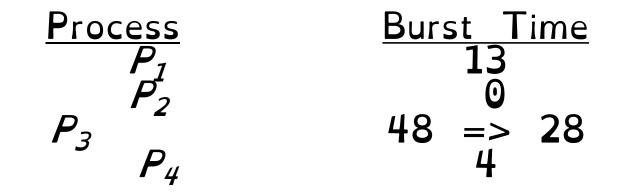

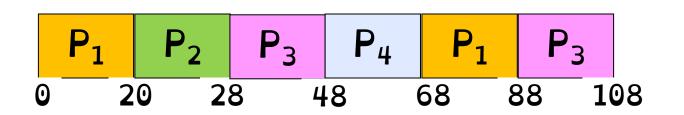

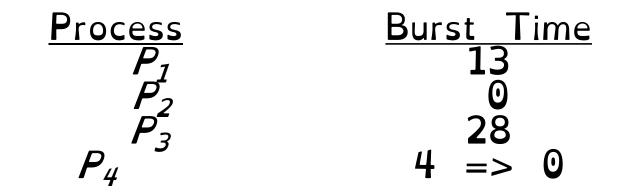

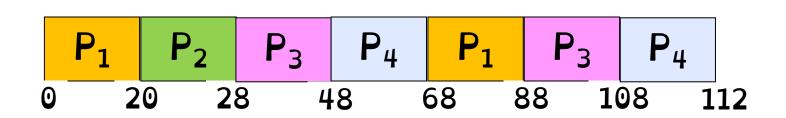

**Process** Burst Time 338 => 0 68 24  $\begin{array}{c} P_2 \\ P_2 \\ P_3 \\ P_4 \end{array}$

Average completion time

$\left(\frac{125+28+153+112}{4}=104.25\right)$

## Decrease Completion Time

- $T_1$ : Burst Length 10  $T_3$ : Burst Length 10

- T<sub>2</sub>: Burst Length 5

$$Q = 10$$

$T_1$   $T_2$   $T_3$

0  $10$   $15$   $25$

Average Completion Time =  $(10 + 15 + 25)/3 = 16.7$

Q = 5  $T_{1} T_{2} T_{3} T_{1} T_{3}$  0 5 10 15 20 25Average Completion Time = (20 + 10 + 25)/3 = 18.3

## Switching is not free!

#### Small scheduling quantas lead to frequent context switches - Mode switch overhead

- Mode switch overnead

- Trash cache-state

# q must be large with respect to context switch, otherwise overhead is too high

## Are we done?

#### Can RR lead to starvation?

#### No

#### No process waits more than (n-1)q time units

## Are we done?

#### Can RR suffer from convoy effect?

#### No

#### Only run a time-slice at a time

Crooks CS162 © UCB Fall 2022

**RR** Summary

## Taking a step back

| Property                                  | FCFS | SJF          | STCF         |

|-------------------------------------------|------|--------------|--------------|

| Optimise<br>Average<br>Completion<br>Time |      | $\checkmark$ | $\checkmark$ |

| Prevent<br>Starvation                     |      |              |              |

| Prevent<br>Convoy<br>Effect               |      |              | $\checkmark$ |

| Psychic Skills<br>Not Needed              |      |              |              |

## Taking a step back

| Property                                  | FCFS         | SJF          | STCF | RR           |

|-------------------------------------------|--------------|--------------|------|--------------|

| Optimise<br>Average<br>Completion<br>Time |              | $\checkmark$ |      |              |

| Optimise<br>Average<br>Response<br>Time   |              |              |      | $\checkmark$ |

| Prevent<br>Starvation                     | $\checkmark$ |              |      |              |

| Prevent<br>Convoy<br>Effect               |              |              |      | $\checkmark$ |

| Psychic<br>Skills Not<br>Needed           | $\checkmark$ |              |      | $\checkmark$ |

## FCFS and Round Robin Showdown

# Assuming zero-cost context-switching time, is RR always better than FCFS?

10 jobs, each take 100s of CPU time RR scheduler quantum of 1s All jobs start at the same time

| Job # | FIFO | RR   |

|-------|------|------|

| 1     | 100  | 991  |

| 2     | 200  | 992  |

|       | •••  |      |

| 9     | 900  | 999  |

| 10    | 1000 | 1000 |

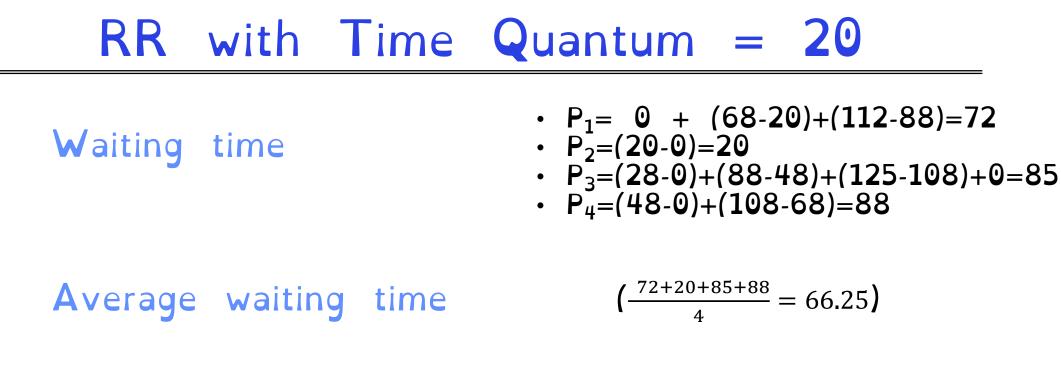

## Earlier Example with Different Time Quantum

Best

| Quantum       | P1  | P2  | P3  | P4  | Average |

|---------------|-----|-----|-----|-----|---------|

| Best FCFS     | 85  | 8   | 16  | 32  | 69.5    |

| Q=1           | 137 | 30  | 153 | 81  | 100.5   |

| Q=5           | 135 | 28  | 153 | 82  | 99.5    |

| Q=8           | 133 | 16  | 153 | 80  | 99,5    |

| Q=10          | 135 | 18  | 153 | 92  | 104.5   |

| Q=20          | 125 | 28  | 153 | 112 | 104.5   |

| Worst<br>FCFS | 121 | 153 | 68  | 145 | 121.75  |