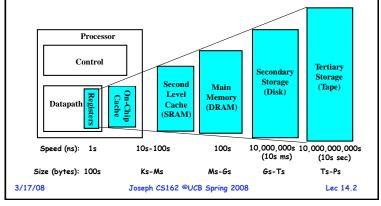

## **Review: Memory Hierarchy of a Modern Computer System**

- Take advantage of the principle of locality to:

- Present as much memory as in the cheapest technology

- Provide access at speed offered by the fastest technology

| Review: What is in a PTE?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>Review: Other Caching Questions</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>What is in a Page Table Entry (or PTE)? <ul> <li>Pointer to next-level page table or to actual page</li> <li>Permission bits: valid, read-only, read-write, write-only</li> </ul> </li> <li>Example: Intel x86 architecture PTE: <ul> <li>Address same format previous slide (10, 10, 12-bit offset)</li> <li>Intermediate page tables called "Directories"</li> </ul> </li> <li>Page Frame Number <ul> <li>Present (same as "valid" bit in other architectures)</li> <li>W: Writeable</li> <li>U: User accessible</li> <li>PWT: Page write transparent: external cache write-through PCD: Page cache disabled (page cannot be cached)</li> <li>Accessed: page has been accessed recently</li> <li>D: Dirty (PTE only): page has been modified recently</li> <li>L: L=1⇒4MB page (directory only).</li> </ul> </li> </ul> | <ul> <li>What line gets replaced on cache miss?</li> <li>Easy for Direct Mapped: Only one possibility</li> <li>Set Associative or Fully Associative: <ul> <li>Random</li> <li>LRU (Least Recently Used)</li> </ul> </li> <li>What happens on a write? <ul> <li>Write through: The information is written to both the cache and to the block in the lower-level memory</li> <li>Write back: The information is written only to the block in the cache</li> <li>Modified cache block is written to main memory only when it is replaced</li> <li>Question is block clean or dirty?</li> </ul> </li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Page 1

В

## Summary

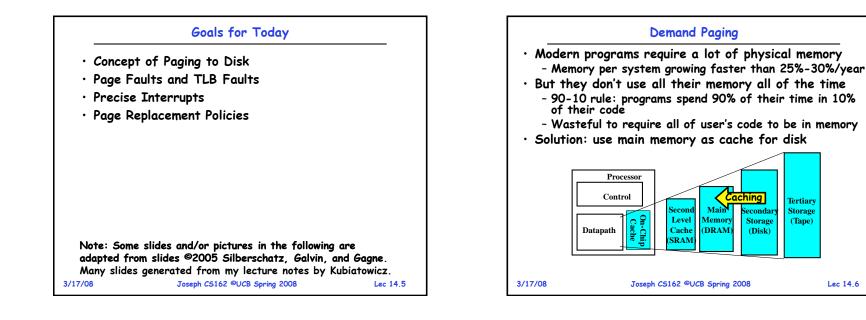

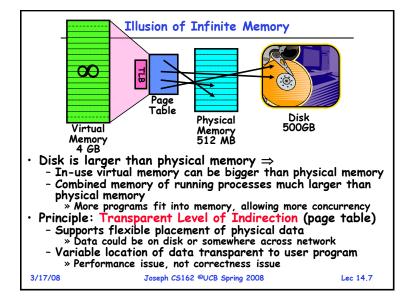

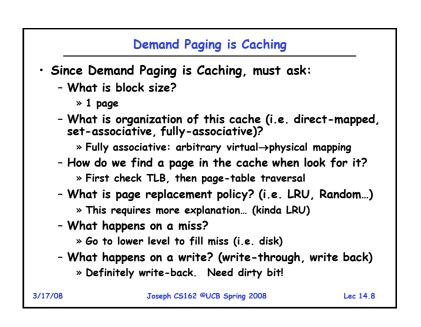

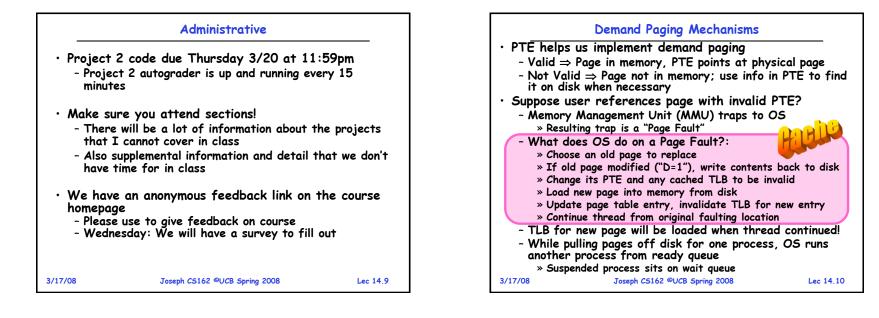

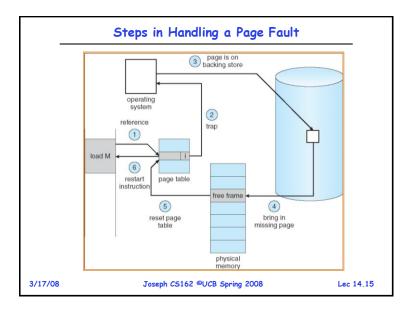

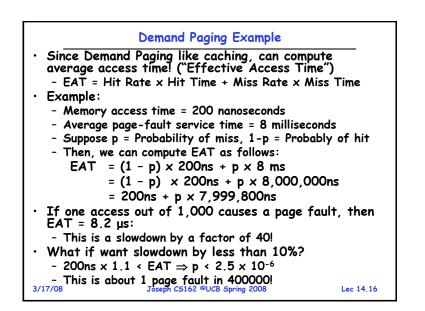

- **Demand Paging:**

- Treat memory as cache on disk

- Cache miss  $\Rightarrow$  get page from disk

- Transparent Level of Indirection

- User program is unaware of activities of OS behind scenes

- Data can be moved without affecting application correctness

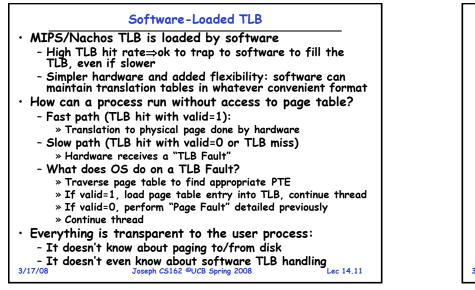

- Software-loaded TLB

- Fast Path: handled in hardware (TLB hit with valid=1)

- Slow Path: Trap to software to scan page table

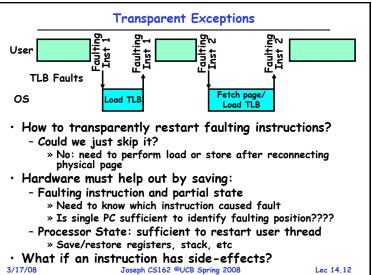

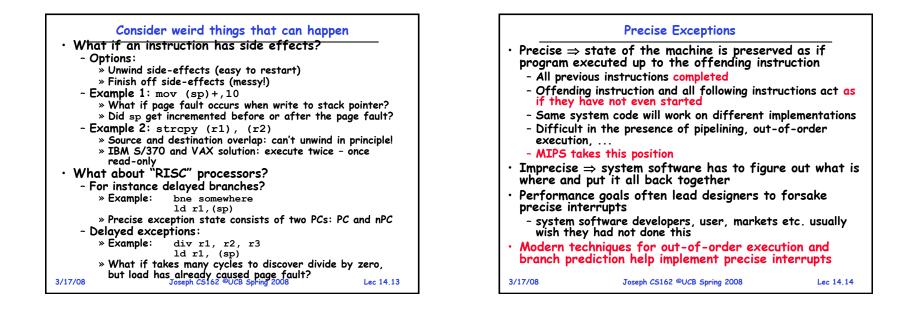

- Precise Exception specifies a single instruction for which: - All previous instructions have completed (committed state)

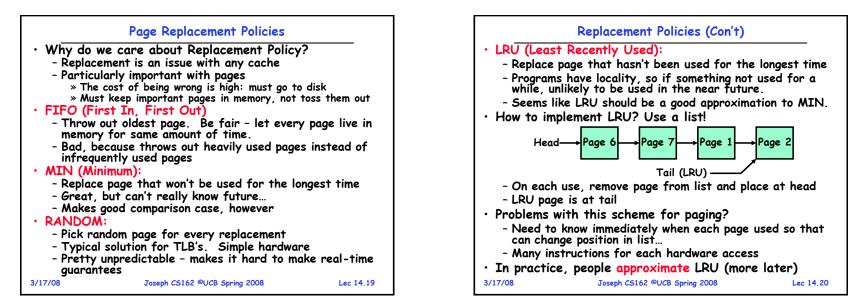

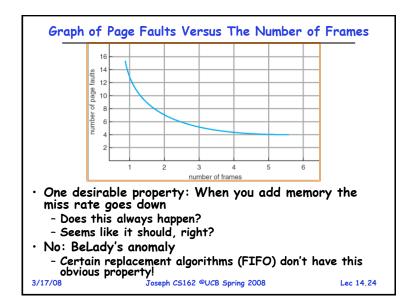

- No following instructions nor actual instruction have started Replacement policies

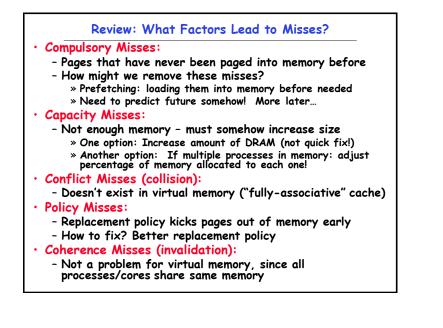

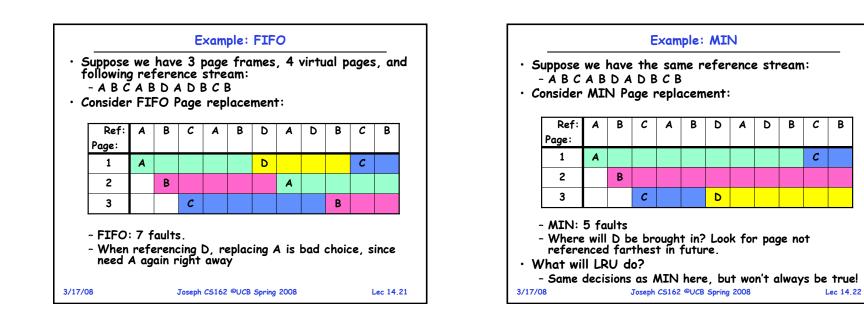

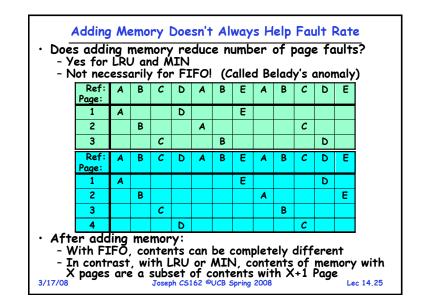

- FIFO: Place pages on queue, replace page at end - MIN: replace page that will be used farthest in future

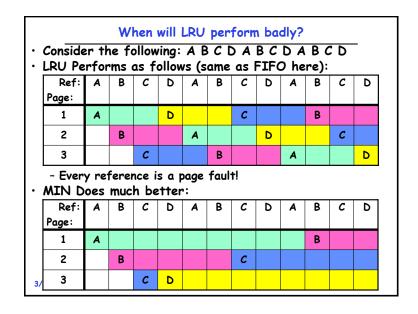

- LRU: Replace page that hasn't be used for the longest time

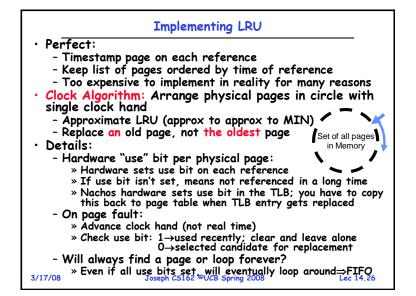

- Clock Algorithm: Approximation to LRU

3/17/08

Joseph CS162 ©UCB Spring 2008

Lec 14.27