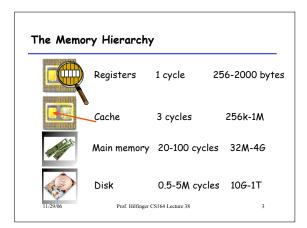

- Programs are written as if there are only two kinds of memory: main memory and disk

- Programmer is responsible for moving data from disk to memory (e.g., file I/O)

- Hardware is responsible for moving data between memory and caches

- Compiler is responsible for moving data between memory and registers

Prof. Hilfinger CS164 Lecture 38

11/29/06

## Current Trends

- Cache and register sizes are growing slowly

- Processor speed improves faster than memory speed and disk speed

- The cost of a cache miss is growing

- The widening gap is bridged with more caches

- It is very important to:

- Manage registers properly

- Manage caches properly

- Compilers are good at managing registers

Prof. Hilfinger CS164 Lecture 38

11/29/06

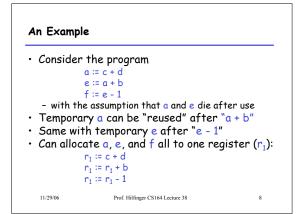

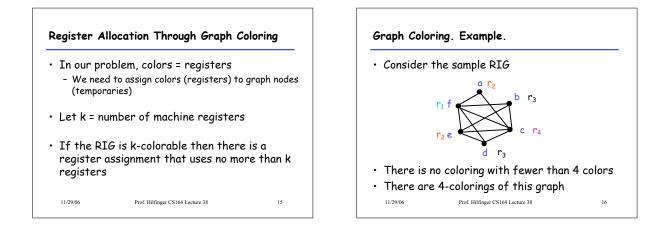

## The Register Allocation Problem Intermediate code uses as many temporaries as necessary This complicates final translation to assembly But simplifies code generation and optimization Typical intermediate code uses too many temporaries The register allocation problem: Rewrite the intermediate code to use fewer temporaries than there are machine registers

Method: assign more temporaries to a register

But without changing the program behavior

11/29/06 Prof. Hilfinger CS164 Lecture 38

## History

- Register allocation is as old as intermediate code

- · Register allocation was used in the original FORTRAN compiler in the '50s - Very crude algorithms

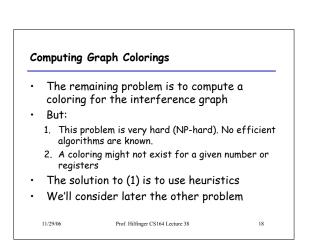

- A breakthrough was not achieved until 1980 when Chaitin invented a register allocation scheme based on graph coloring

- Relatively simple, global and works well in practice

10

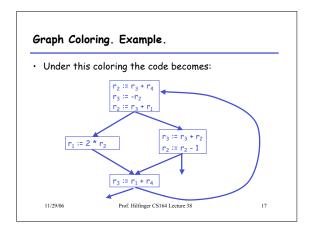

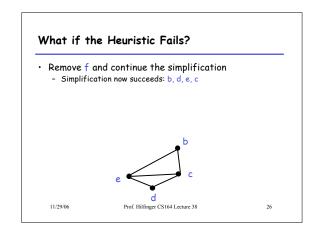

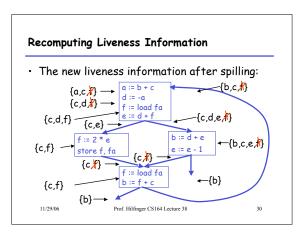

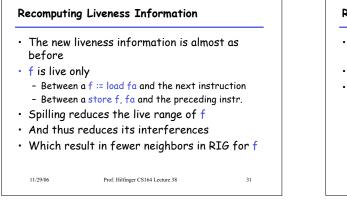

- edges of the spilled node • In our case f still interferes only with c and d

- And the resulting RIG is 3-colorable

## Conclusions

11/29/06

- Register allocation is a "must have" optimization in most compilers:

- Because intermediate code uses too many temporaries

- Because it makes a big difference in performance

- Graph coloring is a powerful register allocation scheme

- Register allocation is more complicated for CISC machines

Prof. Hilfinger CS164 Lecture 38 37