| inst.eecs.berkeley.edu/~c<br>UC Berkeley CS61C : Machine                                                                                    |              |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Lecture 25 –<br>Representations of Combinational Log                                                                                        | gic Circuits |

|                                                                                                                                             |              |

| Senior Lecturer SOE Dan                                                                                                                     |              |

| Conway's Life Logic Gates ⇒<br>Berlekamp, Conway and                                                                                        |              |

| Guy in their "Winning Ways" series<br>showed how a glider was a 1, no                                                                       |              |

| glider a 0, & how to build logic gates!<br>en.wikipedia.org/wiki/Conway%27s_(<br>csticL25 Representations of Combinational Load Circuit (1) | Game_of_Life |

| TT Example #1: 1                                 | iff or       | ne (not both) a,b=1        |

|--------------------------------------------------|--------------|----------------------------|

| а                                                | b            | У                          |

| 0                                                | 0            | 0                          |

| 0                                                | 1            | 1                          |

| 1                                                | 0            | 1                          |

| 1                                                | 1            | 0                          |

| CS81C L25 Representations of Combinational Logic | Circuits (4) | '<br>Garcia, Fall 2014 ⊕ U |

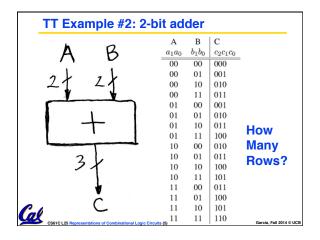

|   | TT Example #3: 32-bit unsigned adder |                                |                         |  |

|---|--------------------------------------|--------------------------------|-------------------------|--|

|   | A B                                  |                                | C                       |  |

| - | 000 0                                | 000 0                          | 000 00                  |  |

|   | 000 0                                | 000 1                          | 000 01                  |  |

|   | •                                    | •                              | • How                   |  |

|   | •                                    | •                              | . Many<br>Bows?         |  |

|   | •                                    | •                              | •                       |  |

|   | 111 1                                | 111 1                          | 111 10                  |  |

| G | CS61C L25 Representations of Com     | ibinational Logic Circuits (6) | Garcia, Fall 2014 © UCB |  |

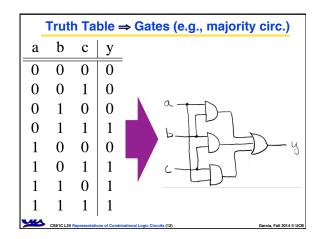

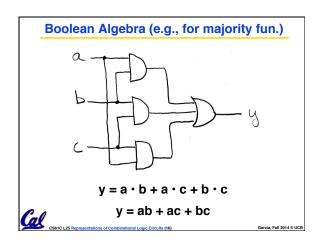

| TT Example                      | #4:           | 3-in          | put | majorit | y circuit           | _   |

|---------------------------------|---------------|---------------|-----|---------|---------------------|-----|

|                                 | а             | b             | c   | У       |                     |     |

|                                 | 0             | 0             | 0   | 0       |                     |     |

|                                 | 0             | 0             | 1   | 0       |                     |     |

|                                 | 0             | 1             | 0   | 0       |                     |     |

|                                 | 0             | 1             | 1   | 1       |                     |     |

|                                 | 1             | 0             | 0   | 0       |                     |     |

|                                 | 1             | 0             | 1   | 1       |                     |     |

|                                 | 1             | 1             | 0   | 1       |                     |     |

| Ca                              | 1             | 1             | 1   | 1       |                     |     |

| CS61C L25 Representations of Co | mbinational L | ogic Circuits | (7) |         | Garcia, Fall 2014 © | UCB |

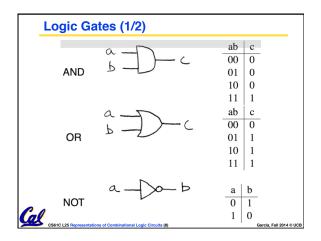

| 2-input gates extend to                                                        | o n-i | nput | ts |                 |

|--------------------------------------------------------------------------------|-------|------|----|-----------------|

| N-input XOR is the                                                             | а     | b    | с  | У               |

| <ul> <li>N-input XOR is the<br/>only one which isn't<br/>so obvious</li> </ul> | 0     | 0    | 0  | 0               |

| <ul> <li>It's simple: XOR is a<br/>1 iff the # of 1s at its</li> </ul>         | 0     | 0    | 1  | 1               |

| 1 iff the # of 1s at its<br>input is odd ⇒                                     | 0     | 1    | 0  | 1               |

|                                                                                | 0     | 1    | 1  | 0               |

|                                                                                | 1     | 0    | 0  | 1               |

|                                                                                | 1     | 0    | 1  | 0               |

|                                                                                | 1     | 1    | 0  | 0               |

| 0                                                                              | 1     | 1    | 1  | 1               |

| CS61C L25 Representations of Combinational Logic Circuits (11)                 |       |      |    | Garcia, Fall 20 |

| Administrivia                                                  |                         |

|----------------------------------------------------------------|-------------------------|

| <ul> <li>How many hours on project</li> </ul>                  | 2 so far?               |

| a) 0-10                                                        |                         |

| b) 10-20                                                       |                         |

| c) 30-40                                                       |                         |

| d) 50-60                                                       |                         |

| e) 60-70                                                       |                         |

|                                                                |                         |

|                                                                |                         |

|                                                                |                         |

| CA                                                             |                         |

| CS61C L25 Representations of Combinational Logic Circuits (14) | Garcia, Fall 2014 © UCB |

| Laws of Bo                                                                 | oolean Algebra                                                      |                                                                |

|----------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|

| $\begin{aligned} x \cdot \overline{x} &= 0\\ x \cdot 0 &= 0 \end{aligned}$ | $\begin{aligned} x + \overline{x} &= 1\\ x + 1 &= 1 \end{aligned}$  | complementarity<br>laws of 0's and 1's                         |

| $x \cdot 1 = x$ $x \cdot x = x$ $x \cdot y = y \cdot x$ $(xy)z = x(yz)$    | x + 0 = x $x + x = x$ $x + y = y + x$ $(x + y) + z = x + (y + z)$   | identities<br>idempotent law<br>commutativity<br>associativity |

| ( 0 )                                                                      | $x + yz = (x + y)(x + z)$ $(x + y)x = x$ $(\overline{x} + y)x = xy$ | distribution<br>uniting theorem<br>uniting theorem v.2         |

| $\overline{x \cdot y} = \overline{x} + \overline{y}$                       | $\overline{x+y} = \overline{x} \cdot \overline{y}$                  | DeMorgan's Law                                                 |

| CS61C L25 Representations of                                               | Combinational Logic Circuits (19)                                   | Garcia, Fall 2014 © U                                          |