#### CS61C Fall 2015

| Guarril | la Ca | ccion | с. | Caches |

|---------|-------|-------|----|--------|

| Guerrii | ia se | ssion | э: | cacnes |

| Login: cs61c | duerrilla session s. caches |

|--------------|-----------------------------|

|--------------|-----------------------------|

1) 3) "Cache, money. Dollar bills, y'all." (24 min, 15 pts)

|    | ippose we have a standard 32-bit byte-addressed MIPS machine, a single direct-mapped 32KiB che, a write-through policy, and a 16B block size.                                                                                                                                                                  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Give the T:I:O breakup  How many bits are there per row on the cache?                                                                                                                                                                                                                                          |

| Su | se the C code below and the description of the cache above to answer the questions that follow it. In the only memory accesses are accesses and stores to arrays and that all memory cesses in the code are valid. Assume $\mathtt{A}$ starts on a block boundary (byte 0 of $\mathtt{A}$ in byte 0 of block). |

|    | efine NUM_INTS 32<br>efine OFFSET 8192 // 8192 = 2^13                                                                                                                                                                                                                                                          |

| in | t rand(int x, int y); // returns a random integer in the range $[x, y)$                                                                                                                                                                                                                                        |

| in | <pre>t main(){    int A[NUM_INTS + OFFSET];</pre>                                                                                                                                                                                                                                                              |

|    | <pre>// START LOOP 1 for ( int count = 0 ; count &lt; NUM_INTS ; count += 1 ) { // count by 1s</pre>                                                                                                                                                                                                           |

|    | <pre>// START LOOP 2 for ( int count = 0 ; count &lt; NUM_INTS ; count += 4 ) { // count by 4s now</pre>                                                                                                                                                                                                       |

| }  |                                                                                                                                                                                                                                                                                                                |

|    |                                                                                                                                                                                                                                                                                                                |

| c) | Hit rate for Loop 1? What types of misses are there?                                                                                                                                                                                                                                                           |

| d) | Hit rate for Loop 2? What types of misses are there?                                                                                                                                                                                                                                                           |

|    | Questions (e), (f), and (g) below are three independent variations on the original code & settings.                                                                                                                                                                                                            |

| e) | If the cache were 2-way set associative, what would be the hit rate for Loop 2?                                                                                                                                                                                                                                |

| f) | If instead we removed the line labeled ACCESS #2, what would be the hit rate for Loop 2?                                                                                                                                                                                                                       |

| g) | Instead, what's the smallest we could shrink OFFSET to maximize our Loop 2 hit rate?                                                                                                                                                                                                                           |

| 2) | Question 3: Our band is called 1023MiB We haven't had any gigs yet. (24 min, 15 pts)                                                                                                                                                                                                                   |                                                                                                                                                  |  |  |  |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|    | We have a standard 32-bit byte-addressed MIPS machine with a 1KiB direct-mapped write-back cache and 16B block size.                                                                                                                                                                                   |                                                                                                                                                  |  |  |  |  |

|    | a)                                                                                                                                                                                                                                                                                                     | How many bits are used for the Tag?Index?Offset?                                                                                                 |  |  |  |  |

|    | Consider the following C code, and answer the questions below. a and s are pointers to 8-bit unsigned integer arrays, of the same size (a multiple of the cache size) that are aligned on 16-byte boundaries. The arrays contain only one 0x00, in the last byte. a and s are not necessarily distinct |                                                                                                                                                  |  |  |  |  |

|    | <b>v</b> o:                                                                                                                                                                                                                                                                                            | <pre>id our_strcpy(uint8_t *d, uint8_t *s) {     char c;     do {         c = *s;         *d = c;         s++; d++; } while (c);</pre>           |  |  |  |  |

|    | b)                                                                                                                                                                                                                                                                                                     | What is the <i>lowest</i> possible cache hit rate for our_strcpy?                                                                                |  |  |  |  |

|    | c)                                                                                                                                                                                                                                                                                                     | What <i>types</i> of misses are there?                                                                                                           |  |  |  |  |

|    | d)                                                                                                                                                                                                                                                                                                     | What is the smallest possible value of (a - s) that would get this hit rate?                                                                     |  |  |  |  |

|    | e)                                                                                                                                                                                                                                                                                                     | What is the <i>highest</i> possible cache hit rate for our_strcpy?                                                                               |  |  |  |  |

|    | f)                                                                                                                                                                                                                                                                                                     | What is one possible value of (d - s) where we would get this hit rate?                                                                          |  |  |  |  |

|    | g)                                                                                                                                                                                                                                                                                                     | If we ran our_strcpy with a 4-way set-associative LRU cache, and the size of both d and s is 8MiB, what is the <i>most # of misses</i> possible? |  |  |  |  |

|    |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                  |  |  |  |  |

Show all your work here!

### 3) Q4: Cache Operations (6 points)

a) Consider a 32-bit physical memory space and a 32 KiB 2-way associative cache with LRU replacement. You are told the cache uses 5 bits for the offset field. Write in the number of bits in the tag and index fields in the figure below.

| Tag | Index | Offset |

|-----|-------|--------|

|     |       | 5 bits |

| 31  |       | 0      |

b) Assume the same cache as in part a).

```

int ARRAY_SIZE = 64 * 1024;

int arr[ARRAY_SIZE]; // *arr is aligned to a cache block

/* loop 1 */ for (int i = 0; i < ARRAY_SIZE; i += 8) arr[i] = i;

/* loop 2 */ for (int i = ARRAY SIZE - 8; i >= 0; i -= 8) arr[i+1] = arr[i];

```

- 1. What is the hit rate of loop 1? What types of misses (of the 3 Cs), if any, occur as a result of loop 1?

- 2. What is the hit rate of loop 2? What types of misses (of the 3 Cs), if any, occur as a result of loop 2?

# 4)Q5: AMAT (4 points)

Suppose you have the following system that consists of an: L1\$ with a local hit rate of 80% and a hit time of 2 cycles L2\$ with a global miss rate of 8% and a hit time of 15 cycles DRAM accesses take 50 cycles

i. What is the AMAT of the L1 cache?

ii. Suppose we want to improve our AMAT, making sure that it is no greater than 6 cycles, by improving our L2\$'s hit rate. What is the minimum possible local hit rate for L2\$ that allows us to meet our AMAT requirement?

| SID: |  |  |

|------|--|--|

## 5) Q6: Floating Point (6 points)

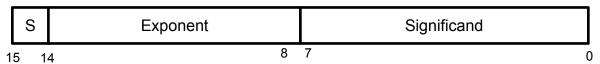

We want to develop a new half-precision floating-point standard for 16-bit machines. The basic structure is as follows:

Here are the design choices:

- 1 bit for sign

- 7 bits for a signed exponent in 2's complement

- 8 bits for the significand

- Everything else follows the IEEE standard 754 for floating point, except in 16 bits.

In this new standard:

- a) Convert the decimal number -10.625 to floating point. Write your answer in hexadecimal.

- b) What is the smallest even number that is not representable?

- c) What is the smallest positive denormalized number?

#### 6)M2-3) Cache Performance/AMAT (19 pts)

Each subproblem in this question can be done without the previous subproblems.

We have caches with the following configurations:

Cache-size: 1KiB, Block-size: 128B, Memory-size: 4 GiB, Write-policy: Write back and write-allocate

For the following scenarios calculate the <u>hit-rate</u> and specify which types of misses are encountered in the code between the lines marked start and stop. Assume all variables stay in registers and memory reads happen left to right in each line.

- a) i) Direct Mapped: # Tag/Index/Offset bits: [ \_\_\_\_\_ : \_\_\_\_ : \_\_\_\_ : \_\_\_\_ ]

- ii) What is the best-case hit rate? Also, state the types of misses.

iii) What is the worst-case hit rate? Also, state the types of misses.

- b) i) 2-way Set Assoc: # Tag/Index/Offset bits: [ \_\_\_\_\_ : \_\_\_\_ : \_\_\_\_ : \_\_\_\_ ]

- ii) What is the worst-case hit-rate? Assume we use LRU replacement. Also, state the types of misses.

c) Calculate the AMAT in cycles if the L1 <u>local</u> hit rate is 60%, with a hit time of 1 cycle, the L2 <u>global</u> hit rate is 20% with a hit time of 10 cycles and the main memory has a hit time of 200 cycles.