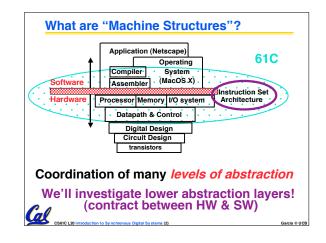

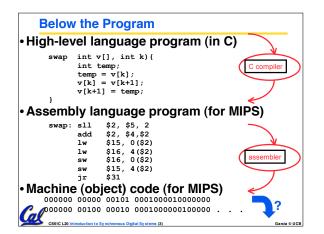

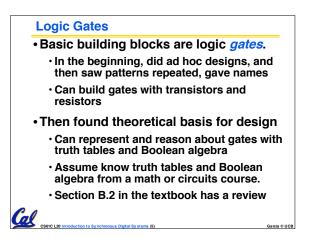

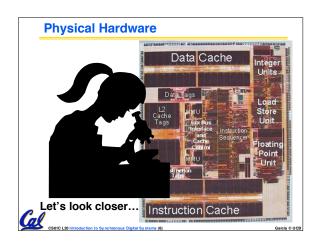

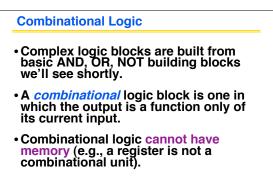

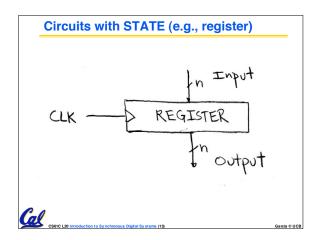

## Logic Design Next 2 weeks: we'll study how a modern processor is built starting with basic logic elements as building blocks. Why study logic design? · Understand what processors can do fast and what they can't do fast (avoid slow things if you want your code to run fast!) · Background for more detailed hardware courses (CS 150, CS 152)

a © UCB

Garcia © UCB

**G** CS61C L20

|    | Peer Instruction                                                                                                                          |                      | _                                      |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

| Α. | SW can peek at HW (past ISA                                                                                                               |                      | ABC                                    |

| A. | SW can peek at HW (past ISA abstraction boundary) for optimizations                                                                       | 1:                   | FFF                                    |

|    | abstraction boundary) for optimizations                                                                                                   | 1:<br>2:<br>3:       |                                        |

|    | abstraction boundary) for optimizations<br>SW can depend on particular HW                                                                 | 2:                   | FFF<br>FFT                             |

| В. | abstraction boundary) for optimizations<br>SW can depend on particular HW<br>implementation of ISA                                        | 2:<br>3:<br>4:<br>5: | FFF<br>FFT<br>FTF<br>FTT<br>TFF        |

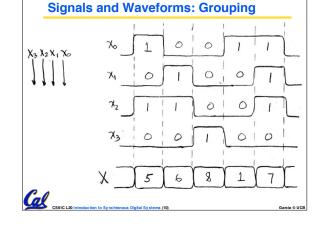

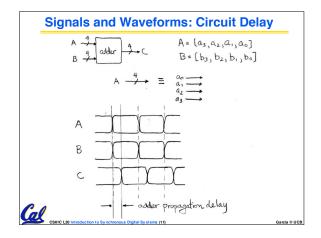

| В. | abstraction boundary) for optimizations<br>SW can depend on particular HW<br>implementation of ISA<br>Timing diagrams serve as a critical | 2:<br>3:<br>4:       | FFF<br>FFT<br>FTF<br>FTT<br>TFF<br>TFT |

| В. | abstraction boundary) for optimizations<br>SW can depend on particular HW<br>implementation of ISA                                        | 2:<br>3:<br>4:<br>5: | FFF<br>FFT<br>FTF<br>FTT<br>TFF        |

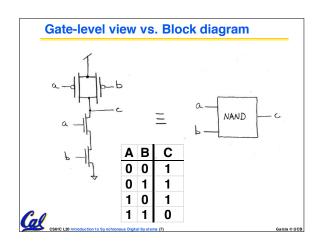

Stateless Combinational Logic (&,I,~)

Garcia © UCB

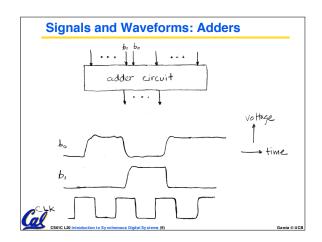

• State circuits (e.g., registers)