# $\begin{array}{ccc} {\rm Nick~Weaver} & {\rm CS~61C} \\ {\rm Sp~2019} & {\rm Great~Ideas~in~Computer~Architecture} \end{array}$

MT 2

| Print your name:                          | ,                                                                                                                                                                             |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (last)                                    | (first)                                                                                                                                                                       |

| academic misconduct will be reported to t | ede of Student Conduct and acknowledge that any<br>the Center for Student Conduct, and may result in<br>to aware that Nick Weaver takes cheating personally<br>see him angry. |

| Sign your name:                           |                                                                                                                                                                               |

| Print your class account login: cs61c     | and SID:                                                                                                                                                                      |

| Your Favorite 61C TA's name:              |                                                                                                                                                                               |

| Exam # for person sitting to your left:   | Exam # for person sitting to your right:                                                                                                                                      |

You may consult one sheet of paper (double-sided) of notes. You may not consult other notes, textbooks, etc. Calculators, computers, and other electronic devices are not permitted.

You have 110 minutes. There are 7 questions, of varying credit (90 points total). The questions are of varying difficulty, so avoid spending too long on any one question. Parts of the exam will be graded automatically by scanning the **bubbles you fill in**, so please do your best to fill them in completely. For short answer question use only the space provided and your answers must be short. You do not need to read any footnotes.

If you have a question, raise your hand, and when an instructor motions to you, come to them to ask the question.

## DO NOT SEPARATE THE PAGES OF THE EXAM

Do not turn this page until your instructor tells you to do so.

| Question: | 1  | 2  | 3  | 4  | 5  | 6  | 7  | Total |

|-----------|----|----|----|----|----|----|----|-------|

| Points:   | 10 | 10 | 10 | 12 | 18 | 12 | 18 | 90    |

Look at the Boolean Expression Table. We'd like to implement its functionality as a circuit!

| A                                              | В                                      | $\mid C \mid$ | $\mid D \mid$ | OUT                   |

|------------------------------------------------|----------------------------------------|---------------|---------------|-----------------------|

| 0                                              | 0                                      | 0             | 0             | 0                     |

| 0                                              | 0                                      | 0             | 1             | 0                     |

| 0                                              |                                        | 1             | 0             | 0                     |

| 0                                              | 0                                      | 1             | 1             | 0                     |

| 0                                              | 1                                      | 0             | 0             | 0<br>0<br>0<br>0      |

| 0                                              | 1                                      | 0             | 1             | 0                     |

| 0                                              | 1                                      | 1             | 0             | 1                     |

| 0                                              | 1                                      | 1             | 1             | 1                     |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 0                                      | 0             | 0             | 0                     |

| 1                                              | 0                                      | 0             | 1             | 0                     |

| 1                                              | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$ | 1             | 0             | 1                     |

| 1                                              | 0                                      | 1             | 1             | 1                     |

| 1                                              | 1                                      | 0             | 0             | 0                     |

| 1                                              | 1                                      | 0             | 1             | 0<br>1<br>1<br>0<br>0 |

| 1                                              | 1                                      | 1             | 0             | 0                     |

| 1                                              | 1                                      | 1             | 1             | 0                     |

Table 1: Boolean Expression Table

| (a) | Write a | boolean  | ${\it expression}$ | that | ${\it represents}$ | this | truth | table | as | a sum | of | products | 3. |

|-----|---------|----------|--------------------|------|--------------------|------|-------|-------|----|-------|----|----------|----|

|     | You do  | not need | to simplify        | your | answer.            |      |       |       |    |       |    |          |    |

(b) Simplify the boolean expression from the previous part such that your expression uses the minimum number of gates. Show your work clearly.

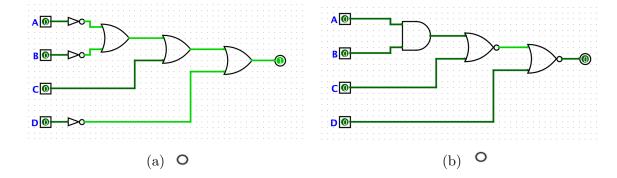

(c) Now we'll work with a new expression:

$$\overline{\overline{(\overline{A}\overline{B}+C)}D}$$

Select the correctly simplified circuit.

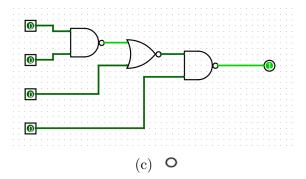

Problem 2 FSMs (10 points)

Complete the states and transitions on the FSM below. For full credit, use the minimum number of states. Our FSM should output 1 if the bit stream is currently a power of 4 and 0 otherwise. Note that 0 is not a power of 4. Label all transitions with *input/output* notation used in discussion section. The first set of transitions has been done for you. Assume we append bits to the least-significant end of the bit stream and our number is interpreted as an unsigned integer.

The following table shows the inputs/outputs at each step as we try to parse the bit-string 001000

| Input Stream | Output Stream |

|--------------|---------------|

| 0            | 0             |

| 00           | 00            |

| 001          | 001           |

| 0010         | 0010          |

| 00100        | 00101         |

| 001000       | 001010        |

| In an (in | Single Cycle Datapath accorrect) implementation of the RISC- the opposite MUXes. ASel to Mux B a | V Datapath, the ASel and BS | (10 points)<br>Sel signal are |

|-----------|--------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|

| (a) Wh    | nich instruction types still work all of t                                                       | the time?                   |                               |

| 0         | R                                                                                                | O UJ                        |                               |

| 0         | SB                                                                                               | o I                         |                               |

| 0         | U                                                                                                |                             |                               |

|           |                                                                                                  |                             |                               |

- (b) Which of the following lines of code will execute incorrectly on the wonky datapath?

- O addi t0 t0 2 O jalr ra 0(a0)

- O beq t1 s0 LABEL

| Con<br>and | m 4 Floating Point (12 points) sider a modified floating point scheme where we opt to use 7 bits for the exponent 24 bits for the significand but is otherwise the same as IEEE 754 Single Precision ting Point (what you learned in lecture). |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a)        | What is the new bias for our Floating Point Scheme? Write your answer in decimal.                                                                                                                                                              |

|            | Bias:                                                                                                                                                                                                                                          |

| (b)        | Represent 18.75 in our new Floating Point Scheme. You may leave your answer in hex or binary.                                                                                                                                                  |

|            | Sign:                                                                                                                                                                                                                                          |

|            | Exponent:                                                                                                                                                                                                                                      |

|            | Significand:                                                                                                                                                                                                                                   |

|            |                                                                                                                                                                                                                                                |

|            |                                                                                                                                                                                                                                                |

|            |                                                                                                                                                                                                                                                |

| (c)        | What is the largest finite value you can represent?                                                                                                                                                                                            |

|            | Sign:                                                                                                                                                                                                                                          |

Exponent: \_\_\_\_\_

Significand:

|     |   | ect the best answer to the required.           | ollowing multi | ple choice questions. | No explanation   |

|-----|---|------------------------------------------------|----------------|-----------------------|------------------|

| (d) |   | can represent<br>n we can in single precision  |                |                       | ng point scheme  |

|     | 0 | More                                           | 0              | The same amount       |                  |

|     | 0 | Fewer                                          |                |                       |                  |

|     |   |                                                |                |                       |                  |

|     |   |                                                |                |                       |                  |

|     |   |                                                |                |                       |                  |

|     |   |                                                |                |                       |                  |

| (e) |   | can represent<br>nt scheme than we can in size | _              |                       | our new floating |

|     |   |                                                |                |                       |                  |

|     | 0 | More                                           | 0              | The same amount       |                  |

|     | 0 | Fewer                                          |                |                       |                  |

|       | *                                    | with four word blocks, a cache size of 2 KiB, What is the T:I:O breakdown for the cache? ded.   |

|-------|--------------------------------------|-------------------------------------------------------------------------------------------------|

| Tag:  |                                      |                                                                                                 |

| Inde  | x:                                   |                                                                                                 |

| Offse | et:                                  |                                                                                                 |

|       |                                      |                                                                                                 |

|       |                                      |                                                                                                 |

| lengt | _                                    | r False and justify your answer in a tweet-<br>ification (or with incorrect justification) will |

| 1. ]  | Increasing a cache's block size alwa | ays decreases the AMAT.                                                                         |

|       |                                      |                                                                                                 |

| ,     | O True                               | • False                                                                                         |

| •     | O True                               | • False                                                                                         |

| -     | O True                               | • False                                                                                         |

| -     | O True                               | • False                                                                                         |

| -     | • True                               | • False                                                                                         |

| -     | • True                               | • False                                                                                         |

| -     | • True                               | • False                                                                                         |

| 2. ]  |                                      | • False gher hit time than direct mapped caches of                                              |

| 2. ]  | Fully associative caches have a hig  |                                                                                                 |

${\bf Problem~5} \quad Short~Cache/AMAT~Questions$

(18 points)

| O True O False  1. If the majority of misses in our cache are conflict misses then switching to a fully associative cache will always produce at least the same hit rate. O True O False | 3. |   | Doubling the size of our cache but keeping the block size and associativity the same will always produce at least the same hit rate. |         |   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|--------------------------------------------------------------------------------------------------------------------------------------|---------|---|--|--|--|--|

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    | 0 | True                                                                                                                                 | O False |   |  |  |  |  |

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    |   |                                                                                                                                      |         |   |  |  |  |  |

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    |   |                                                                                                                                      |         |   |  |  |  |  |

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    |   |                                                                                                                                      |         |   |  |  |  |  |

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    |   |                                                                                                                                      |         |   |  |  |  |  |

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    |   |                                                                                                                                      |         |   |  |  |  |  |

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    |   |                                                                                                                                      |         |   |  |  |  |  |

| fully associative cache will always produce at least the same hit rate.                                                                                                                  |    |   |                                                                                                                                      |         |   |  |  |  |  |

| O True                                                                                                                                                                                   | 1. |   |                                                                                                                                      |         | a |  |  |  |  |

|                                                                                                                                                                                          |    | 0 | True                                                                                                                                 | O False |   |  |  |  |  |

|                                                                                                                                                                                          |    |   |                                                                                                                                      |         |   |  |  |  |  |

|                                                                                                                                                                                          |    |   |                                                                                                                                      |         |   |  |  |  |  |

|                                                                                                                                                                                          |    |   |                                                                                                                                      |         |   |  |  |  |  |

| (c) | Assume that the local hit rate for our L1 cache is 40% and the local hit rate for our L2 cache is also 40%. The hit time for the L1 cache is 5 cycles, the hit time for the L2 cache is 25 cycles, and access time for main memory is 100 cycles. Find the average memory access time. Express your answer in terms of cycles. |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | AMAT = Cycles                                                                                                                                                                                                                                                                                                                  |

### Problem 6 Maybe cache(s) can buy happiness...

(12 points)

You have secured a fancy summer internship analyzing cache performance at a data processing company Glamazon, and you don't want to F@#)(\* it up. In your first week, you discover the average user has a hit rate of 20% and an 80% miss rate. Furthermore, you find the misses follow (roughly) the following distribution:

Compulsory: 20% Capacity: 6% Conflict: 74%

Your users' main system has 256 B direct mapped cache with 16 B blocks. Glamazon is also installing a fancy new machine with an 1024 B 2-way set associative cache with 4B blocks. Both machines feature a 32-bit architecture.

(a) After migrating all your users to the new machine, you get an angry call from a customer complaining their results arent rolling in as fast as they used to. Which of the following miss-classification profiles likely belongs to this customer?

O Compulsory: 80% Capacity: 16% Conflict: 4% O Compulsory: 3% Capacity: 79% Conflict: 18%

O Compulsory: 13% Capacity: 12% Conflict: 75%

O Compulsory: 80% Capacity: 15% Conflict: 15% You open up the customers main processing program and see the following.

You decide to test the function with the following parameters:

```

genFakeReviews(products, 20, fakeReviews, 20);

```

You may assume the arrays are block aligned and do not overlap or contain overlapping elements. When loaded into memory, products lives at 0x04000000 and fakeReviews lives at 0x08000000. Assume function call operands are always evaluated left to right.

(b) You simulate the code on the old cache (256 B direct mapped cache with 16 B blocks). What is the hit rate?

| • |   |   |   |

|---|---|---|---|

|   | : | : | : |

(c) You simulate the code on the new cache (1024 B 2-way set associative cache with 4B blocks). What is the hit rate?

| Hit Rate: |  |

|-----------|--|

|           |  |

| (d) | You find your simulation results confusing, so you run the code again on each simulation. In your haste you forget to clear the caches, so the data from the previous runs sticks around. |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | How do the new, second round hit rates compare?                                                                                                                                           |

O They are equal O The new caches second run is better than the old caches second run

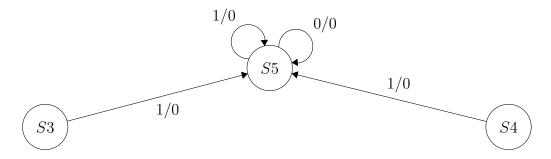

O The old caches second run is better than the new caches second run The missing part of a basic five-stage RISC-V pipeline before we added forwarding that we dont cover in lecture is the hardware logic that decides when to insert stalls if we have a data hazard. Lets put it together now! Heres an outline of a hardware unit that will decide if we need a stall due to a data hazard in that youll fill in the missing pieces for. Each clock cycle, it takes in the 5-bit signals for rd, rs1, and rs2 that come into the Instruction Decode phase and it outputs the number of stalls that are necessary. For this question we will assume all of our instructions are R-Type Instructions, every instruction will write to rd and use rs1 and rs2. Additionally we assume that you cannot read and write in the same clock cycle, which means you could need to stall as many as 3 clock cycles.

In the diagram below you will see that we store the value of rd for each of the past 3 instructions, which are from top to bottom, rd[i-1], rd[i-2], and rd[i-3] respectively.

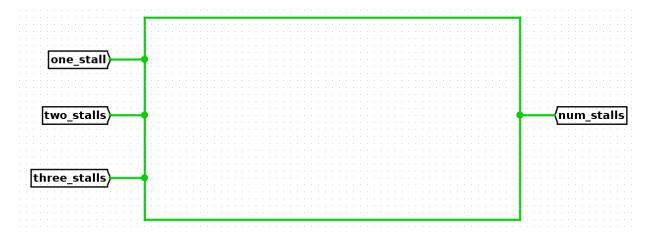

#### (a) Pick maximum stalls

Fill in the logic below that takes in three one-bit signals (one\_stall, two\_stalls, and three\_stalls) and output a constant representing the maximum number of stalls (i.e. 3 if three\_stalls is 1, 2 if two\_stalls is 1, 1 if one\_stall is 1, and 0 otherwise). If multiple signals are 1, for example, if one\_stall and three\_stalls are both 1, the circuit should output a 3. You may use any combination of constants and the components listed on the Logisim Cheat Sheet on the back this exam, but nothing else.

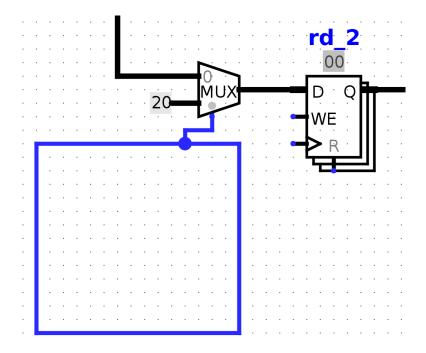

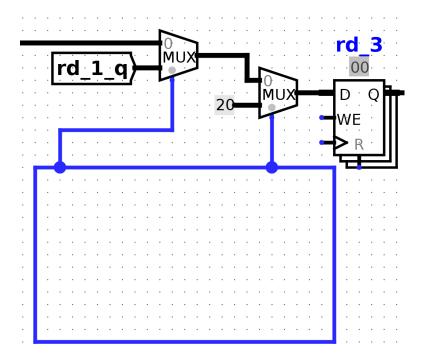

# (b) Flush

When we stall, we want to flush whatever is in the pipeline so that we don't have any unnecessary stalls in the future. Fill in the diagram below with the appropriate stalling logic for rd[i-2], and rd[i-3] so that we can output the correct number of stalls.

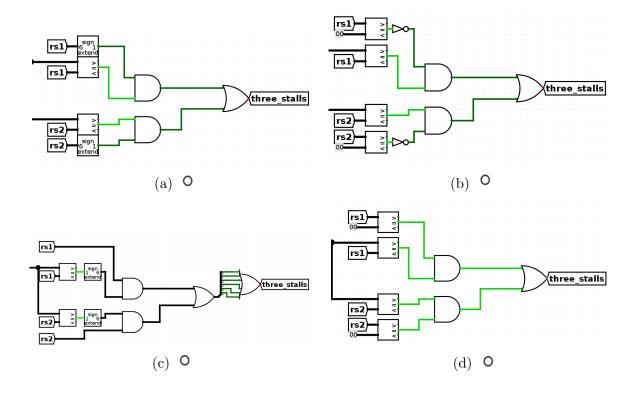

# (c) x0 Optimization

You'll notice that the logic we provided stalls even if the register we write back to is x0. This is unnecessary, and we can optimize it out. Select all of the following modifications that produce three stalls when necessary and not when rd[i-1] is x0.

Figure 3: Good Luck And Don't F\*@)! It Up