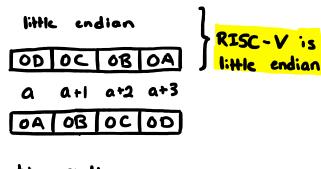

### 1 Endianness

Consider some value 0x0AOBOCOD stored at address a...

There are two ways to store this 4 byte value

big endian

# @ Addressing

Consider some address Ox AABBCCOD that we wish to access in memory. The memory unit will only fetch the top 30 bits of this address. This means that to memory our effective address is the 30 bit value Ox 2AAEF337.

Note that memory <u>always</u> returns the 4 byte word from a referenced effective address.

#### 3 Write Masks

The provided memory is byte level write enabled. This means that our write enable is a 4-bit signal where each bit corresponds to one byte in the addressed word.

Say we have some address a which contains  $0 \times 0.020304$  and we wish to write some new value  $0 \times AABBCCDD$ . The following examples show the effects of some different write enables

#### Original:

04 03 02 01 0 041 042 043

Wen = 4'b1111:

DD CC 88 AA

Wen = 4/61000:

04 03 02 AA a a+1 a+2 a+3

Wen = 4'60110:

04 CC 88 01 a at 1 at 2 at 3

This may seem confusing at first glance, but can be simplified to: if bit i of wen is 2, write byte i of Din into the ith byte of the word in memory at address a. Remember that regardless of your original address, the effective address will be word aligned!

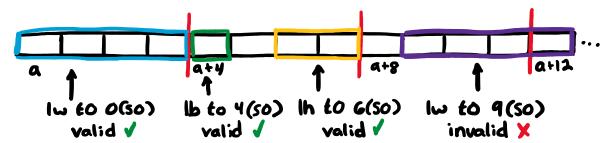

## 4 Valid Loads/Stores

The rule for loads and stocks is as follows:

Any request where the requested Section does not break the boundary of a contiguous 4-byte word in memory is valid.

But what does that mean? Consider some address a, and some register so containing a. We can represent bytes in memory as boxes, and requests as overlays. We draw a red line to mark the boundary between contiguous words. Any request where the overlay box does not break the red line is valid.

Below are some examples of this, you are encouraged to build on these examples to determine what is valid for each load/store type.