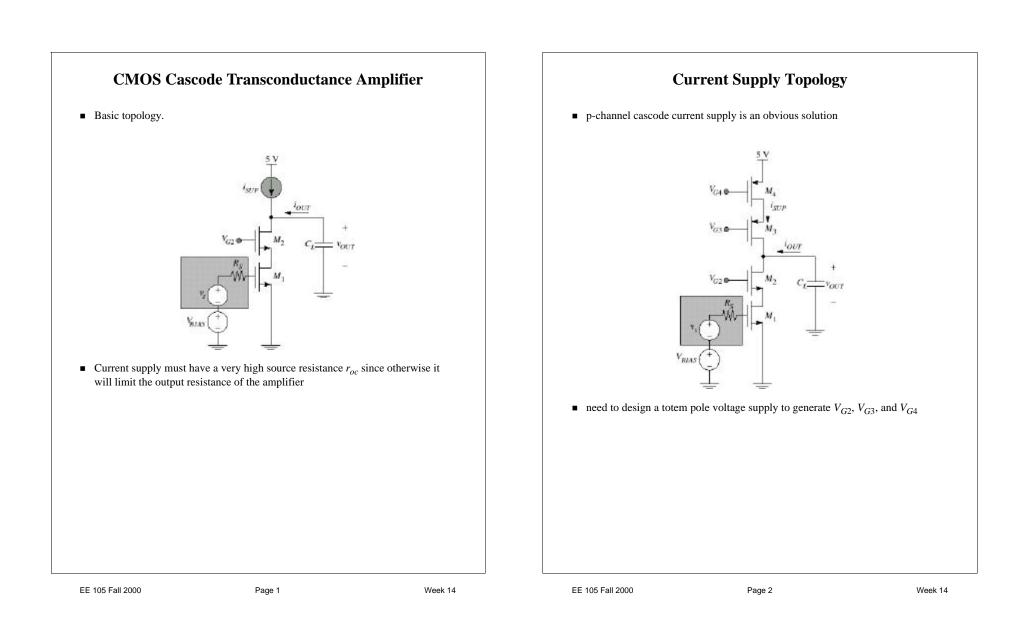

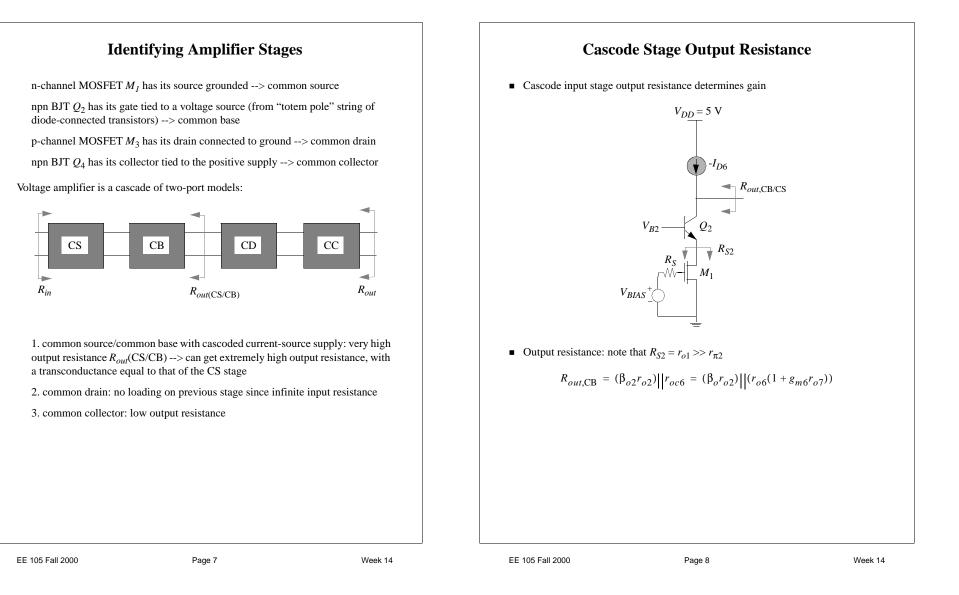

- 1. replace all transistor current sources and voltage sources by their symbols -- look for diodes and current mirrors!  $(M_5, M_6/M_{6B}, M_7/M_{7B}, \text{ and } M_{10} \text{ and } Q_{2B}$  are part of current sources or a totem pole voltage reference.)

- 2. for the (few) remaining transistors, identify the type and use two-port small-signal models to understand the circuit's operation. (For the above amplifier, the remaining transistors are  $M_1, Q_2, M_3$ , and  $Q_4$ .)

#### EE 105 Fall 2000

Week 14

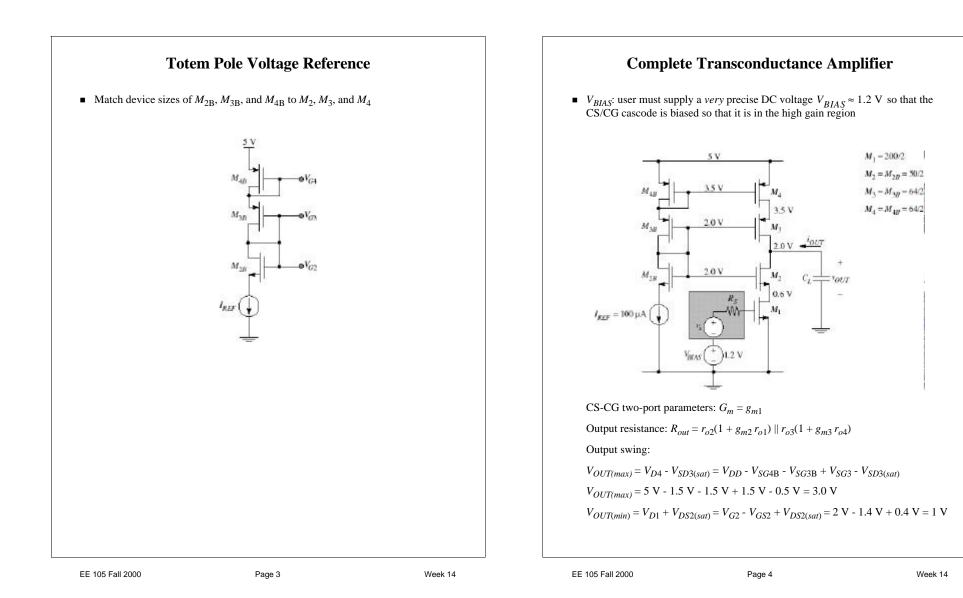

# **Eliminating Current and Voltage Sources**

Replace current and voltage sources with symbols

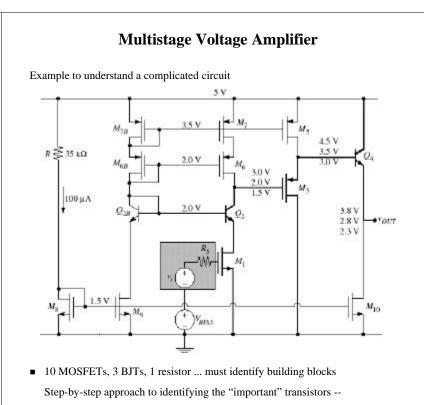

## **CS-CB-CD-CC** Two-Port Parameters

- Since CC and CD stages have unity gain (approximately), we can quickly estimate the voltage gain by finding v<sub>in3</sub>/v<sub>in</sub> where v<sub>in3</sub> is the input to the CD stage

- Voltage gain:

$$A_v \approx (-g_{m1})R_{out,CB} = -g_{m1}((\beta_o r_{o2})||(r_{o6}(1+g_{m6}r_{o7})))$$

• Output resistance: source resistance of CC output stage is relatively small, since it preceded by a CD stage.

$$R_{out} = R_{out,CC} \approx \frac{1}{g_{m4}} + \frac{R_{S,CC}}{\beta_{o4}} = \frac{1}{g_{m4}} + \frac{1}{g_{m3}\beta_{o4}}$$

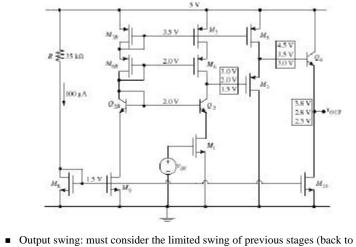

## **DC Bias and Output Swing**

• Assuming all n-channel devices have  $V_{GS} = 1.5$  V and p-channel devices have  $V_{SG} = 1.5$  V, we can find all the node voltages ... we also assume that  $V_{BIAS}$  has been adjusted such that the circuit is in the high-gain region

Output swing: must consider the limited swing of previous stages (back to cascode) since the the CD/CC output stages are "DC level shifters"

EE 105 Fall 2000

Week 14

EE 105 Fall 2000

# Multistage Amplifier Frequency Response

- Summary of frequency response of single-stages:

- CE/CS: suffers from Miller effect

- CC/CD: "wideband" -- see Section 10.5

- CB/CG: "wideband" -- see Section 10.6

(wideband means that the stage operates to near the frequency limit of the device  $\dots f_T$ )

- How to find the Bode plot for a general multistage amplifier?

can't handle *n* poles and *m* zeroes analytically --> SPICE!

develop analytical tool for an important special case:

- \* no zeroes

- \* exactly one "dominant" pole ( $\omega_1 << \omega_2, \omega_3, \dots, \omega_n$ )

$$\frac{V_{out}}{V_{in}} = \frac{A_o}{(1+j(\omega/\omega_1))(1+j(\omega/\omega_2))(\dots)(1+j(\omega/\omega_n))}$$

(the example shows a voltage gain ... it could be  $I_{out}/V_{in}$  or  $V_{out}/I_{in}$ )

## Finding the Dominant Pole

• Multiplying out the denominator:

$$\frac{V_{out}}{V_{in}} = \frac{A_o}{1 + b_1 j \omega + b_2 (j \omega)^2 + \dots + b_n (j \omega)^n}$$

The coefficient  $b_1$  originates from the sum of  $j\omega/\omega_i$  factors --

$b_1 = \frac{1}{\omega_1} + \frac{1}{\omega_2} + \ldots + \frac{1}{\omega_n} = \sum_{i=1}^n \frac{1}{\omega_i} \approx \frac{1}{\omega_1}$

Therefore, if we can estimate the linear coefficient  $b_1$  in the demoninator polynomial, we can estimate of the dominant pole

- Procedure: see P. R. Gray and R. G. Meyer, *Analysis and Design of Analog* Integrated Circuits, 3<sup>rd</sup> ed., Wiley, 1994, pp. 502-504.

- 1. Find circuit equations with current sources driving each capacitor

- 2. Denominator polynomial is determinant of the matrix of coefficients

- 3.  $b_1$  term comes from a sum of terms, each of which has the form:

$R_{Ti} C_i$

where  $C_j$  is the  $j^{\text{th}}$  capacitor and  $R_{Tj}$  is the Thévenin resistance across the  $j^{\text{th}}$  capacitor terminals (with all capacitors open-circuited)

EE 105 Fall 2000

# **Open-Circuit Time Constants**

• The dominant pole of the system can be estimated by:

$$\omega_1 \approx \frac{1}{b_1} = \left(\sum_j^n R_{Tj} C_j\right)^{-1} = \left(\sum_1^n \tau_j\right)^{-1},$$

where  $\tau_i = R_{T_i} C_i$  is the **open-circuit time constant** for capacitor  $C_i$

• This technique is valuable because it estimates the contribution of each capacitor to the dominant pole frequency *separately* ... which enables the designer to understand what part of a complicated circuit is responsible for limiting the bandwidth of the amplifier.

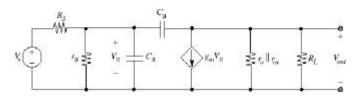

## **Example: Revisit CE Amplifier**

Small-signal model:

- Apply procedure to each capacitor separately

- 1.  $C_{\pi}$ 's Thévenin resistance is found by inspection as the resistance across its terminals with all capacitors open-circuited:

$$R_{T\pi} = R_{S} || r_{\pi} = R_{in}' - \tau_{C_{\pi o}} = R_{T\pi} C_{\pi}$$

2.  $C_{\mu}$ 's Thévenin resistance is *not* obvious --> must use test source and network analysis

EE 105 Fall 2000

Week 14

Page 14

## **Estimate of Dominant Pole for CE Amplifier**

• Estimate dominant pole as inverse of sum of open-circuit time constants

$$\omega_1^{-1} = (R_{T\pi}C_{\pi} + R_{T\mu}C_{\mu}) = R_{in}'C_{\pi} + (R_{in}' + R_{out}' + g_mR_{in}'R_{out}')C_{\mu}$$

inspection --> identical to "exact" analysis (which also assumed  $\omega_1 \ll \omega_2$ )

Advantage of open-circuit time constants: *general* technique Example: include C<sub>cs</sub> and estimate its effect on ω<sub>1</sub>

EE 105 Fall 2000

EE 105 Fall 2000

Week 14

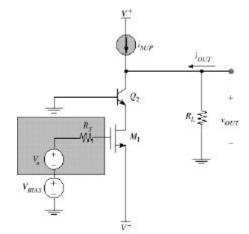

• Applying the open-circuit time constant technique to find the dominant pole frequency -- use CS/CB cascode as an example

• Systematic approach:

- 1. two-port small-signal models for each stage (not the device models!)

- carefully add capacitances across the appropriate nodes of two-port models, which may not correspond to the familiar device configuation for some models

We have omitted  $C_{db1}$ , which would be in parallel with  $C_{\pi 2}$  at the output of the CS stage, and  $C_{cs2}$  which would be in parallel with  $C_{\mu 2}$ . In addition, the current supply transistor will contribute additional capacitance to the output node.

Time constants

$$\tau_{C_{gs1o}} = R_{S}C_{gs1}$$

$$\tau_{C_{gd1o}} = (R_{in}' + R_{out}' + g_{m1}R_{in}'R_{out}')C_{gd1}$$

where

$$R_{in}' = R_S$$

and  $R_{out}' = r_{o1} || (\frac{1}{g_{m2}}) \approx \frac{1}{g_{m2}}$

Since the output resistance is only  $1/g_{m2}$ , the Thévenin resistance for  $C_{gd1}$  is not magnified (i.e., the Miller effect is minimal):

$$\pi_{C_{gd1o}} = \left( R_S + \frac{1}{g_{m2}} + \left( \frac{g_{m1}}{g_{m2}} \right) R_S \right) C_{gd1} \approx R_S (1 + g_{m1} / g_{m2}) C_{gd1}$$

EE 105 Fall 2000

Page 17

Week 14

EE 105 Fall 2000

Page 18

Week 14

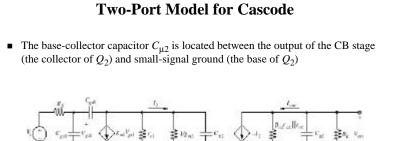

# **Cascode Frequency Response (cont.)**

• The base-emitter capacitor of  $Q_2$  has a time constant of

$$\tau_{C_{\pi 2o}} = \left(\frac{1}{g_{m2}}\right) C_{\pi 2}$$

• The base-collector capacitor of  $Q_2$  has a time constant of

$$\tau_{C_{\mu 2o}} = (\beta_{o2} r_{o2} || r_{oc} || R_L) C_{\mu 2} \approx R_L C_{\mu 2}$$

• Applying the theorem, the dominant pole of the cascode is approximately

$$\omega_{3db}^{-1} \approx \tau_{C_{gs1o}} + \tau_{C_{gd1o}} + \tau_{C_{\pi 2o}} + \tau_{C_{\mu 2o}}$$

$$\omega_{3db}^{-1} \approx R_S C_{gs1} + R_S (1 + g_{m1} / g_{m2}) C_{gd1} + \left(\frac{1}{g_{m2}}\right) C_{\pi 2} + R_L C_{\mu 2}$$

## **Gain-Bandwidth Product**

• A useful metric of an amplifier's frequency response is the product of the low-frequency gain  $|A_{vo}|$  and the 3 dB frequency  $\omega_{3dB}$

For the cascode, the gain is  $|A_{vo}| = |-g_{m1}R_L|$  and the gain-bandwidth product is

$$A_{vo} | \omega_{3dB} \approx \frac{g_{m1}R_L}{R_S C_{gs1} + R_S (1 + g_{m1}/g_{m2})C_{gd1} + \left(\frac{1}{g_{m2}}\right)C_{\pi 2} + R_L C_{\mu 2}}$$

• If the voltage source resistance is small, then

$$|A_{vo}|\omega_{3dB} \approx \frac{g_{m1}R_L}{(C_{\pi 2}/g_{m2} + R_L C_{\mu 2})}$$

which has the same form as the common-base gain-bandwidth product (and which is *much* greater than the Miller-degraded common-source)

EE 105 Fall 2000

Page 19

Week 14

Page 20