#### Lecture 23: Multistage Amps-Cascades and Cascodes

#### Prof. Niknejad

**Department of EECS**

University of California, Berkeley

### Lecture Outline

- Example 1: Cascodes Amp Design

- Example 2: Two Stage CS Amp

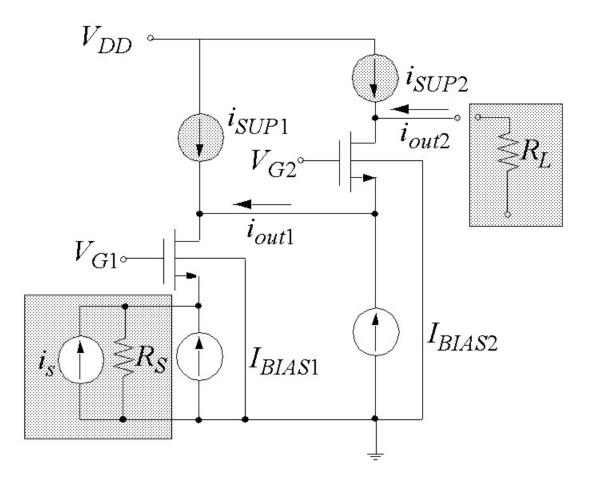

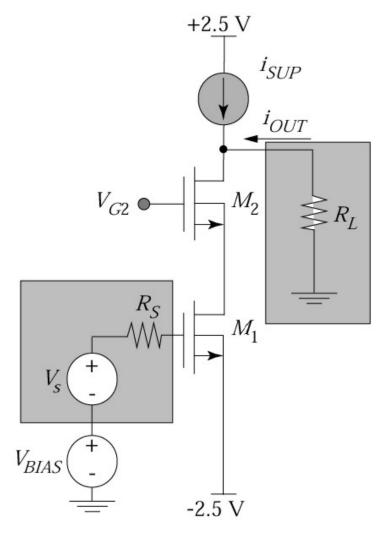

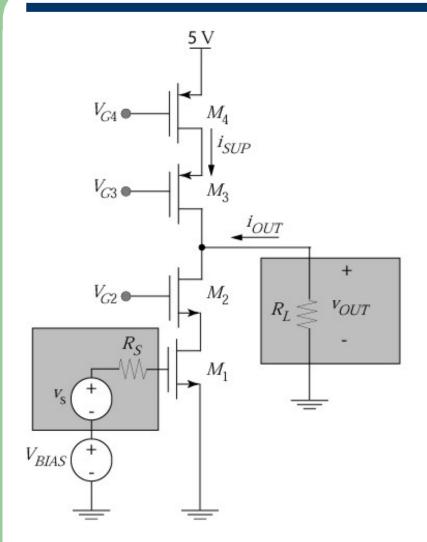

## **CG Cascade:** DC Biasing

Two stages can have different supply currents

Extreme case:  $I_{BIAS2} = 0 \text{ A}$

## **CG Casc**ade: Sharing a Supply

Department of EECS

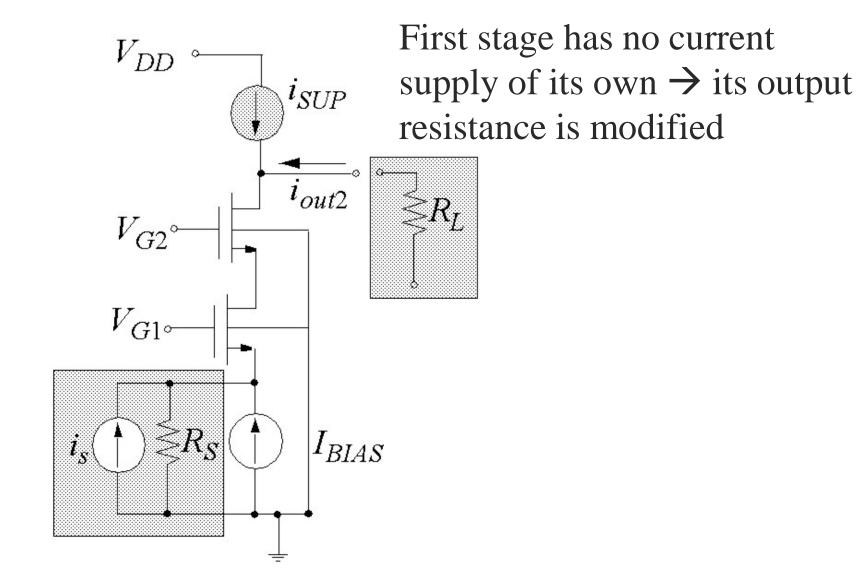

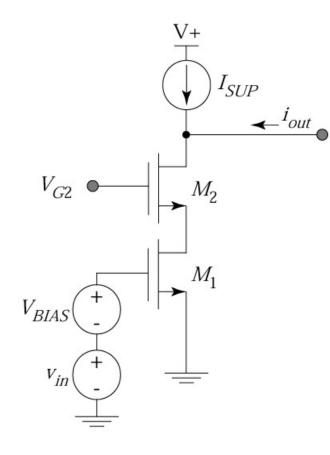

## **The Cascode Configuration**

Common source / common gate cascade is one version of a *cascode* (all have shared supplies)

DC bias:

Two-port model: first stage has no current supply of its own

Prof. A. Niknejad

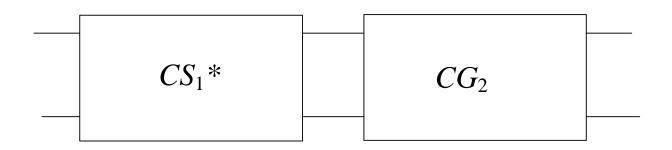

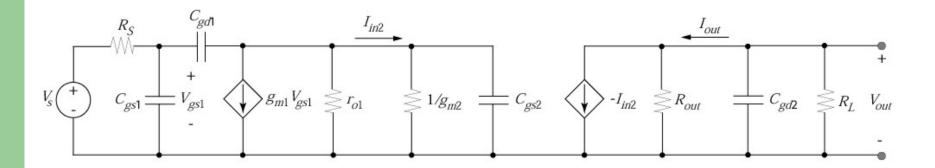

### **Cascode Two-Port Model**

Output resistance of first stage =  $R_{out,CS^*} = R_{down,CS} = r_{o1}$

$$R_{out} \simeq r_{oc2} \parallel (1 + g_m r_{o1}) r_{o2}$$

$$G_m = g_{m1}$$

$$R_{in} = \infty$$

#### Why is the cascode such an important configuration?

Department of EECS

University of California, Berkeley

# Miller Capacitance of Input Stage

#### Find the Miller capacitance for $C_{gd1}$

Input resistance to common-gate second stage is low  $\rightarrow$ gain across  $C_{gd1}$  is small.

Prof. A. Niknejad

#### **Two-Port Model with Capacitors**

Miller capacitance:  $C_M = (1 - A_{vC_{gd1}})C_{gd1}$

$$A_{vC_{gd1}} = -g_{m1}\left(\frac{1}{g_{m2}} \| r_{o1}\right) \approx -\frac{g_{m1}}{g_{m2}} = -1$$

$$C_M = 2C_{gd}$$

University of California, Berkeley

Department of EECS

D

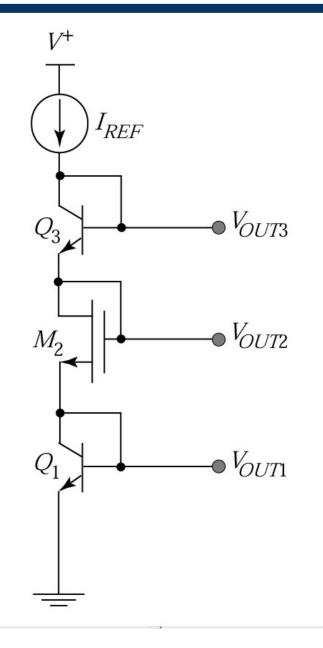

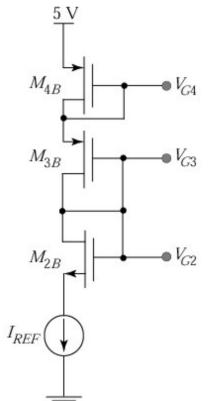

#### **Generating Multiple DC Voltages**

Stack-up diode-connected MOSFETs or BJTs and run a reference current through them  $\rightarrow$  pick off voltages from gates or bases as references

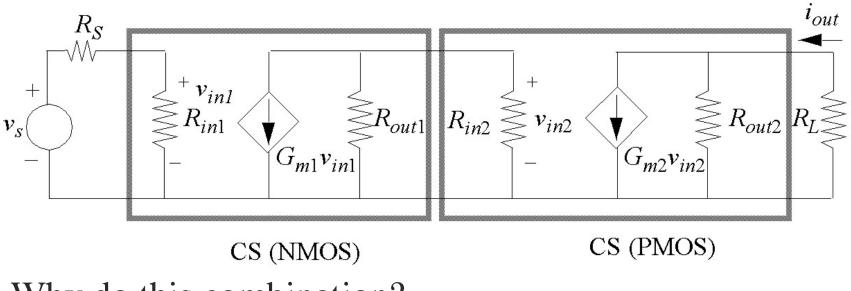

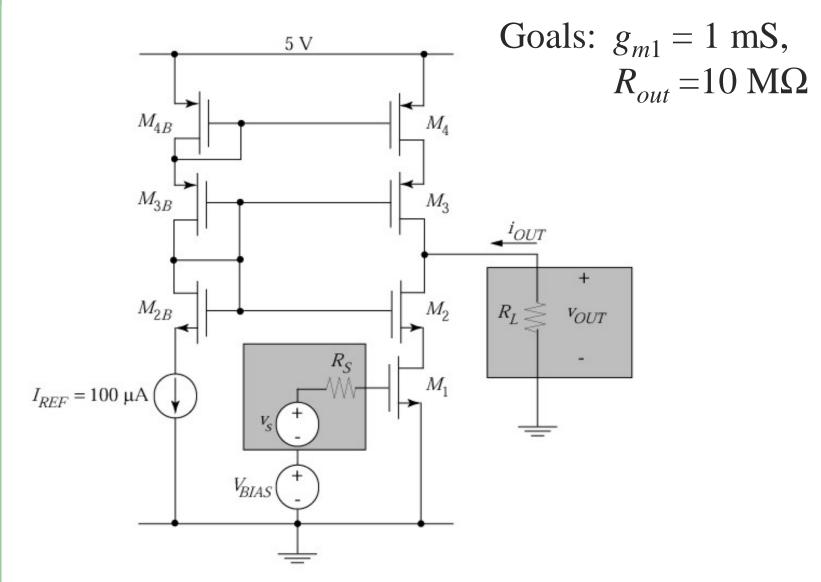

#### **Multistage Amplifier Design Examples**

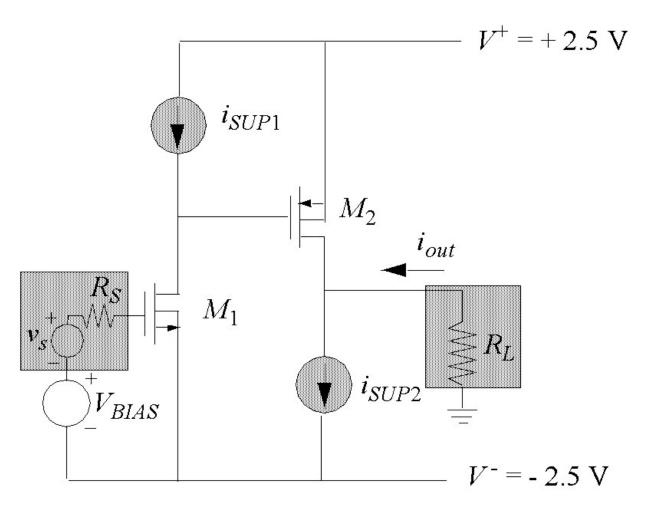

Start with basic two-stage transconductance amplifier:

Why do this combination?

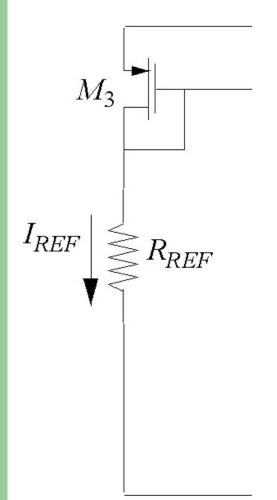

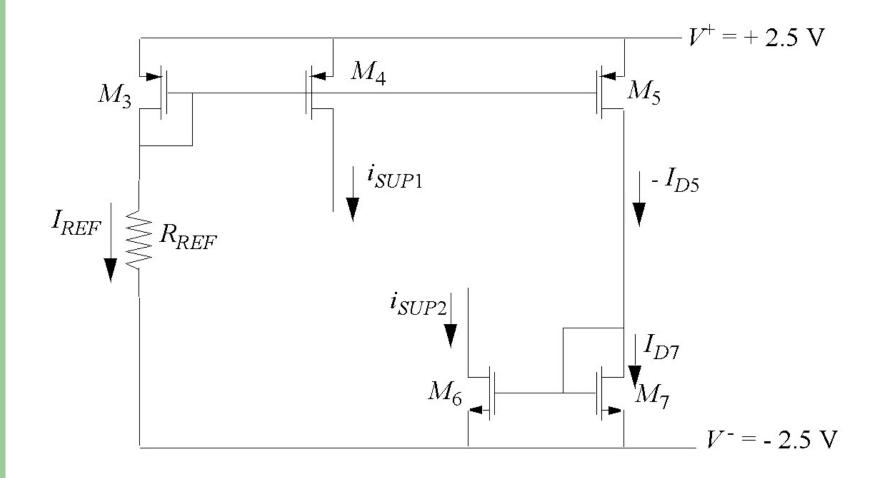

#### **Current Supply Design**

Output resistance goal requires large  $r_{oc} \rightarrow$ use cascode current source

#### **Totem** Pole Voltage Supply

DC voltages must be set for the cascode current supply transistors  $M_3$  and  $M_4$ , as well as the gate of  $M_2$ .

Why include  $M_{2B}$ ?

### **Complete Amplifier Schematic**

Department of EECS

### **Device Sizes**

$M_1$ : select  $(W/L)_1 = 200/2$  to meet specified  $g_{m1} = 1$  mS  $\rightarrow$  find  $V_{RIAS} = 1.2$  V Cascode current supply devices: select  $V_{SG} = 1.5$  V  $(W/L)_4 = (W/L)_{4B} = (W/L)_3 = (W/L)_{3B} = 64/2$  $M_2$ : select  $(W/L)_2 = 50/2$  to meet specified  $R_{out} = 10 \text{ M}\Omega$  $\rightarrow$  find  $V_{GS2} = 1.4$  V Match  $M_2$  with diode-connected device  $M_{2B}$ .

Assuming perfect matching and zero input voltage, what is  $V_{OUT}$ ?

Prof. A. Niknejad

EECS 105 Fall 2003, Lecture 23

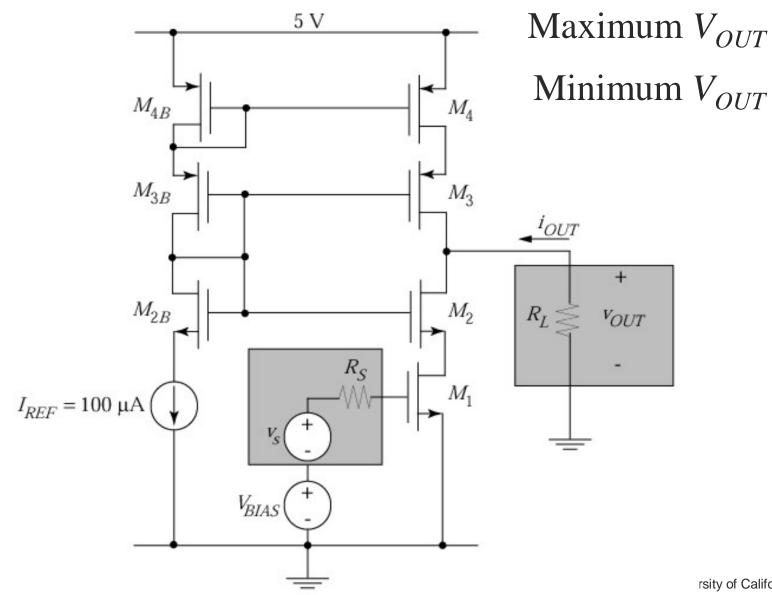

# **Output (Voltage) Swing**

rsity of California, Berkeley

#### **Two-Port Model**

Find output resistance  $R_{out}$

$$λn = (1/20) V-1, λn = (1/50) V-1 at L = 2 μm →

ron = (100 μA / 20 V-1)-1 = 200 kΩ, rop = 500 kΩ$$

$$g_{m2} = \frac{2I_{D2}}{V_{GS2} - V_{Tn}} = \frac{2(100\,\mu A)}{1.4V - 1V} = 500\,\mu S$$

$$g_{m3} = \frac{2(-I_{D3})}{V_{SG3} + V_{Tp}} = \frac{2(100\,\mu A)}{1.5V - 1V} = 400\,\mu S$$

$$R_{out} = r_{oc} \| r_{o2} (1 + g_{m2} R_{s2}) = r_{o3} (1 + g_{m3} R_{s3}) \| r_{o2} (1 + g_{m2} r_{o1})$$

Department of EECS

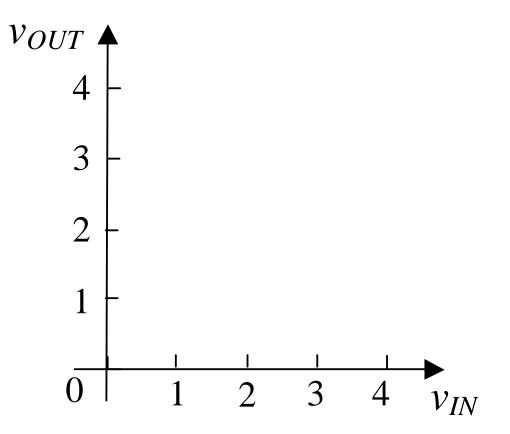

### **Voltage Transfer Curve**

Open-circuit voltage gain:  $A_v = v_{out} / v_{in} = -g_{m1}R_{out}$

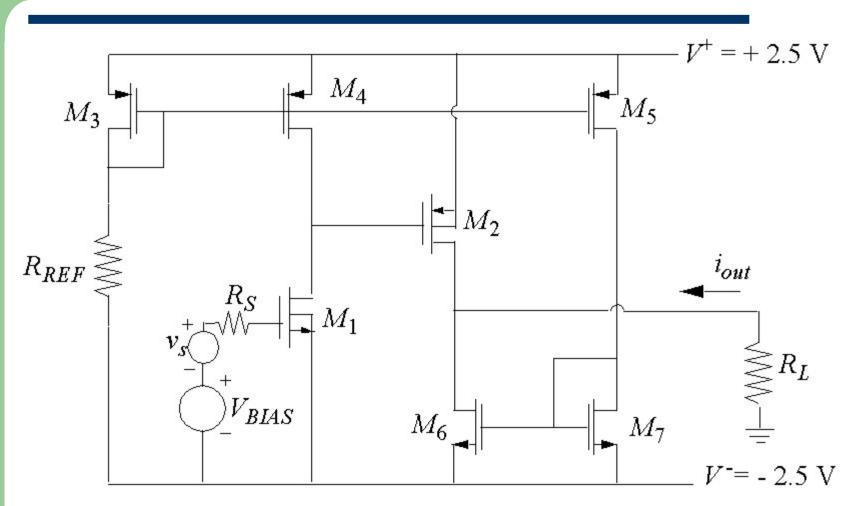

### **Two-Stage Amplifier Topology**

Direct DC connection: use NMOS then PMOS

# **Current Supply Design**

Assume that the reference is a "sink" set by a resistor

Must mirror the reference current and generate a sink for  $i_{SUP 2}$

### **Use Basic Current Supplies**

### **Complete Amplifier Topology**

What's missing? The device dimensions and the bias voltage and reference resistor