#### **Lecture 15**

#### **OUTLINE**

- MOSFET structure & operation (qualitative)

- Review of electrostatics

- The (N)MOS capacitor

- Electrostatics

- Charge vs. voltage characteristic

- Reading: Chapter 6.1-6.2.1

EE105 Spring 2008

Lecture 15, Slide 1

Prof. Wu, UC Berkeley

#### The MOSFET

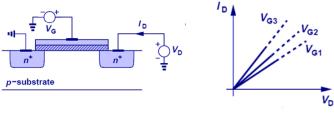

- Current flowing through the channel between the source and drain is controlled by the gate voltage.

- "N-channel" & "P-channel" MOSFETs operate in a complementary manner "CMOS" = Complementary MOS

CURREN | PART | CURREN | PART | PART

EE105 Spring 2008

Lecture 15, Slide 2

Prof. Wu, UC Berkeley

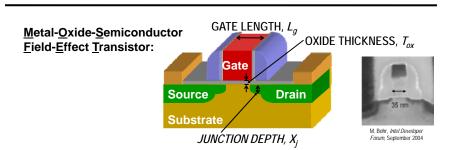

#### **N-Channel MOSFET Structure**

- The conventional gate material is heavily doped polycrystalline silicon (referred to as "polysilicon" or "poly-Si" or "poly")

- Note that the gate is usually doped the same type as the source/drain,

i.e. the gate and the substrate are of opposite types.

- The conventional gate insulator material is SiO<sub>2</sub>.

- To minimize current flow between the substrate (or "body") and the source/drain regions, the p-type substrate is grounded.

EE105 Spring 2008 Lecture 15, Slide 3 Prof. Wu, UC Berkeley

### **Review: Charge in a Semiconductor**

- Negative charges:

- Conduction electrons (density = n)

- Ionized acceptor atoms (density =  $N_{\Delta}$ )

- Positive charges:

- Holes (density = p)

- Ionized donor atoms (density =  $N_D$ )

- The net charge density [C/cm³] in a semiconductor is

$$\rho = q(p - n + N_D - N_A)$$

- Note that p, n,  $N_D$ , and  $N_A$  each can vary with position.

- The mobile carrier concentrations (n and p) in the channel of a MOSFET can be modulated by an electric field via V<sub>G</sub>.

EE105 Spring 2008 Lecture 15, Slide 4 Prof. Wu, UC Berkeley

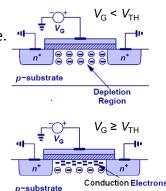

## **Channel Formation (Qualitative)**

- As the gate voltage  $(V_G)$  is increased, holes are repelled away from the substrate surface.

- The surface is depleted of mobile carriers. The charge density within the *depletion region* is determined by the dopant ion density.

- As V<sub>G</sub> increases above the threshold voltage V<sub>TH</sub>, a layer of conduction electrons forms at the substrate surface.

- For  $V_G > V_{TH}$ ,  $n > N_A$  at the surface.

- → The surface region is "inverted" to be n-type.

The electron *inversion layer* serves as a resistive path (*channel*) for current to flow between the heavily doped (*i.e.* highly conductive) *source* and *drain* regions.

EE105 Spring 2008

Lecture 15, Slide 5

Prof. Wu, UC Berkeley

### **Voltage-Dependent Resistor**

In the ON state, the MOSFET channel can be viewed as a resistor.

Since the mobile charge density within the channel depends on the gate voltage, the channel resistance is voltage-dependent.

EE105 Spring 2008

Lecture 15, Slide 6

Prof. Wu, UC Berkeley

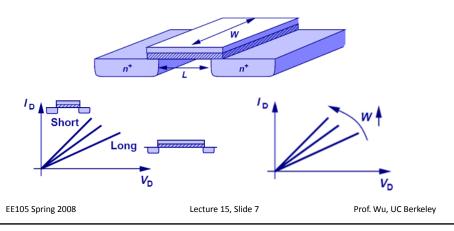

### **Channel Length & Width Dependence**

- Shorter channel length and wider channel width each yield lower channel resistance, hence larger drain current.

- Increasing W also increases the gate capacitance, however, which limits circuit operating speed (frequency).

### Comparison: BJT vs. MOSFET

- In a BJT, current (I<sub>C</sub>) is limited by <u>diffusion</u> of carriers from the emitter to the collector.

- $I_{\rm C}$  increases exponentially with input voltage ( $V_{\rm BE}$ ), because the carrier concentration gradient in the base is proportional to  $e^{V_{\rm BE}/V_T}$

- In a MOSFET, current (ID) is limited by <u>drift</u> of carriers from the source to the drain.

- $I_D$  increases ~linearly with input voltage ( $V_G$ ), because the **carrier** concentration in the channel is proportional to ( $V_G$ - $V_{TH}$ )

In order to understand how MOSFET design parameters affect MOSFET performance, we first need to understand how a MOS capacitor works...

EE105 Spring 2008 Lecture 15, Slide 8 Prof. Wu, UC Berkeley

EE105 Fall 2007 4

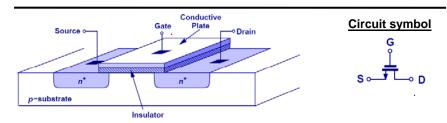

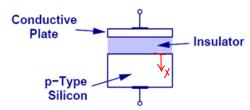

### **MOS Capacitor**

A metal-oxide-semiconductor structure can be considered as a parallel-plate capacitor, with the top plate being the positive plate, the gate insulator being the dielectric, and the p-type semiconductor substrate being the negative plate.

• The negative charges in the semiconductor (for  $V_{\rm G} > 0$ ) are comprised of conduction electrons and/or acceptor ions.

In order to understand how the potential and charge distributions within the Si depend on  $V_{\rm G}$ , we need to be familiar with electrostatics...

EE105 Spring 2008

Lecture 15, Slide 9

Prof. Wu, UC Berkeley

#### Gauss' Law

$$\nabla \cdot E = \frac{\rho}{\varepsilon}$$

ho is the net charge density ho is the dielectric permittivity

- → If the magnitude of electric field changes, there must be charge!

- In a charge-free region, the electric field must be constant.

- Gauss' Law equivalently says that if there is a net electric field leaving a region, there must be positive charge in that region:

$$\oint_{V} \nabla \cdot E \, dV = \iint_{V} \frac{\rho}{\varepsilon} \, dV$$

$$\oint_{V} \nabla \cdot E \, dV = \oint_{S} E \cdot dS$$

$$\oint_{V} \frac{\rho}{\varepsilon} \, dV = \underbrace{\oint_{V} \rho}_{\varepsilon} \, dV = \underbrace{\oint_{V} \rho}_{\varepsilon} \, dV$$

$\oint E \cdot dS = \frac{Q}{\varepsilon}$

The integral of the electric field over a closed surface is proportional to the charge within the enclosed volume

EE105 Spring 2008

Lecture 15, Slide 10

Prof. Wu, UC Berkeley

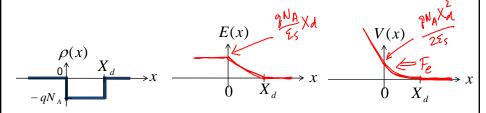

### Gauss' Law in 1-D

$$\nabla \cdot E = \frac{dE}{dx} = \frac{\rho}{\varepsilon}$$

$$dE = \frac{\rho}{\varepsilon} dx$$

$$E(x) = E(x_0) + \int_{x_0}^{x} \frac{\rho(x')}{\varepsilon} dx'$$

• Consider a pulse charge distribution:

EE105 Spring 2008

Lecture 15, Slide 11

Prof. Wu, UC Berkeley

#### **Electrostatic Potential**

• The electric field (force) is related to the potential (energy):

$$E = -\frac{dV}{dx}$$

$\Rightarrow$   $\frac{d^2V(x)}{dx^2} = -\frac{\rho(x)}{\varepsilon}$

Note that an electron (-q charge) drifts in the direction of increasing potential:

$$F_e = -qE = -q\frac{dV}{dx}$$

EE105 Spring 2008

Lecture 15, Slide 12

Prof. Wu, UC Berkeley

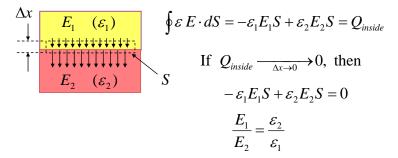

### **Boundary Conditions**

- Electrostatic potential must be a continuous function. Otherwise, the electric field (force) would be infinite.

- Electric field does not have to be continuous, however.

Consider an interface between two materials:

Discontinuity in electric displacement  $\varepsilon E \rightarrow$  charge density at interface!

EE105 Spring 2008

Lecture 15, Slide 13

Prof. Wu. UC Berkelev

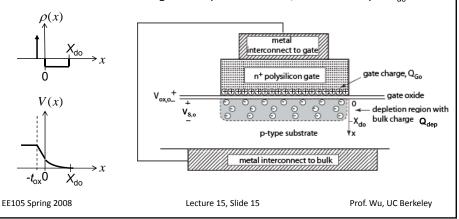

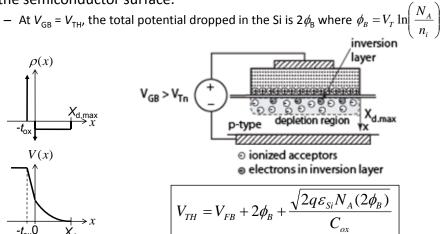

### **MOS Capacitor Electrostatics**

- Gate electrode:

- Since E(x) = 0 in a metallic material, V(x) is constant.

- Gate-electrode/gate-insulator interface:

- The gate charge is located at this interface.

- $\rightarrow E(x)$  changes to a non-zero value inside the gate insulator.

- Gate insulator:

- Ideally, there are no charges within the gate insulator.

- $\rightarrow E(x)$  is constant, and V(x) is linear.

- Gate-insulator/semiconductor interface:

- Since the dielectric permittivity of SiO<sub>2</sub> is lower than that of Si, E(x) is larger in the gate insulator than in the Si.

- Semiconductor:

- If  $\rho(x)$  is constant (non-zero), then V(x) is quadratic.

EE105 Spring 2008 Lecture 15, Slide 14 Prof. Wu, UC Berkeley

EE105 Fall 2007 7

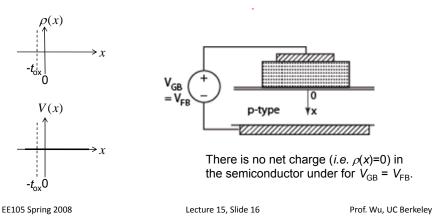

## MOS Capacitor: $V_{GB} = 0$

- If the gate and substrate materials are not the same (typically the case), there is a built-in potential ( $^{\sim}1V$  across the gate insulator).

- Positive charge is located at the gate interface, and negative charge in the Si.

- The substrate surface region is depleted of holes, down to a depth  $X_{do}$

# Flatband Voltage, $V_{\rm FB}$

The built-in potential can be "cancelled out" by applying a gate voltage that is equal in magnitude (but of the opposite polarity) as the built-in potential. This gate voltage is called the *flatband* voltage because the resulting potential profile is flat.

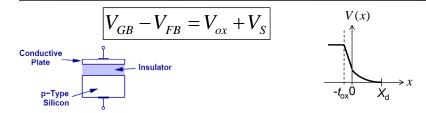

### **Voltage Drops across a MOS Capacitor**

• If we know the total charge within the semiconductor  $(Q'_s)$ , we can find the electric field within the gate insulator  $(E_{ox})$  and hence the voltage drop across the gate insulator  $(V_{ox})$ :

$$\oint E \cdot dS = E_{ox} A = \frac{-Q_S'}{\varepsilon_{ox}} \qquad V_{ox} = E_{ox} t_{ox} = \left(\frac{-Q_S'}{A \varepsilon_{ox}}\right) t_{ox} = \frac{-Q_S}{C_{ox}}$$

where  $Q_{\rm S}$  is the areal charge density in the semiconductor [C/cm²] and  $C_{ox} \equiv \varepsilon_{ox}/t_{ox}$  is the areal gate capacitance [F/cm²]

EE105 Spring 2008

Lecture 15, Slide 17

Prof. Wu, UC Berkeley

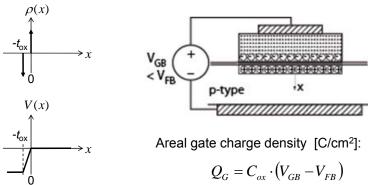

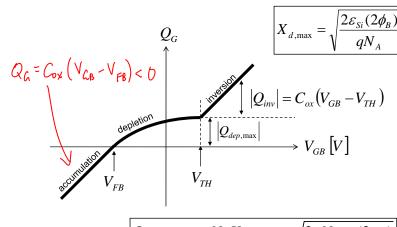

# $V_{GB} < V_{FB}$ (Accumulation)

• If a gate voltage more negative than  $V_{\rm FB}$  is applied, then holes will accumulate at the gate-insulator/semiconductor interface.

EE105 Spring 2008

Lecture 15, Slide 18

Prof. Wu, UC Berkeley

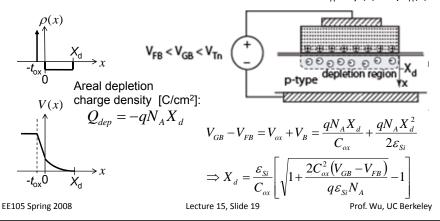

## $V_{\rm FB} < V_{\rm GB} < V_{\rm TH}$ (Depletion)

- If the applied gate voltage is greater than  $V_{\rm FB}$ , then the semiconductor surface will be depleted of holes.

- − If the applied gate voltage is less than  $V_{TH}$ , the concentration of conduction electrons at the surface is smaller than  $N_A \rightarrow \rho(x) \cong -qN_A(x)$

# $V_{\rm GB} > V_{\rm TH}$ (Inversion)

• If the applied gate voltage is greater than  $V_{\rm TH}$ , then  $n > N_{\rm A}$  at the semiconductor surface.

EE105 Fall 2007

Lecture 15, Slide 20

Prof. Wu, UC Berkeley

EE105 Spring 2008

# Maximum Depletion Depth, $X_{d,max}$

- As  $V_{GB}$  is increased above  $V_{TH}$ ,  $V_{S}$  and hence the depth of the depletion region ( $X_{d}$ ) increases very slowly.

- This is because n increases exponentially with  $V_s$ , whereas  $X_d$  increases with the square root of  $V_s$ . Thus, most of the incremental negative charge in the semiconductor comes from additional conduction electrons rather than additional ionized acceptor atoms, when n exceeds  $N_A$ .

- $\rightarrow$   $X_{\rm d}$  can be reasonably approximated to reach a maximum value  $(X_{\rm d,max})$  for  $V_{\rm GB} \ge V_{\rm TH}$ .

- $-~Q_{\rm dep}$  thus reaches a maximum of  $Q_{\rm dep,max}$  at  $V_{\rm GB}$  =  $V_{\rm TH}$ .

- If we assume that only the inversion-layer charge increases with increasing  $V_{\rm GB}$  above  $V_{\rm TH}$ , then

$$Q_{inv} = -C_{ox}(V_{GB} - V_{TH})$$

and so  $Q_G(V_{GB}) = C_{ox}(V_{GB} - V_{TH}) + Q_{dep,max}$

EE105 Spring 2008

Lecture 15, Slide 21

Prof. Wu, UC Berkeley

### **Q-V** Curve for MOS Capacitor

$Q_{dep,\text{max}} = -qN_AX_{d,\text{max}} = -\sqrt{2qN_A\varepsilon_{Si}(2\varphi_B)}$

EE105 Spring 2008

Lecture 15, Slide 22

Prof. Wu, UC Berkeley

EE105 Fall 2007 11