#### **Lecture 17**

#### **OUTLINE**

- NMOSFET in ON state (cont'd)

- Body effect

- Channel-length modulation

- Velocity saturation

- NMOSFET in OFF state

- MOSFET models

- PMOSFET

- Reading: Finish Chap. 6

EE105 Spring 2008

Lecture 17, Slide 1

Prof. Wu, UC Berkeley

# **Body Effect Example**

EE105 Spring 2008

Lecture 17, Slide 2

Prof. Wu, UC Berkeley

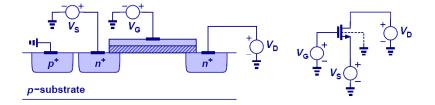

### **Channel-Length Modulation**

- The pinch-off point moves toward the source as  $V_{\rm DS}$  increases.

- ightarrow The length of the inversion-layer channel becomes shorter with increasing  $V_{

m DS}$ .

- ightarrow  $I_{\rm D}$  increases (slightly) with increasing  $V_{\rm DC}$  in the saturation region of operation.

$$I_{D,sat} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 \left[ 1 + \lambda (V_{DS} - V_{D,sat}) \right]$$

$\lambda$ : channel length modulation coefficient

\* Note: in Razavi:  $I_{D,sat} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 [1 + \lambda V_{DS}]$

EE105 Spring 2008

Lecture 17, Slide 3

Prof. Wu, UC Berkeley

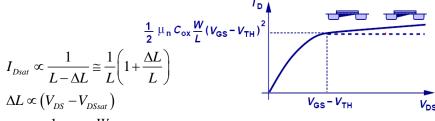

#### $\lambda$ and L

• The effect of channel-length modulation is less for a longchannel MOSFET than for a short-channel MOSFET.

$\lambda \propto \frac{1}{L}$   $\Rightarrow$  short channel MOSFET has larger  $\lambda$

EE105 Spring 2008

Lecture 17, Slide 4

Prof. Wu, UC Berkeley

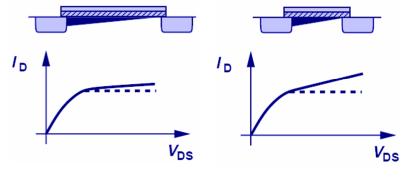

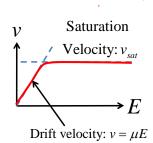

#### **Velocity Saturation**

- In state-of-the-art MOSFETs, the channel is very short (<0.1 $\mu$ m); hence the lateral electric field is very high and carrier drift velocities can reach their saturation levels.

- The electric field magnitude at which the carrier velocity saturates is E<sub>sat</sub>.

$$v_{sat} = \begin{cases} 8 \times 10^6 \text{ cm/s for electrons in Si} \\ 6 \times 10^6 \text{ cm/s for holes in Si} \end{cases}$$

NMOS:

$$\mu_n \approx 250 \text{ cm}^2/\text{V-s} \implies E_{sat} \approx 30,000 \text{ V/cm}$$

PMOS:  $\mu_n \approx 80 \text{ cm}^2/\text{V-s} \implies E_{sat} \approx 80,000 \text{ V/cm}$

For

$$L = 0.1 \,\mu\text{m}$$

$$\begin{cases} V_{D,sat} = 0.3 \text{ V} & \text{for NMOS} \\ V_{D,sat} = 0.8 \text{ V} & \text{for PMOS} \end{cases}$$

EE105 Spring 2008

Slope =  $\mu$

Lecture 17, Slide 5

Prof. Wu, UC Berkeley

## **Impact of Velocity Saturation**

- Recall that  $I_D = WQ_{inv}(y)v(y)$

- If  $V_{DS} > E_{sat} \times L$ , the carrier velocity will saturate and hence the drain current will saturate:

$$I_{D,sat} = WQ_{inv}v_{sat} = WC_{ox}(V_{GS} - V_{TH})v_{sat}$$

- $I_{\rm D,sat}$  is proportional to  $V_{\rm GS} V_{\rm TH}$  rather than  $(V_{\rm GS} V_{\rm TH})^2$

- I<sub>D.sat</sub> is not dependent on L

- I<sub>D.sat</sub> is dependent on W

EE105 Spring 2008

Lecture 17, Slide 6

Prof. Wu, UC Berkeley

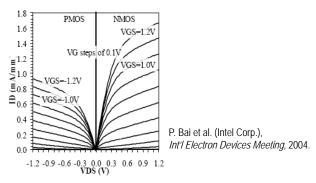

# Short-Channel MOSFET $I_D$ - $V_{DS}$

$I_{\text{DS}}\text{-}V_{\text{DS}}$  for 35nm gate lengths

- $I_{D,sat}$  is proportional to  $V_{GS}$ - $V_{TH}$  rather than  $(V_{GS}$ - $V_{TH})^2$

- $V_{D.sat}$  is smaller than  $V_{GS}$ - $V_{TH}$

- Channel-length modulation is apparent (?)

EE105 Spring 2008 Lecture 17, Slide 7 Prof. Wu, UC Berkeley

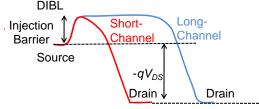

# **Drain Induced Barrier Lowering (DIBL)**

- In a short-channel MOSFET, the source & drain regions each "support" a significant fraction of the total channel depletion charge Q<sub>dep</sub>×W×L

- $\rightarrow V_{\text{TH}}$  is lower than for a long-channel MOSFET

- As the drain voltage increases, the reverse bias on the body-drain PN junction increases, and hence the drain depletion region widens.

- $\rightarrow V_{\text{TH}}$  decreases with increasing drain bias.

(The barrier to carrier diffusion from the source into the channel is reduced.)

$\rightarrow$   $I_{\rm D}$  increases with increasing drain bias.

EE105 Spring 2008 Lecture 17, Slide 8 Prof. Wu, UC Berkeley

EE105 Fall 2007 4

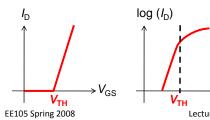

#### **NMOSFET in OFF State**

- We had previously assumed that there is no channel current when  $V_{\rm GS} < V_{\rm TH}$ . This is incorrect!

- As V<sub>GS</sub> is reduced below V<sub>TH</sub> (towards 0 V), the potential barrier to carrier diffusion from the source into the channel is increased.

I<sub>D</sub> becomes limited by carrier diffusion into the channel, rather than by carrier drift through the channel.

(This is similar to the case of a PN junction diode!)

$\rightarrow I_D$  varies exponentially with the potential barrier height at the source, which varies directly with the channel potential.

EE105 Spring 2008

Lecture 17, Slide 9

Prof. Wu, UC Berkeley

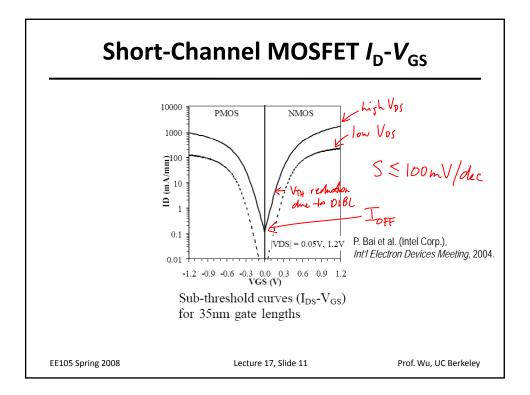

### **Sub-Threshold Leakage Current**

• Recall that, in the depletion (sub-threshold) region of operation, the channel potential is capacitively coupled to the gate potential. A change in gate voltage ( $\Delta V_{\rm GS}$ ) results in a change in channel voltage ( $\Delta V_{\rm CS}$ ):

$$\Delta V_{CS} = \Delta V_{GS} \times \left( \frac{C_{ox}}{C_{ox} + C_{dep}} \right) \equiv \Delta V_{GS} / m \quad ; \quad m = 1 + \frac{C_{dep}}{C_{ox}} > 1$$

• Therefore, the sub-threshold current  $(I_{D,subth})$  decreases exponentially with linearly decreasing  $V_{GS}/m$

Sub-threshold swing:

$$S \equiv \left(\frac{d(\log_{10} I_{DS})}{dV_{GS}}\right)^{-1}$$

$S = mV_T \ln(10) > 60 \text{mV/dec}$

Prof. Wu, UC Berkeley

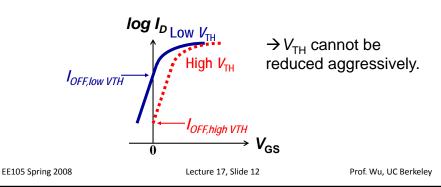

# **V**<sub>TH</sub> Design Trade-Off

• Low  $V_{\text{TH}}$  is desirable for high ON-state current:

$$I_{\text{D.sat}} \propto (V_{\text{DD}} - V_{\text{TH}})^{\eta}$$

1 <  $\eta$  < 2

• But high  $V_{TH}$  is needed for low OFF-state current:

EE105 Fall 2007 6

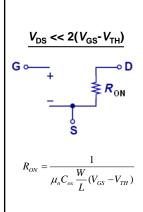

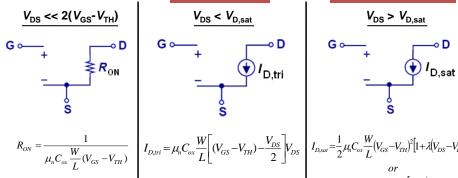

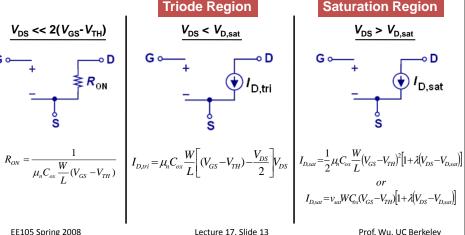

# **MOSFET Large-Signal Models** $(V_{GS} > V_{TH})$

Depending on the value of  $V_{DS}$ , the MOSFET can be represented with different large-signal models.

#### MOSFET Transconductance, $g_m$

Transconductance  $(g_m)$  is a measure of how much the drain current changes when the gate voltage changes.

$$g_m \equiv \frac{\partial I_D}{\partial V_{GS}}$$

- For amplifier applications, the MOSFET is usually operating in the saturation region.

- For a long-channel MOSFET:

$$g_{m} = \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) \{ 1 + \lambda (V_{DS} - V_{D,sat}) \} = \frac{2I_{D}}{V_{GS} - V_{TH}}$$

For a short-channel MOSFET:

$$g_{m} = v_{sat}WC_{ox}\left\{1 + \lambda\left(V_{DS} - V_{D,sat}\right)\right\} = \frac{I_{D}}{V_{GS} - V_{TH}}$$

EE105 Spring 2008

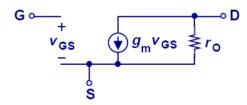

### **MOSFET Small-Signal Model**

(Saturation Region of Operation)

• The effect of channel-length modulation or DIBL (which cause  $I_{\rm D}$  to increase linearly with  $V_{\rm DS}$ ) is modeled by the transistor output resistance,  $r_{\rm o}$ .

$$r_o \equiv \frac{\partial V_{DS}}{\partial I_D} \approx \frac{1}{\lambda I_D}$$

EE105 Spring 2008

Lecture 17. Slide 15

Prof. Wu, UC Berkeley

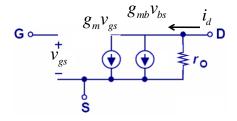

#### **Derivation of Small-Signal Model**

(Long-Channel MOSFET, Saturation Region)

$$\begin{split} I_D &= \frac{1}{2} \mu_n C_{ox} \frac{W}{L} \left( V_{GS} - V_{TH} \right)^2 \left[ 1 + \lambda \left( V_{DS} - V_{D,sat} \right) \right] \\ i_d &= \frac{\partial I_D}{\partial V_{GS}} v_{gs} + \frac{\partial I_D}{\partial V_{BS}} v_{bs} + \frac{\partial I_D}{\partial V_{DS}} v_{ds} \equiv g_m v_{gs} + g_{mb} v_{bs} + \frac{1}{r_o} v_{ds} \end{split}$$

EE105 Spring 2008

Lecture 17, Slide 16

Prof. Wu, UC Berkeley

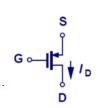

#### **PMOS Transistor**

A p-channel MOSFET behaves similarly to an n-channel MOSFET, except the polarities for I<sub>D</sub> and V<sub>GS</sub> are reversed.

Circuit symbol

- The small-signal model for a PMOSFET is the same as that for an NMOSFET.

- The values of  $g_{\rm m}$  and  $r_{\rm o}$  will be different for a PMOSFET vs. an NMOSFET, since mobility & saturation velocity are different for holes vs. electrons.

EE105 Spring 2008

Lecture 17, Slide 17

Prof. Wu, UC Berkeley

# PMOS I-V Equations

$$I_{D,tri} = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} \Big[ 2 \big( V_{SG} - V_{TH} \big) V_{DS} - V_{DS}^2 \Big] \qquad _{DS \leftrightarrow SD} \ G$$

$$= \frac{1}{2} \mu_p C_{ox} \frac{W}{L} \Big[ 2 \big( |V_{GS}| - |V_{TH}| \big) |V_{DS}| - V_{DS}^2 \Big]$$

Long Channel

$$\begin{split} I_{D,sat} &= \frac{1}{2} \, \mu_p C_{ox} \, \frac{W}{L} \big( V_{SG} - V_{TH} \big)^2 \Big[ 1 + \lambda \big( V_{SD} - V_{SD,sat} \big) \Big] \\ &= \frac{1}{2} \, \mu_p C_{ox} \, \frac{W}{L} \big( \big| V_{GS} \big| - \big| V_{TH} \big| \big)^2 \Big[ 1 + \lambda \big( \big| V_{DS} \big| - \big| V_{D,sat} \big| \big) \Big] \end{split}$$

Short Channel:

$$\begin{split} I_{D,sat} &= v_{sat} W C_{ox} (V_{SG} - V_{TH}) \Big[ 1 + \lambda \left( V_{SD} - V_{SD,sat} \right) \Big] \\ &= v_{sat} W C_{ox} (\left| V_{SG} \right| - \left| V_{TH} \right|) \Big[ 1 + \lambda \left( \left| V_{DS} \right| - \left| V_{D,sat} \right| \right) \Big] \end{split}$$

Note:  $V_{GS} < 0, V_{DS} < 0, V_{D,sat} < 0, V_{TH} < 0$  in PMOS

EE105 Spring 2008

Lecture 17, Slide 18

Prof. Wu, UC Berkeley

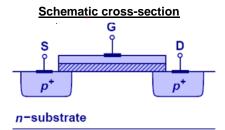

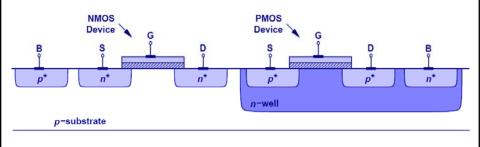

# **CMOS Technology**

- It possible to form deep n-type regions ("well") within a p-type substrate to allow PMOSFETs and NMOSFETs to be co-fabricated on a single substrate.

- This is referred to as CMOS ("Complementary MOS") technology.

#### **Schematic cross-section of CMOS devices**

EE105 Spring 2008 Lecture 17, Slide 19 Prof. Wu, UC Berkeley

### **Comparison of BJT and MOSFET**

$\bullet~$  The BJT can achieve much higher  $g_{\rm m}$  than a MOSFET, for a given bias current, due to its exponential I-V characteristic.

#### (Long-Channel)

#### (Short-Channel)

| Bipolar Transistor                                                                                                                                | MOSFET                                                                                                                                                                                  | MOSFET                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Exponential Characteristic  Active: V <sub>CB</sub> > 0  Saturation: V <sub>CB</sub> < 0  Finite Base Current  Early Effect  Diffusion Current  - | Quadratic Characteristic Saturation: $V_{DS} > V_{GS} - V_{TH}$ Triode: $V_{DS} < V_{GS} - V_{TH}$ Zero Gate Current Channel-Length Modulation Drift Current Voltage-Dependent Resistor | $\begin{array}{c} \hline \\ \text{Linear} \\ V_{GS} > V_{Dsat} \\ V_{GS} < V_{Dsat} \end{array};  V_{Dsat} \\ \end{array}$ |

# $V_{Dsat}$ ; $V_{Dsat} = E_{sat}L$

EE105 Spring 2008 Lecture 17, Slide 20 Prof. Wu, UC Berkeley