#### **Lecture 18**

#### **OUTLINE**

- Basic MOSFET amplifier

- MOSFET biasing

- MOSFET current sources

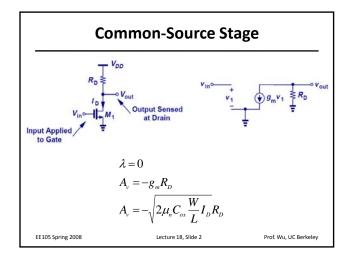

- Common-source amplifier

- Reading: Chap. 7.1-7.2

EE105 Spring 2008

Lecture 18, Slide

Prof. Wu, UC Berkeley

## **Operation in Saturation**

$$V_{DD}$$

$$R_{D} \ge 1 \text{ k}\Omega$$

$$V_{out} > V_{in} - V_{in}$$

$$W_{1} \frac{W}{L} = \frac{10}{0.18}$$

Condition for M<sub>1</sub> in saturation

$$V_{out} > V_{in} - V_{TH}$$

$$\Rightarrow V_{DD} - R_{D}I_{D} > (V_{CS} - V_{TH})$$

- In order to maintain operation in saturation, V<sub>out</sub> cannot fall below V<sub>in</sub> by more than one threshold voltage.

- The condition above ensures operation in saturation.

EE105 Spring 2008 Lecture 18, Slide 3 Prof. Wu, UC Berkel

# CS Stage with $\lambda$ =0 $A_{v} = -g_{m}R_{L}$ $R_{in} = \infty$ $R_{out} = R_{L}$ EE105 Spring 2008 Lecture 18, Slide 4 Prof. Wu, UC Berkeley

EE105 Fall 2007

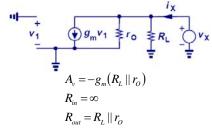

#### CS Stage with $\lambda \neq 0$

• However, channel length modulation leads to finite output resistance,  $r_{o}$ , which is in parallel with the load resistance, R<sub>L</sub>

EE105 Spring 2008

Lecture 18, Slide 5

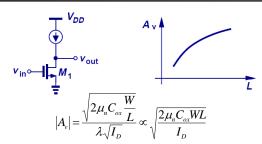

#### **CS Gain Variation with Channel Length**

• Since  $\lambda$  is inversely proportional to L, the intrinsic voltage gain actually becomes proportional to the square root of L. EE105 Spring 2008

Lecture 18, Slide 6

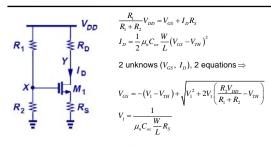

#### **MOS Biasing**

- Voltage at X is determined by  $V_{\rm DD}$ ,  $R_{\rm 1}$ , and  $R_{\rm 2}$ .

- V<sub>GS</sub> can be found using the equation above, and I<sub>D</sub> can be found by using the NMOS current equation.

EE105 Spring 2008 Lecture 18, Slide 7 Prof. Wu, UC Berkeley

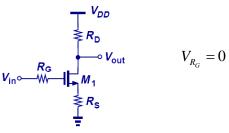

# **Self-Biased MOS Stage**

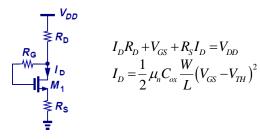

• The circuit above is analyzed by noting M<sub>1</sub> is in saturation and no potential drop appears across RG.

EE105 Spring 2008 Lecture 18, Slide 8 Prof. Wu, UC Berkeley

EE105 Fall 2007 2

#### **Current Sources**

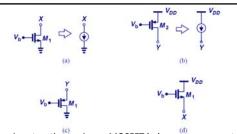

- When in saturation region, a MOSFET behaves as a current source.

- NMOS draws current from a point to ground (sinks current), whereas PMOS draws current from V<sub>DD</sub> to a point (sources current).

EE105 Spring 2008 Lecture 18, Slide 9 Prof. Wu, UC Berkeley

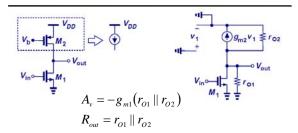

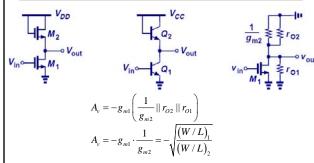

#### **CS Stage with Current-Source Load**

- To alleviate the headroom problem, an active current-source load is used.

- This is advantageous because a current-source has a high output resistance and can tolerate a small voltage drop across it.

EE105 Spring 2008

Lecture 18, Slide 10

Prof. Wu, UC Berkeley

Output

Prof. Wu, UC Berkeley

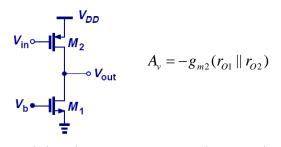

### PMOS CS Stage with NMOS as Load

• Similarly, with PMOS as input stage and NMOS as the load, the voltage gain is the same as before.

EE105 Spring 2008 Lecture 18, Slide 11 Prof. Wu, UC Berkeley

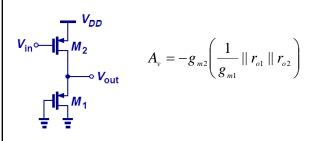

# **CS Stage with Diode-Connected Load**

• Lower gain, but less dependent on process parameters.

EE105 Spring 2008 Lecture 18, Slide 12 Prof. Wu, UC Berkeley

EE105 Fall 2007 3

#### **CS Stage with Diode-Connected PMOS Device**

• Note that PMOS circuit symbol is usually drawn with the source on top of the drain.

EE105 Spring 2008 Lecture 18, Slide 13 Prof. Wu, UC Berkeley

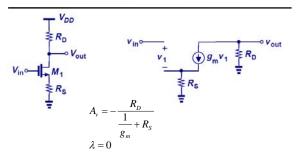

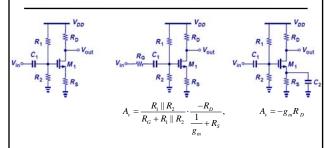

#### **CS Stage with Degeneration**

Similar to bipolar counterpart, when a CS stage is degenerated, its gain, I/O impedances, and linearity change.

EE105 Spring 2008 Lecture 18, Slide 14 Prof. Wu, UC Berkeley

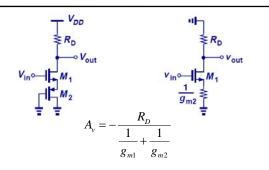

#### **Example of CS Stage with Degeneration**

• A diode-connected device degenerates a CS stage.

EE105 Spring 2008 Lecture 18, Slide 15 Prof. Wu, UC Berkeley

# **CS Stage with Gate Resistance**

Since at low frequencies, the gate conducts no current, gate resistance does not affect the gain or I/O impedances.

105 Spring 2008 Lecture 18, Slide 16 Prof. Wu, UC Berkeley

EE105 Fall 2007 4

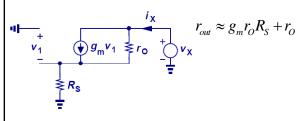

# Output Impedance of CS Stage with Degeneration

• Similar to the bipolar counterpart, degeneration boosts output impedance.

EE105 Spring 2008 Lecture 18, Slide 17 Prof. Wu, UC Berkeley

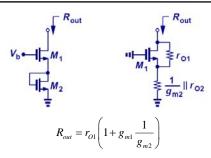

#### **Output Impedance Example (I)**

• When  $1/g_m$  is parallel with  $r_{O2}$ , we often just consider  $1/g_m$

EE105 Spring 2008 Lecture 18, Slide 18 Prof. Wu, UC Berkeley

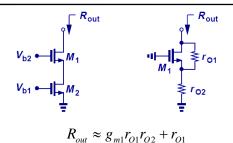

# **Output Impedance Example (II)**

• In this example, the impedance that degenerates the CS stage is  $r_0$ , instead of  $1/g_m$  in the previous example.

EE105 Spring 2008 Lecture 18, Slide 19 Prof. Wu, UC Berkeley

# **CS Core with Biasing**

Degeneration is used to stabilize bias point, and a bypass capacitor can be used to obtain a larger small-signal voltage gain at the frequency of interest.

EE105 Spring 2008 Lecture 18, Slide 20 Prof. Wu, UC Berkeley

EE105 Fall 2007 5