#### Lecture 7

#### **OUTLINE**

- Bipolar Amplifier Topologies (1)

- Common-Emitter Amplifiers

Reading: Chapter 5.3.1

## Possible Bipolar Amplifier Topologies

(e)

(d)

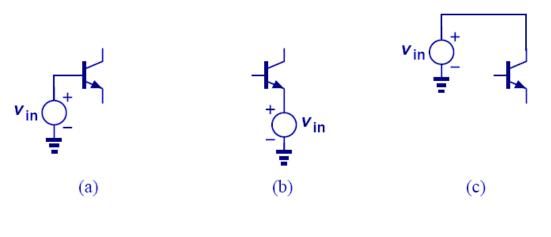

- Three possible ways to apply an input to an amplifier and three possible ways to sense its output.

- However, in reality only three of six input/output combinations are useful.

(f)

$v_{\rm out}$

## **Study of Common-Emitter Topology**

- Analysis of CE Core

- Inclusion of Early Effect

- Emitter Degeneration

- Inclusion of Early Effect

- CE Stage with Biasing

EE105 Spring 2008 Lecture 7, Slide 3 Prof. Wu, UC Berkeley

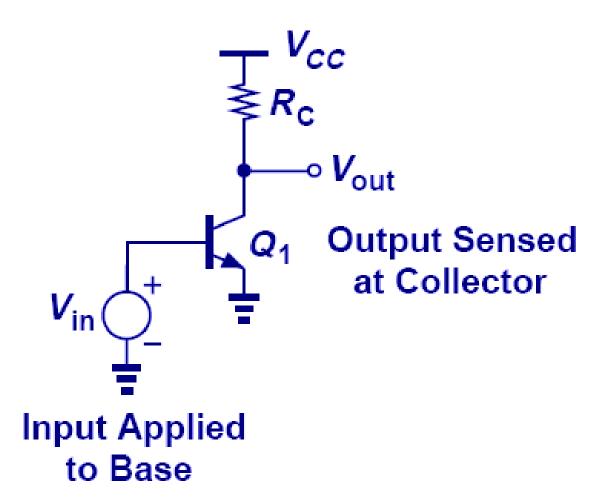

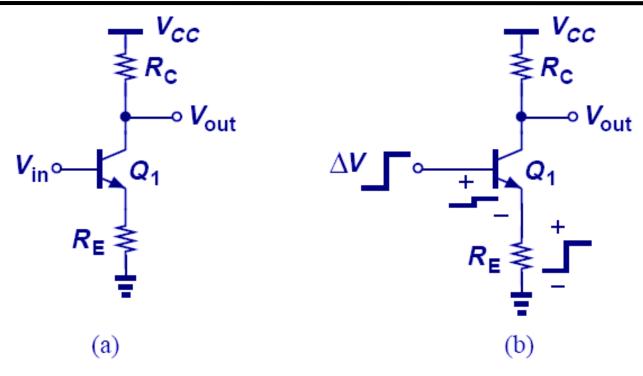

## **Common-Emitter Topology**

## **Small Signal of CE Amplifier**

EE105 Spring 2008 Lecture 7, Slide 5 Prof. Wu, UC Berkeley

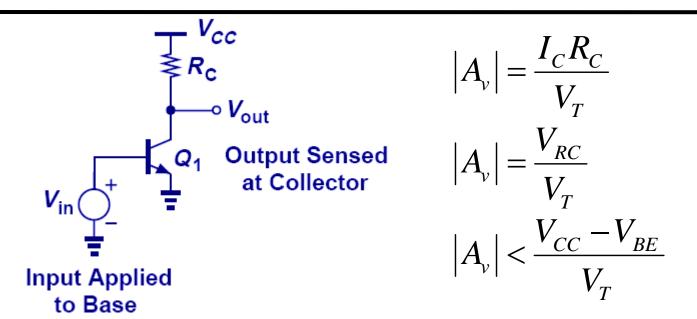

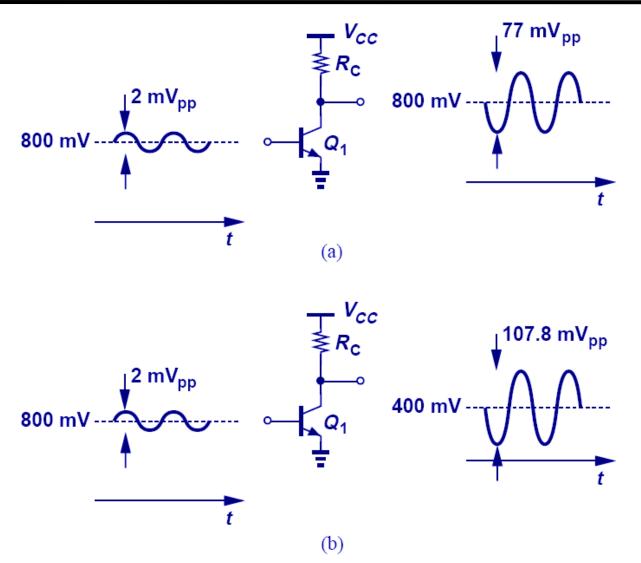

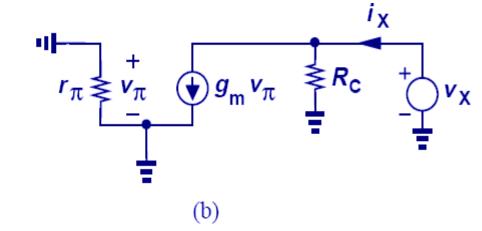

## Limitation on CE Voltage Gain

- Since  $g_m$  can be written as  $I_C/V_T$ , the CE voltage gain can be written as the ratio of  $V_{RC}$  and  $V_T$ .

- $V_{RC}$  is the potential difference between  $V_{CC}$  and  $V_{CE}$ , and  $V_{CE}$  cannot go below  $V_{BE}$  in order for the transistor to be in active region.

#### **Tradeoff between Voltage Gain and Headroom**

EE105 Spring 2008 Lecture 7, Slide 7 Prof. Wu, UC Berkeley

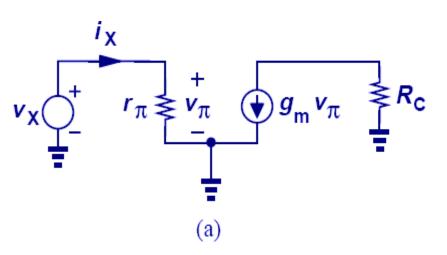

## I/O Impedances of CE Stage

$$R_{in} = \frac{v_X}{i_X} = r_{\pi}$$

$$R_{\scriptscriptstyle out} = rac{v_{\scriptscriptstyle X}}{i_{\scriptscriptstyle X}} = R_{\scriptscriptstyle C}$$

• When measuring output impedance, the input port has to be grounded so that  $V_{in} = 0$ .

EE105 Spring 2008 Lecture 7, Slide 8 Prof. Wu, UC Berkeley

## **CE Stage Trade-offs**

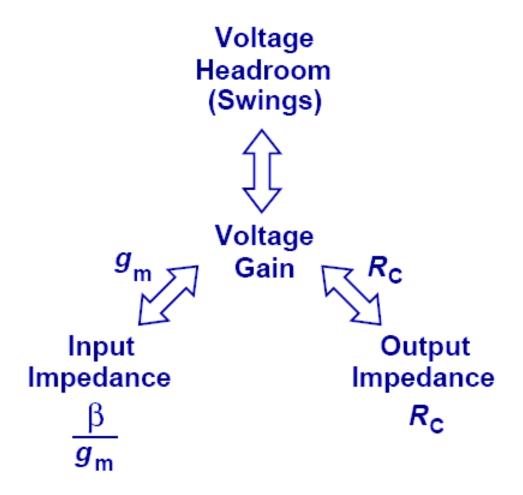

## **Inclusion of Early Effect**

$$A_{v} = -g_{m}(R_{C} \parallel r_{O})$$

$$R_{out} = R_{C} \parallel r_{O}$$

Early effect will lower the gain of the CE amplifier, as it appears in parallel with RC.

EE105 Spring 2008 Lecture 7, Slide 10 Prof. Wu, UC Berkeley

#### **Intrinsic Gain**

$$A_{v} = -g_{m} r_{O}$$

$$|A_{v}| = \frac{V_{A}}{V_{T}}$$

- As R<sub>c</sub> goes to infinity, the voltage gain reaches the product of g<sub>m</sub> and r<sub>o</sub>, which represents the maximum voltage gain the amplifier can have.

- The intrinsic gain is independent of the bias current.

#### **Current Gain**

$$A_{I} = rac{i_{out}}{i_{in}}$$

$A_{I}|_{CE} = eta$

- Another parameter of the amplifier is the current gain, which is defined as the ratio of current delivered to the load to the current flowing into the input.

- For a CE stage, it is equal to  $\beta$ .

## **Emitter Degeneration**

- By inserting a resistor in series with the emitter, we "degenerate" the CE stage.

- This topology will decrease the gain of the amplifier but improve other aspects, such as linearity, and input impedance.

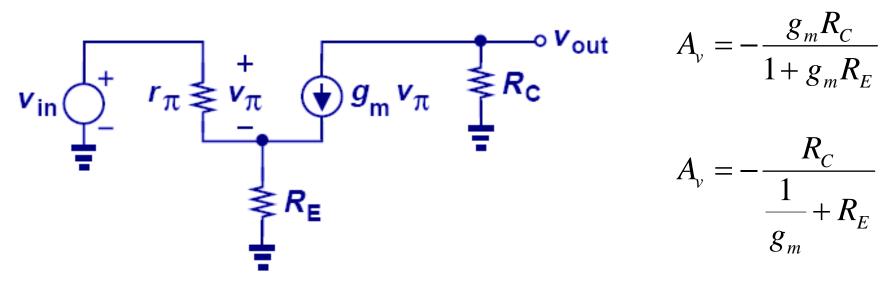

## **Small-Signal Model**

Interestingly, this gain is equal to the total load resistance to ground divided by 1/g<sub>m</sub> plus the total resistance placed in series with the emitter.

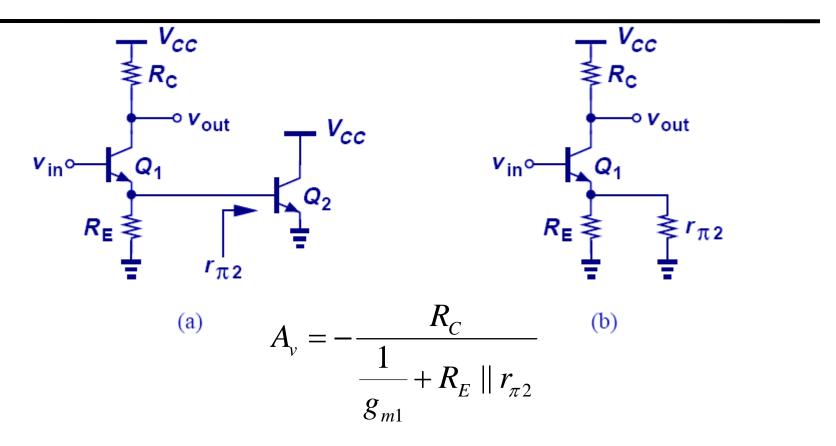

## **Emitter Degeneration Example I**

• The input impedance of  $Q_2$  can be combined in parallel with  $R_E$  to yield an equivalent impedance that degenerates  $Q_1$ .

EE105 Spring 2008 Lecture 7, Slide 15 Prof. Wu, UC Berkeley

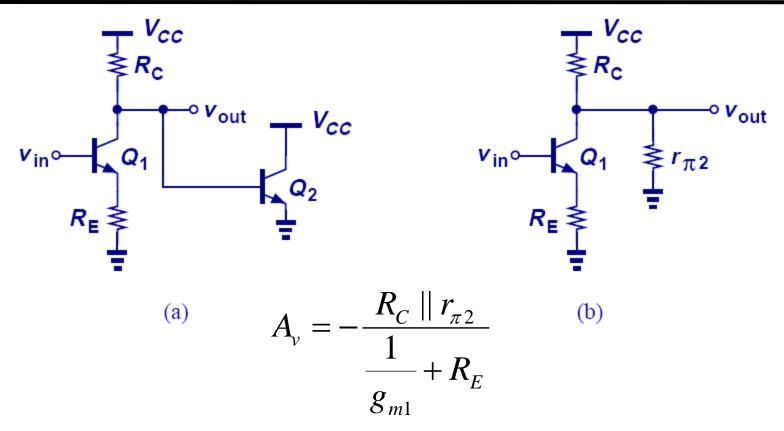

## **Emitter Degeneration Example II**

• In this example, the input impedance of  $Q_2$  can be combined in parallel with  $R_C$  to yield an equivalent collector impedance to ground.

EE105 Spring 2008 Lecture 7, Slide 16 Prof. Wu, UC Berkeley

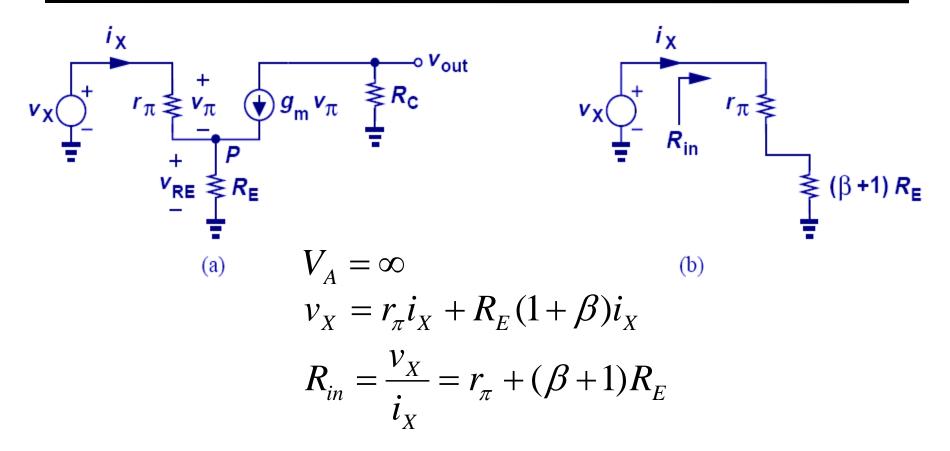

### Input Impedance of Degenerated CE Stage

• With emitter degeneration, the input impedance is increased from  $r_{\pi}$  to  $r_{\pi}$  + ( $\beta$ +1) $R_{E}$ ; a desirable effect.

EE105 Spring 2008 Lecture 7, Slide 17 Prof. Wu, UC Berkeley

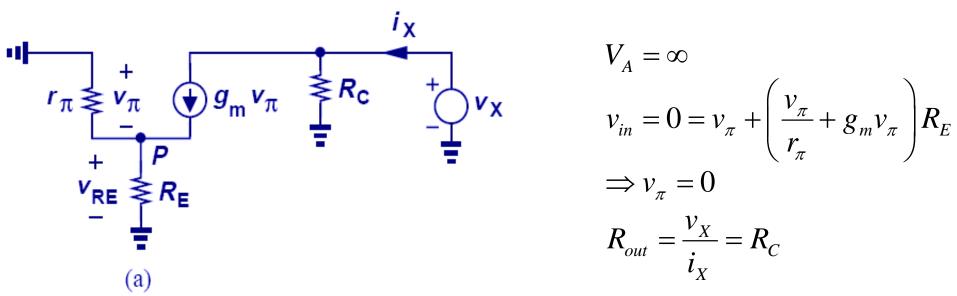

# Output Impedance of Degenerated CE Stage without Considering Early Effect

• Emitter degeneration does not alter the output impedance in this case. (More on this later.)

EE105 Spring 2008 Lecture 7, Slide 18 Prof. Wu, UC Berkeley

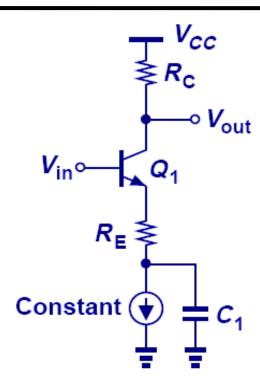

## **Capacitor at Emitter**

- At DC the capacitor is open and the current source biases the amplifier.

- For ac signals, the capacitor is short and the amplifier is degenerated by RE.

EE105 Spring 2008 Lecture 7, Slide 19 Prof. Wu, UC Berkeley

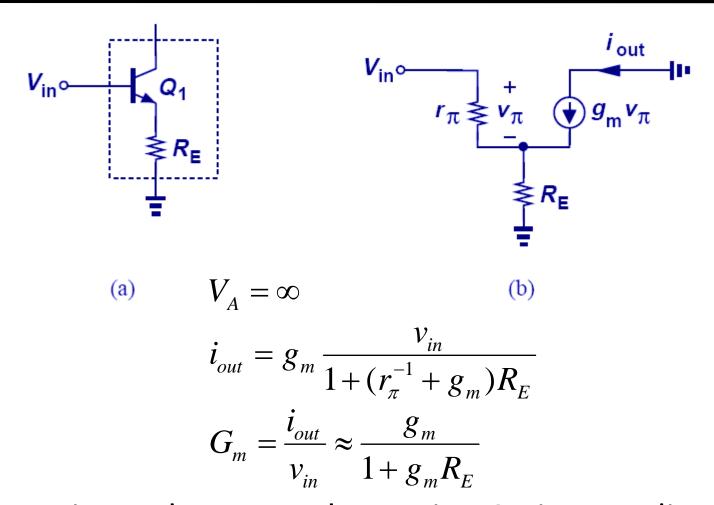

## Example: Design CE Stage with Degeneration as a Black Box

• If  $g_m R_E$  is much greater than unity,  $G_m$  is more linear.

EE105 Spring 2008 Lecture 7, Slide 20 Prof. Wu, UC Berkeley