### UNIVERSITY OF CALIFORNIA, BERKELEY

# College of Engineering Department of Electrical Engineering and Computer Sciences Fall 2015

EE 105: Microelectronic Devices and Circuits

Prof. Ming Wu

## **MIDTERM EXAMINATION #2**

Time allotted: 80 minutes

| NAME:   |      |       |           |

|---------|------|-------|-----------|

| (print) | Last | First | Signature |

| STUDENT | ID#: |       |           |

#### **INSTRUCTIONS:**

- 1. SHOW YOUR WORK. (Make your methods clear to the grader!)

- 2. Clearly mark (underline or box) your answers.

- 3. Specify the units of your answer to receive full credit.

- 4. Unless stated in the problem, use the values of physical constants provided below.

- 5. You can use approximations within 10% accuracy any time.

| Commonly used constants and physical parameters: |                    |                                       |  |  |  |

|--------------------------------------------------|--------------------|---------------------------------------|--|--|--|

| Electronic charge                                | q                  | 1.6×10 <sup>-19</sup> C               |  |  |  |

| Boltzmann's constant                             | k                  | 8.62×10 <sup>-5</sup> eV/K            |  |  |  |

| Thermal voltage at 300K                          | $V_{\rm T} = kT/q$ | 0.025 V                               |  |  |  |

| Intrinsic carrier concentration of Si            | $n_i$              | 1.5x10 <sup>10</sup> cm <sup>-3</sup> |  |  |  |

| Relative permittivity of Si                      | $\epsilon_{r,Si}$  | 11.7                                  |  |  |  |

| Relative permittivity of SiO <sub>2</sub>        | $\epsilon_{r,ox}$  | 3.9                                   |  |  |  |

| Vacuum permittivity                              | $\epsilon_0$       | 8.854x10 <sup>-14</sup> F/cm          |  |  |  |

|        | Problem 1 | 15  |  |

|--------|-----------|-----|--|

|        | Problem 2 | 20  |  |

| Points | Problem 3 | 25  |  |

| Pomis  | Problem 4 | 20  |  |

|        | Problem 5 | 20  |  |

|        | Total     | 100 |  |

## **Note:**

Even though all problems have the same points, they have varying degree of difficulty. Make sure you scan through the problems, and work on those you know how to solve first.

1. Answer the following questions concisely. Use the semiconductor parameters in the following Table if needed.

| Electron diffusion coefficient |  | $30 \text{ cm}^2/\text{s}$     |

|--------------------------------|--|--------------------------------|

| Hole diffusion coefficient     |  | $10 \text{ cm}^2/\text{s}$     |

| Electron mobility              |  | $1200 \text{ cm}^2/\text{s-V}$ |

| Hole diffusion coefficient     |  | $400 \text{ cm}^2/\text{s-V}$  |

| Electron diffusion length      |  | 2 μm                           |

| Hole diffusion length          |  | 1 μm                           |

- a. Two NPN BJT's have identical doping levels. The base width of BJT-A is half that of BJT-B. Under the same base-emitter bias voltage, which BJT has higher collector current?

- b. What is the **ratio** of the collector currents in NPN and PNP BJT's if they have identical dimensions and doping concentrations (but opposite doping types)?

- c. What is the **ratio** of the transconductances  $(g_m)$  of NMOS and PMOS if they have identical dimensions, doping concentrations, magnitudes of threshold voltages and gate-to-source bias voltages?

(Continuation of Problem 1 solution)

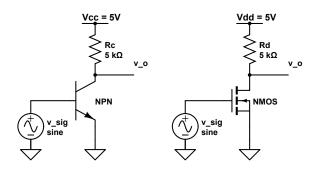

- 2. Consider the two amplifiers shown below (only the AC circuit is shown). The NPN BJT has a current gain of 100, and a  $v_{CE,sat} = 0.3V$ , and the NMOS has  $k_n = 1 \, mA/V^2$  and  $V_{tn} = 1V$ . Ignore Early effects. Assume both transistors are biased at 0.5 mA.

- a. Find the voltage gains of both amplifiers. Which amplifier has higher gain?

- b. Which amplifier (BJT or NMOS) has higher input resistance? What's its value?

- c. What are the output resistances of both amplifiers?

- d. Which amplifier (BJT or NMOS) has large output swing? What's its value? (*Note: output swing is defined as the smaller of the upward and downward voltage swings*)

(Continuation of Problem 2 solution)

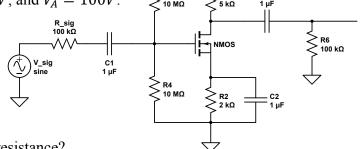

- 3. The NMOS below has  $k_n = 1 \, mA/V^2$ ,  $V_{tn} = 1V$ , and  $V_A = 100V$ .

- a. What is the amplifier configuration?

- b. Find the DC bias current and drain-source voltage. You can assume

V<sub>A</sub> = ∞ for DC analysis.

c. Find the small signal parameters,

- c. Find the small signal parameters,  $g_m$ ,  $r_0$ .

- d. What is the overall gain of the amplifier including the signal resistance and load resistance?

- e. What is the maximum output voltage swing? (Note: output swing is defined as the smaller of the upward and downward voltage swings)

(Continuation of Problem 3 solution)

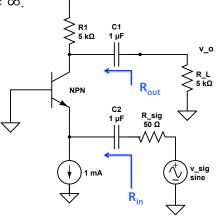

4. The NPN BJT has a current gain of 100. Assume Early voltage  $V_A = \infty$ .

a. What is the amplifier configuration?

- b. What is the input resistance (not including  $R_L$ )?

- c. What is the output resistance,  $R_{out}$  (including  $R_{sig}$ )? d. What is the overall voltage gain, including the signal and load resistance?

- e. What is the overall current gain of the amplifier, i.e., the ratio of the current flowing into R<sub>L</sub> and current from source?

Vcc = 10V

(Continuation of Problem 4 solution)

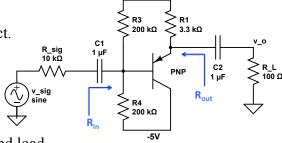

- 5. The PNP BJT has a current gain of 100. Ignore Early effect.

- a. What is the amplifier configuration?

- b. Find the DC bias point (collector current and collector-to-emitter voltage).

- c. What is the input resistance,  $R_{in}$  (not including  $R_{L}$ )?

- d. What is the overall voltage gain including signal and load resistances?

(Continuation of Problem 5 solution)

(Continuation of Problem \_\_\_\_\_ solution)

(Continuation of Problem \_\_\_\_\_ solution)

(Continuation of Problem \_\_\_\_\_ solution)