## PROBLEM SET #1A

Issued: Monday, Oct. 12, 2015

Due (at 8 a.m.): Monday, Nov. 2, 2015, at 8 a.m. in the EE 140/240A HW box near 125 Cory.

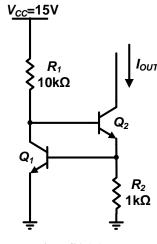

**1.** Determine the value of sensitivity *S* of output current to supply voltage for the circuit in Fig. PSA1.1, where  $S = (V_{CC}/I_{OUT})(\partial I_{OUT}/\partial V_{CC})$ .

Fig. PSA1.1

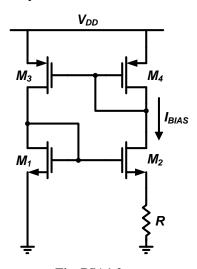

- **2.** For the circuit shown in Fig. PSA1.2, assume that  $X_d = L_d = 0$ ,  $(W/L)_2 > (W/L)_1$ , and  $M_3$  and  $M_4$  are identical.

- (a) Neglecting the body effect, calculate the bias current  $I_{BIAS}$  as a function of R,  $\mu_n C_{ox}$ ,  $(W/L)_I$ , and  $(W/L)_2$ . Comment on how the bias current might vary with temperature.

- (b) Calculate the ratio of small-signal variations in  $I_{BIAS}$  to small signal variations in  $V_{DD}$  at low frequencies. Ignore the body effect but include finite transistor  $r_o$  in this calculation.

Fig. PSA1.2

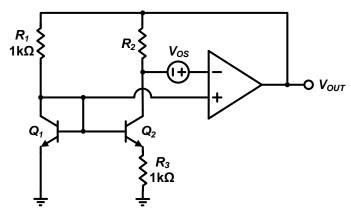

- **3.** A band-gap reference circuit is shown in Fig. PSA1.3. Assume that  $\beta_F \to \infty$ ,  $V_A \to \infty$ ,  $I_{SI} = 1 \times 10^{-15}$  A, and  $I_{S2} = 8 \times 10^{-15}$  A. Assume the opamp is ideal except for a possibly nonzero offset voltage  $V_{OS}$ .

- (a) Suppose that  $R_2$  is trimmed to set  $V_{OUT}$  equal to the target voltage for which  $dV_{OUT}/dT = 0$  at T = 25°C when  $V_{OS} = 0$ . Find  $dV_{OUT}/dT$  at T = 25°C when  $V_{OS} = 30$  mV.

- (b) Under the conditions in part (a), is  $dV_{OUT}/dT$  positive or negative? Explain.

Fig. PSA1.3

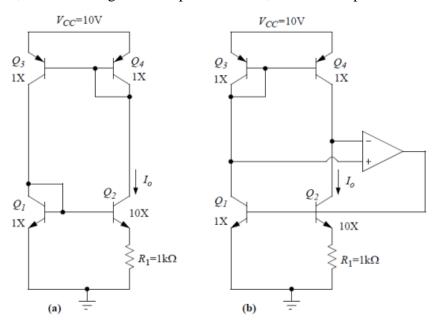

**4.** For each of the bias reference circuits shown in Fig. PSA1.4, find the sensitivity of the bias current  $I_0$  to the supply voltage  $V_{CC}$ . For each case, give a numerical value and justification. Assume a temperature of 300K, neglect base currents, and use the data given below.

## Transistors parameters:

$$\beta = 100$$

,  $r_b = 0 \Omega$ ,  $V_T = 26 \text{ mV}$  @ 300K,  $V_A = 40 \text{ V}$ ,  $I_S = 10^{-17} \text{ A for 1X device.}$

Op Amp is ideal, with infinite gain and input resistance, and zero output resistance.

Fig. PSA1.4