## **PROBLEM SET #6**

Issued: Wednesday, Oct. 7, 2015

Due (at 8 a.m.): Wednesday, Oct. 14, 2015, in the EE 140/240A HW box near 125 Cory.

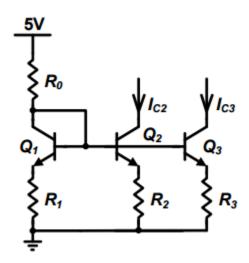

**1.** Provide an expression and calculate the numerical value for the output current mismatch between  $I_{C2}$  and  $I_{C3}$  shown in Fig. PS6-1 caused by finite fabrication tolerances.

## **Nominal Parameter Values:**

$$\beta = 100, I_s = 37.751 \text{x} 10^{-15} \text{A}, V_T = 25 \text{mV}, R_0 = 3.4 \text{k}\Omega, R_1 = R_2 = R_3 = 1 \text{k}\Omega$$

## **Fabrication Tolerances:**

$$\frac{\Delta\beta}{\beta} = 10\%, \frac{\Delta I_s}{I_s} = 5\%, \frac{\Delta R}{R} = 20\%$$

**Fig. PS6-1**

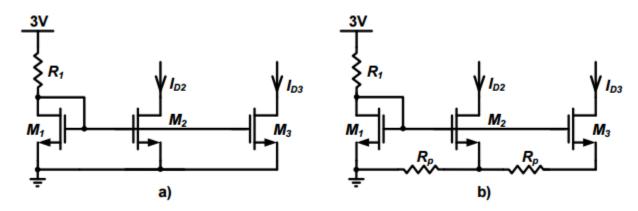

- 2. This problem considers the MOS current mirror shown in Figure PS6-2a.

- (a) Design the current mirror such that all of the following is satisfied:

- i. The currents  $I_{D2} = 0.5 \text{mA}$  and  $I_{D3} = 2 \text{mA}$ , approximately.

- ii. The minimum output voltage for which  $M_2$  and  $M_3$  work as current sources is 200mV.

- iii. The output currents change less than 1% for a 1V change in output voltages.

- iv. All transistors have the same channel length.

You are to minimize the total circuit area approximately given by:

$$A = \sum_{i=1}^{3} W_i L_i + \beta R_1$$

The parameter  $\lambda$  can be calculated as  $\lambda = \alpha/L$ .  $\alpha$  and  $\beta$  are constants.

## **Transistor Parameters:**

$$\alpha = 0.02 \frac{\mu \text{m}}{\text{V}}$$

,  $\beta = 0.2 \frac{\mu \text{m}^2}{\Omega}$ ,  $C_{ox} = 5 \frac{\text{fF}}{\mu \text{m}^2}$ ,  $\mu_n = 450 \frac{\text{cm}^2}{\text{Vs}}$ ,  $V_{th} = 0.6 \text{V}$

(b) A layout designer used long and narrow wires to connect sources of  $M_1$ ,  $M_2$ , and  $M_3$  which resulted in small parasitic resistors  $R_p = 2\Omega$  as shown in Fig. PS6-2b. What are the new values of  $I_{D2}$  and  $I_{D3}$ ? You can use numerical methods if needed.

**Fig. PS6-2**

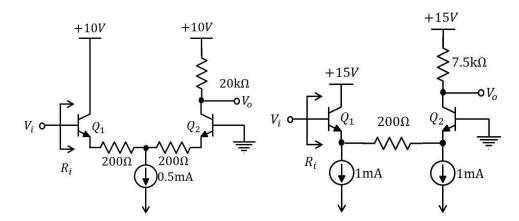

3. Calculate the mid-band gain and input resistance of the amplifiers shown in Fig. PS6-3 assuming  $\beta$ =100.

**Fig. PS6-3**

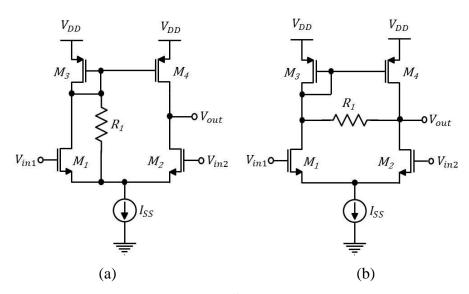

**4.** Due to a manufacturing defect, a large parasitic resistance  $R_1$  has appeared in the circuits of Fig. PS6-4. Assuming all transistors are in saturation, find an expression for the mid-band gain  $G = V_{out}/(V_{in1} - V_{in2})$  of each circuit. The expressions should be in terms of the given elements and parameters of the small-signal equivalent circuits (i.e.,  $g_{mb}$ ,  $r_o$  etc.) for the transistors. Ignore body-effect.

**Fig. PS6-4**