# <u>Laboratory 1</u> <u>Single-Stage MOSFET Amplifier Analysis and Design</u> Due Date: Week of February 26, 2013, at the beginning of your lab section

#### **Objective**

To analyze and design single-stage common source amplifiers. This lab does not require the building of the circuit. Design objectives can be accomplished and verified using hand calculations and SPICE simulations.

#### Introduction:

Since MOS technology is playing a more central role in today's analog integrated circuits, it is important to have a good understanding of MOS transistor amplifier analysis and design. It is the goal of this lab to enable you to understand the inter-relationships among gain, bandwidth, device dimensions and bias point specifications for MOS amplifiers through a simple design. Most of the knowledge obtained in this lab will be used in the design project later this semester. In the first lab you are asked to analyze, design, and simulate a simple MOS amplifier to satisfy a given set of specifications.

## <u> Part 1:</u>

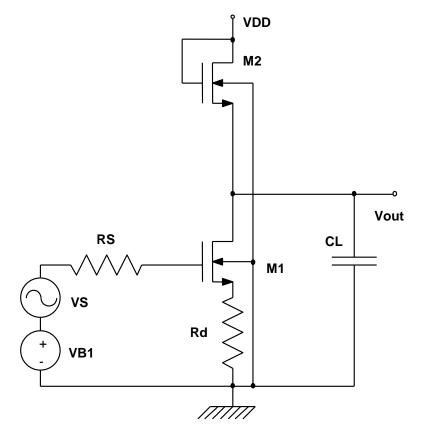

In this first part you will analyze and simulate a saturated NMOS load common-source amplifier shown in Figure 1 below.

Figure 1: Saturated NMOS Load common-source amplifier.

CTN 2/4/13

For both parts assume the following parameters for the transistor when doing hand calculations and SPICE simulations:

| Parameter | NMOS                                  | PMOS                                  |

|-----------|---------------------------------------|---------------------------------------|

| Level     | 4 (In HSPICE)                         | 4 (In HSPICE)                         |

| VTO       | 0.8 V                                 | -0.8 V                                |

| KP        | $90 \ \mu A/V^2$                      | $30 \ \mu A/V^2$                      |

| GAMMA     | $0.8\sqrt{\mathrm{V}}$                | $0.4\sqrt{V}$                         |

| LAMBDA    | 0.01 V <sup>-1</sup>                  | 0.02 V <sup>-1</sup>                  |

| TOX       | 200 Å                                 | 200 Å                                 |

| XJ        | 0.5 μm                                | 0.5 μm                                |

| LD        | 0.3 µm                                | 0.3 μm                                |

| PHI       | 0.7 V                                 | 0.6 V                                 |

| NSUB      | $3.33 \times 10^{16} \text{ cm}^{-3}$ | $3.33 \times 10^{15} \text{ cm}^{-3}$ |

| RSH       | 0 Ω                                   | 0 Ω                                   |

| CGSO      | 500P, F/M                             | 500P, F/M                             |

| CGDO      | 500P, F/M                             | 500P, F/M                             |

| CGBO      | 0, F/M                                | 0, F/M                                |

| CJ        | 300U, F/M <sup>2</sup>                | 300U, F/M <sup>2</sup>                |

| MJ        | 0.5                                   | 0.5                                   |

| CJSW      | 0, F/M                                | 0, F/M                                |

| MJSW      | 0.33                                  | 0.33                                  |

#### PROCESS/SPICE PARAMETERS FOR NMOS/PMOS TRANSISTORS

Note that all biasing in this circuit is performed using the DC source VB1. The power supply for this amplifier is VDD = 5V. There are two external elements in this amplifier:

RS= Source Resistance =  $1M\Omega$ CL= Load Capacitance = 5pFRd = Degeneration Resistance (Will Be Given Later)

# Task a:

Assume that:

VB1= 1.1V Rd=0 (i.e. no degeneration) (W/L)<sub>1</sub> =(40/5)  $\mu$ m/ $\mu$ m (W/L)<sub>2</sub> = (5/90)  $\mu$ m/ $\mu$ m

Determine the small-signal voltage gain vo/vs, the upper cutoff frequency (or bandwidth), and the output resistance of the amplifier using BOTH hand calculation and SPICE simulation.

#### EE 140 / EE 240A ANALOG INTEGRATED CIRCUITS

You should show the plot of the magnitude of the gain in dB vs. log(frequency) for this amplifier. Note that you can make any reasonable approximations in your hand calculations. If the simulated and calculated results do not agree you should discuss the reasons. Also determine the maximum output voltage swing that this amplifier can deliver. You can use SPICE simulation only for this part.

# Task b:

In this part we add some degeneracy into the circuit by changing the value of resistor Rd. You can assume that:

VB1= 1.3V Rd=5k $\Omega$ (W/L)<sub>1</sub> =(40/5)  $\mu$ m/ $\mu$ m (W/L)<sub>2</sub> = (5/90)  $\mu$ m/ $\mu$ m

Determine the small-signal voltage gain vo/vs, the upper cutoff frequency (or bandwidth), and the output resistance of the amplifier using BOTH hand calculation and SPICE simulation. You should show the plot of the magnitude of the gain in dB vs. log(frequency) for this amplifier. Note that you can make any reasonable approximations in your hand calculations. If the simulated and calculated results do not agree you should discuss the reasons. Also determine the maximum output voltage swing that this amplifier can deliver. You can use SPICE simulation only for this part.

For both of these tasks you should list the relevant performance parameters in a Table.

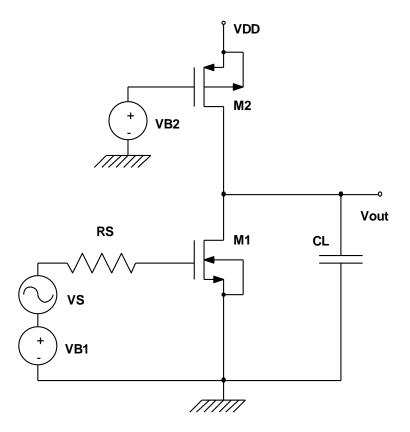

# Part 2: MOS Amplifier Design:

In this part you are asked to design a common-source amplifier with a saturated PMOS load as shown in the figure below:

Note that all biasing in this circuit is performed with two DC sources VB1 and VB2. The power supply for this amplifier is VDD = 5V. In your design you have to determine the values of these two sources. There are two external elements in this amplifier:

$$RS$$

= Source Resistance =  $2M\Omega$

$CL$ = Load Capacitance =  $2pF$

Design the above common-source amplifier so that it satisfies the following specifications:

| Parameter             | Specification                        |

|-----------------------|--------------------------------------|

| Midband Gain          | $\geq$ 120 V/V                       |

| 3dB Cutoff Frequency  | ≥ 20kHz                              |

| Output Voltage Swing  | Within 0.5V of VDD & Ground          |

| Load Capacitance, CL  | 2pF                                  |

| Source Resistance, RS | 2 ΜΩ                                 |

| Supply Voltage:       | $V_{DD} = +5V, V_{SS} = Ground = 0V$ |

# EE 140 / EE 240A ANALOG INTEGRATED CIRCUITS SPRING 2013

There are several important issues that you have to remember as you design your amplifier. These are itemized below:

- 1. Note that the Lambda value is given for L=5 $\mu$ m. All of your transistors should have a length of 5 $\mu$ m. You cannot use any other channel length for this problem. For Lambda calculation you can ignore lateral diffusion and assume that the value of Lambda at L=4.4 $\mu$ m is the same as that at L=5 $\mu$ m.

- 2. The gate oxide thickness is provided so that you can calculate the relevant capacitances that you need in your calculations. Note that some of the capacitance parameters that are typically needed in SPICE are already calculated for you. You may need some of these in your design.

- 3. When you perform the design you should ensure that the circuit is biased such that all transistors are in saturation. This may require very fine tuning of the bias voltages VB1 and VB2 down to the millivolt value. The reason for this is that the amplifier has such a high gain that the slightest shift in the bias point value will cause one or the other transistor to come out of saturation.

- 4. When biasing these transistors you should not use a  $V_{GS} V_T$  of smaller than 200mV for either of the transistors. This means that the  $V_{GS}$  across either transistor has to be higher than 1.0V.

You should pay attention to the following in your design:

- 1. You need to determine the dimensions for both transistors M1 and M2, as well as the values for bias sources VB1 and VB2 at the end of your design. In addition, you should show both by hand calculations and computer simulations that the specifications have been satisfied. Include plots (or tables) of simulations results where necessary and make sure that all plots are labeled appropriately. The hand calculations and the equations and relationships you use are very important and they should be included in your lab report. All equations should be in variable form before numerical evaluation. Your design approach should be outlined in your report. Your hand calculations and simulation results may differ quite significantly. Try to explain why this is the case if you observe this.

- 2. Calculate the output resistance of the final amplifier and compare it with the output resistance of the CS amplifier used in Task a of Part 1.

- 3. You should use HSPICE, Level=4, for this lab.

- 4. You are to work on this lab <u>individually</u>. Although you can discuss generalities with other students in the class, you are not to perform the design in teams or groups.

- 5. Your lab report should be brief, concise, and complete, and should include your hand calculations, and a table comparing the design specifications as well as your actual circuit's specifications. A discussion on the tradeoffs and design strategy should be provided in your report. The report need not be very long, and the format of the report is left up to you. Just make sure that the report is clear and easy to read so that your TA can follow your

# EE 140 / EE 240A ANALOG INTEGRATED CIRCUITS SPRING 2013

presentation. If you cannot meet the design specifications make sure that your report states why and explain what critical factors prevented you from achieving your design goals and suggest directions for modifying your design to meet specifications.

You should try your best to achieve the design specifications. If after all attempts you fail to meet all the design specifications, describe to us your final design and what you consider to have been the most restrictive and problematic spec to meet.