### EE143 – Fall 2016 Microfabrication Technologies

#### **Lecture 14: MEMS Process**

Prof. Ming C. Wu wu@eecs.berkeley.edu 511 Sutardja Dai Hall (SDH)

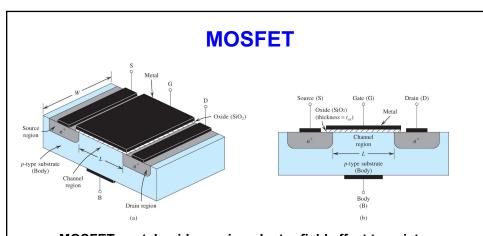

- MOSFET: metal-oxide-semiconductor field effect transistor

- Typically

- Channel length: L ~ 10 nm to 0.35  $\mu$ m,

- Channel width: W ~ 0.05  $\mu m$  to 100  $\mu m$ ,

- Oxide thickness:  $t_{ox} \sim 1$  to 10 nm

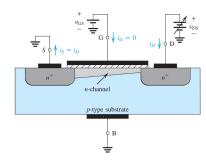

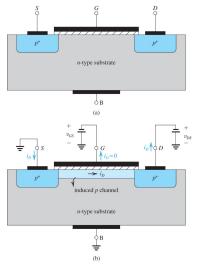

#### **NMOSFET (or simply NMOS)**

- N-channel MOSFET

- Current conducted by electrons

- · 3 terminal device

- Source (S): n+ (heavily n-type)

- Drain (D): n+

- Gate (G): metal deposited on insulator above channel

- Substrate (called "Body") is a 4<sup>th</sup> terminal

- Substrate is p-doped

- Electrons is induced in channel when a positive gate voltage is applied

- · Electrons moves from Source to Drain

- Current flows from D to S

3

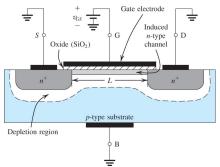

# Creating a "Channel" for Current Flow

MOS is a capacitor across an insulator (oxide) When a positive voltage is applied at Gate, electrons are induced under the gate.

At "thresold", sufficient number of electrons form a "channel" between Source and Drain, forming a conductive channel.

Total charge in the channel:

$$|Q| = C_{ox} \cdot WL \cdot (v_{GS} - V_t)$$

where  $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$  is oxide capacitance

per unit area

$$\varepsilon_{ox} = 3.9 \varepsilon_0 = 3.9 \times 8.854 \times 10^{-12} \text{ F/m}$$

W: gate width

L: gate length

$V_t$ : Threshold voltage

$v_{GS} - V_t \equiv v_{OV}$  is called "Overdrive Voltage"

RSAC

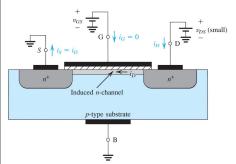

### **Current at Small v<sub>DS</sub>**

When  $v_{OV} = v_{GS} - V_t > 0$ , a channel is formed between Source and Drain.

Linear charge density in channel:

$$\frac{|Q|}{L} = C_{ox}W \cdot v_{OV}$$

Electric field along the channel

$$|E| = \frac{v_{DS}}{L}$$

Drain current = charge density x velocity:

$$i_D = \frac{|Q|}{L} v_n = \frac{|Q|}{L} \mu_n |E| = C_{ox} W \cdot v_{OV} \mu_n \frac{v_{DS}}{L}$$

$$W$$

$$i_D = \mu_n C_{ox} \frac{W}{L} v_{OV} v_{DS}$$

At small  $v_{DS}$ , the transistor is like a gate-controlled variable resistor

**BSAC**

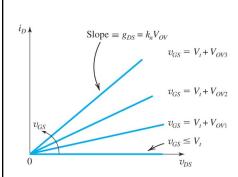

## **Current at Small v<sub>DS</sub>**

$$i_D = \mu_n C_{ox} \frac{W}{L} v_{OV} v_{DS}$$

$$= k_n \frac{W}{L} v_{OV} v_{DS}$$

$$= k_n v_{OV} v_{DS}$$

where

$\vec{k_n} = \mu_n C_{ox}$ : process transconducance paramter

$$v_{GS} = V_t + V_{OV1}$$

$k_n = \mu_n C_{ox} \frac{W}{L}$ : MOSFET transconductance

parameter

MOSFET behaves like a linear resistor

$$r_{DS} = \frac{v_{DS}}{i_D} = \frac{1}{k_n v_{OV}}$$

Resistance value can be changed by gate voltage (overdrive voltage)

**BSAC**

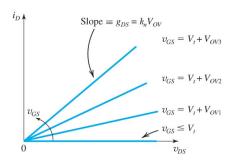

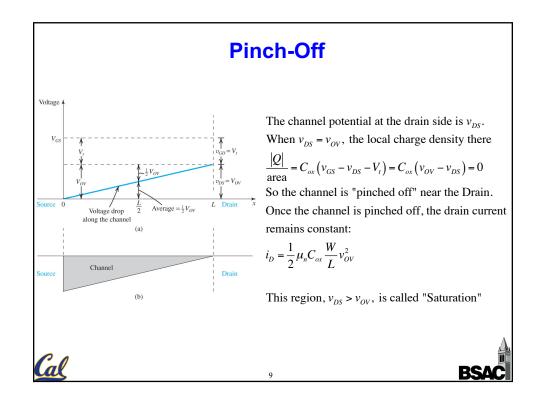

### Triode Region ( $v_{DS} < v_{OV}$ )

As  $v_{DS}$  increases, the potential in the channel is no longer a constant. Assume the channel is v(x):

$$i_D = C_{ox}W(v_{GS} - v(x) - V_t)v_n(x)$$

$$v_n(x) = \mu_n |E(x)| = \mu_n \frac{dv(x)}{dx}$$

Note:  $i_D$  is still constant along the channel (think Kirchhoff's Current Law)

$$\int\limits_{x=0}^{x=L}i_{D}dx=\int\limits_{x=0}^{x=L}\left(C_{ox}W\left(v_{GS}-v(x)-V_{t}\right)\mu_{n}\frac{dv(x)}{dx}\right)dx$$

Change of variable on right-hand side:  $x \rightarrow v$

$$i_D L = \int_{v=0}^{v=v_{DS}} \left( C_{ox} W \left( v_{OV} - v \right) \mu_n \right) dv$$

$$i_D = \mu_n C_{ox} \frac{W}{L} \left( v_{OV} v_{DS} - \frac{1}{2} v_{DS}^2 \right)$$

BSAC

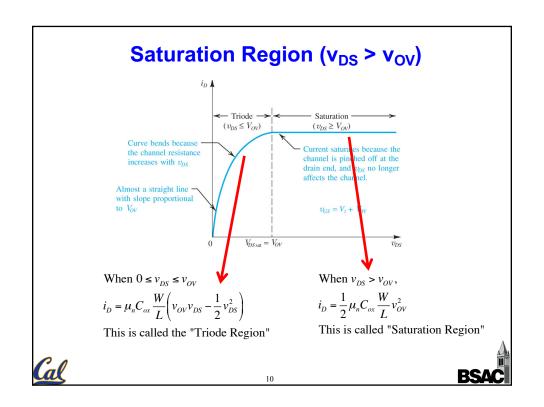

# Triode $v_{DS} \le V_{OV}$ Saturation $v_{DS} \ge V_{OV}$ Curve bends because the channel resistance increases with $v_{DS}$ Almost a straight line with slope proportional to $v_{OV}$

Triode Region  $(v_{DS} < v_{OV})$

$V_{DS \, \text{sat}} = V_{OV}$

When  $0 \le v_{DS} \le v_{OV}$

$$i_D = \mu_n C_{ox} \frac{W}{L} \left( v_{OV} v_{DS} - \frac{1}{2} v_{DS}^2 \right)$$

This is called the "Triode Region"

**BSAC**

#### **PMOSFET (or simply PMOS)**

- P-channel MOSFET

- Current conducted by holes

- · 3 terminal device

- Source (S): p+ (heavily p-type)

- Drain (D): p+

- Gate (G): metal deposited on insulator above channel

- Substrate (called "Body") is a 4<sup>th</sup> terminal

- Substrate is n-doped

- Holes is induced in channel when a negative gate voltage is applied

- Holes moves from Source to Drain

- Current flows from S to D

11

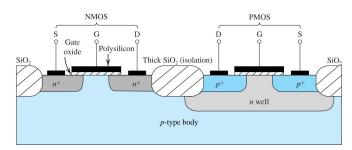

# CMOS (Complementary MOS)

- CMOS is the prevalent IC technology today

- Since NMOS and PMOS are formed on oppositely doped substrates, one of the transistor needs to be placed in a "well"

- · PMOS is placed in an "n well" here.

- · Alternatively, NMOS can be placed in p well

BSAC

6