4/13/10

| EE 143 CMOS Process Flow                                                                                                                                                                                                                                                                                                   |                                               |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

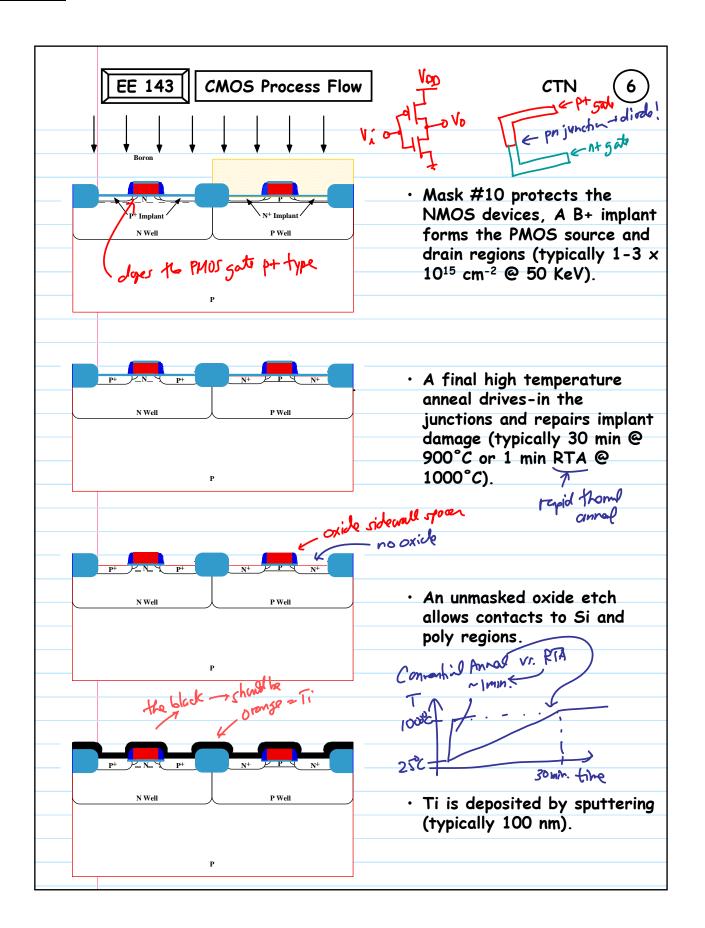

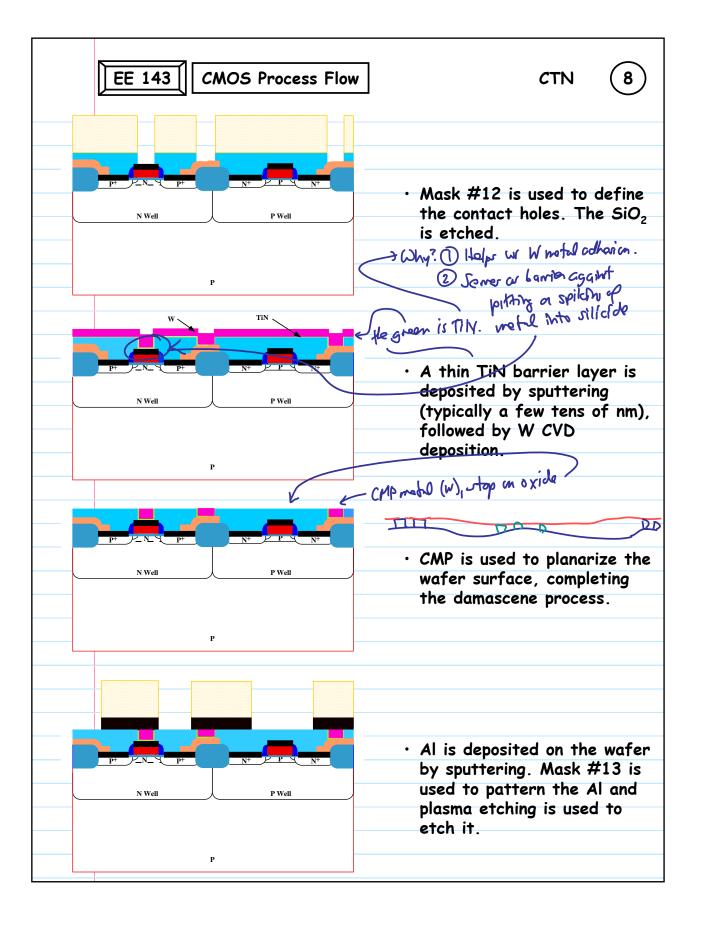

|                                                                                                                                                                                                                                                                                                                            | <ul> <li>Intermetal dielectric and</li> </ul> |  |

|                                                                                                                                                                                                                                                                                                                            | second level metal are                        |  |

|                                                                                                                                                                                                                                                                                                                            | deposited and defined in                      |  |

|                                                                                                                                                                                                                                                                                                                            | the same way as level #1.                     |  |

|                                                                                                                                                                                                                                                                                                                            | Mask #14 is used to define                    |  |

| N Well P Well                                                                                                                                                                                                                                                                                                              | contact vias and Mask #15                     |  |

|                                                                                                                                                                                                                                                                                                                            | is used to define metal 2.                    |  |

|                                                                                                                                                                                                                                                                                                                            | A final passivation layer                     |  |

| Р                                                                                                                                                                                                                                                                                                                          | of $Si_3N_4$ is deposited by                  |  |

|                                                                                                                                                                                                                                                                                                                            | PECVD and patterned                           |  |

| There will be more leads of metal -> Cu.                                                                                                                                                                                                                                                                                   | with Mask #16.                                |  |

| Use a dual-damascene process.         Differences from older long-channel CMOS:         1. Very thin lightly doped drain (LDD) and source junctions;         very small x <sub>j</sub> 2. Very thin gate oxide         3. Much higher channel & substrate doping         & So why these differences? Answer: punchthrough! |                                               |  |

| Go to the regular lecture written                                                                                                                                                                                                                                                                                          | format to discuss punchthrough.               |  |

| Ē | E 143 CMOS Process Flow<br>Electroplated Cy for highe                                                                                                                                                                                                                                                                                                                                                                                                          | CTN (10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | Ebetroplated Cu fin higher<br>N Well P<br>P<br>ene will be more levels of metal - Cu.<br>re a dual-damascene process.<br>Fferences from older long-cha<br>Very thin lightly doped drain<br>very small x <sub>j</sub><br>Very thin gate oxide<br>Much higher channel & substr<br>So why these differences?<br>marks:<br>More advanced technologies also<br>for reasons explained above<br>SiO <sub>2</sub> can no longer satisfy,<br>thicknesses below 1 nm has | <ul> <li>Intermetal dielectric and second level metal are deposited and defined in the same way as level #1. Mask #14 is used to define contact vias and Mask #15 is used to define metal 2. A final passivation layer of Si<sub>3</sub>N<sub>4</sub> is deposited by PECVD and patterned with Mask #16.</li> <li><u>nnel CMOS</u>:</li> <li>(LDD) and source junctions;</li> <li>Pate doping</li> <li><u>Answer</u>: punchthrough!</li> <li>so require a thinner gate oxide,</li> <li>, since the gate oxide ve leakage issues</li> </ul> |  |

|   | <ul> <li>♦ Newest technologies use ALD high-k oxides (e.g., HfO₂)</li> <li>More advanced technologies must reduce as much as possible the interconnect capacitance ⇒ low-k inter-metal dielectrics</li> <li>The use of LOCOS in this process limits it to 0.18-0.25 μm channel lengths</li> </ul>                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|   | <ul> <li>Any smaller and the LOCOS encroachment it too much</li> <li>Plus, the topography makes lithography for smaller<br/>channel lengths more difficult</li> </ul>                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |