#### Copyright © 2010 Regents of the University of California

# CTN 1/28/10

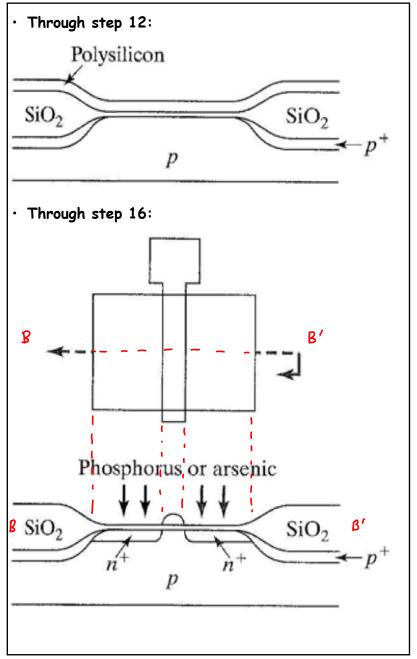

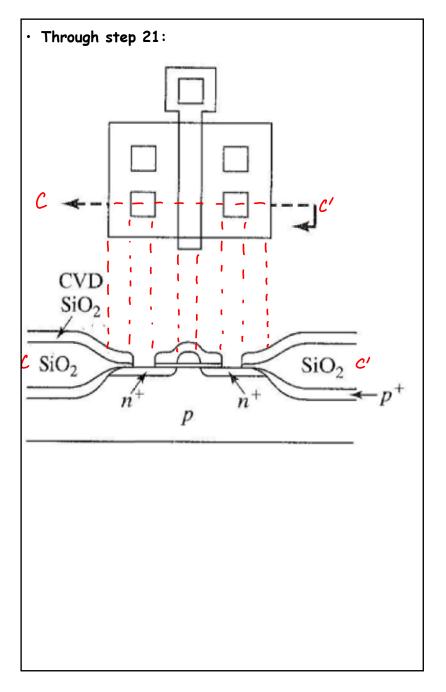

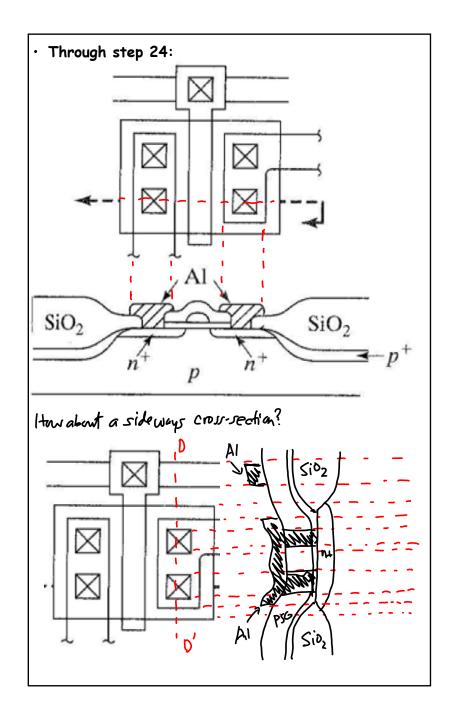

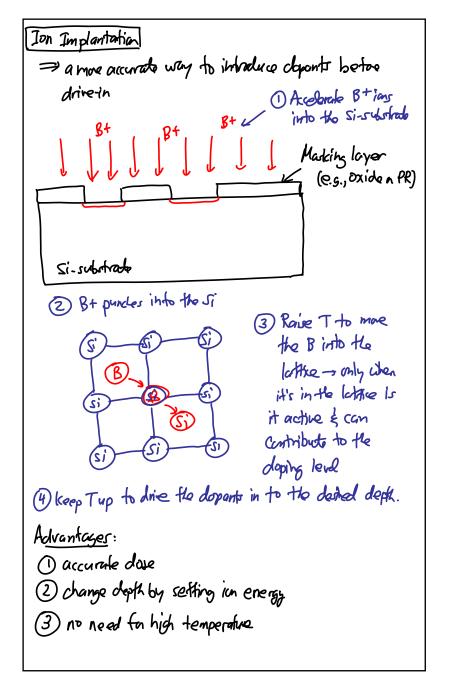

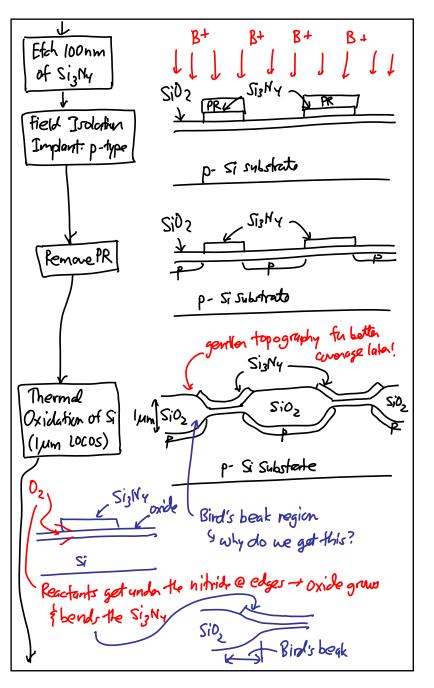

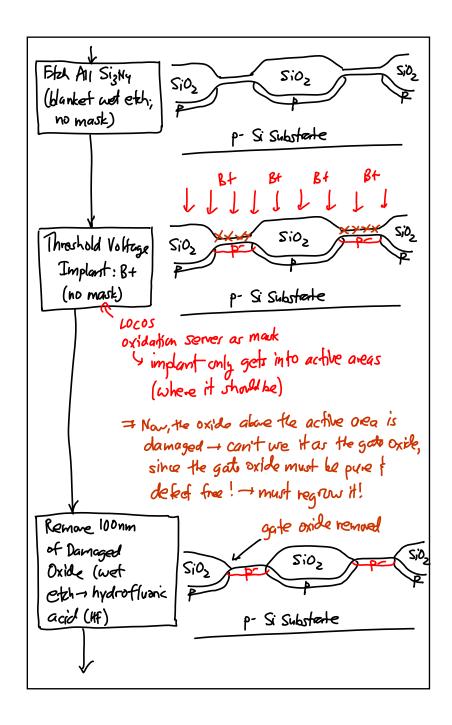

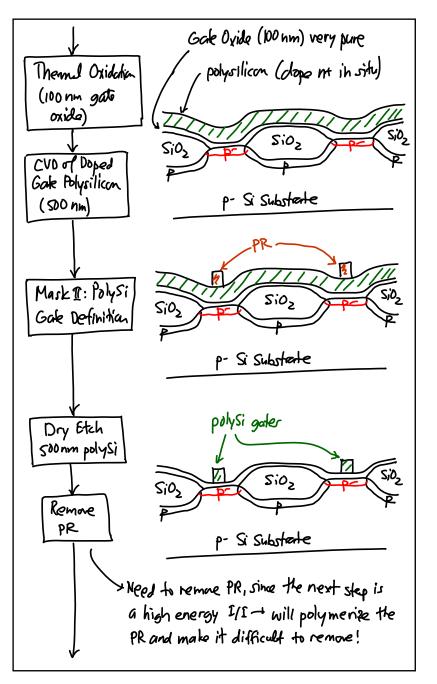

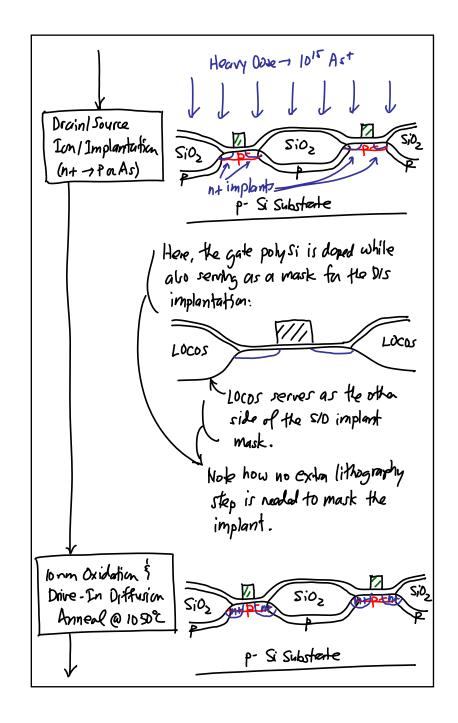

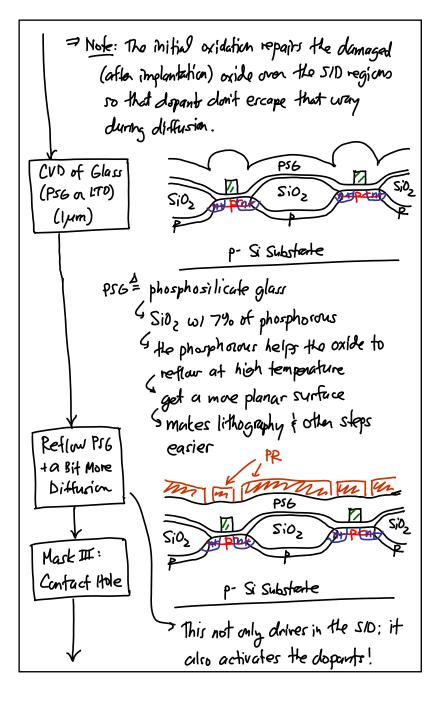

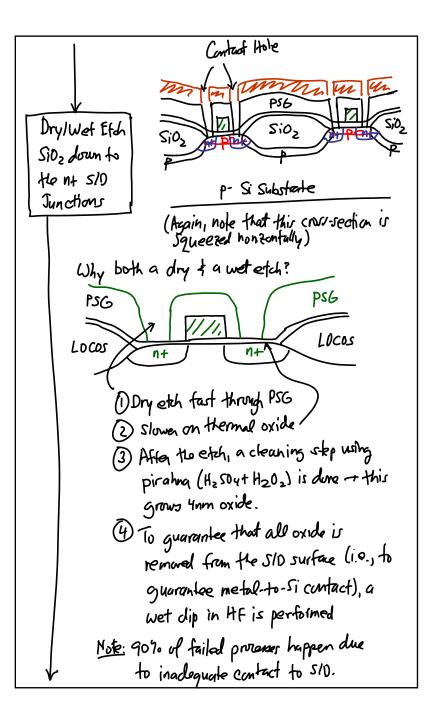

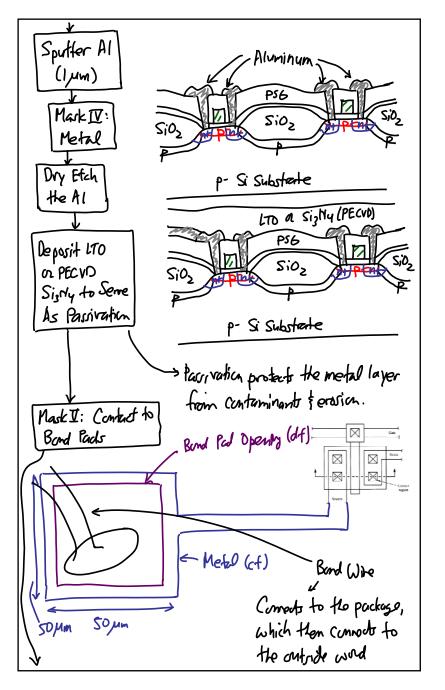

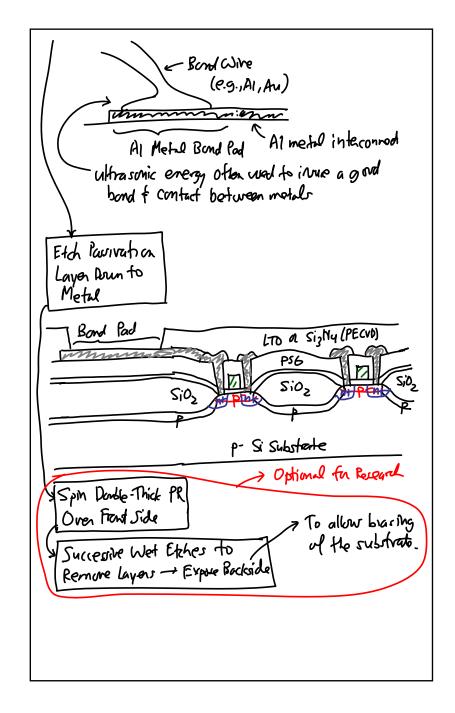

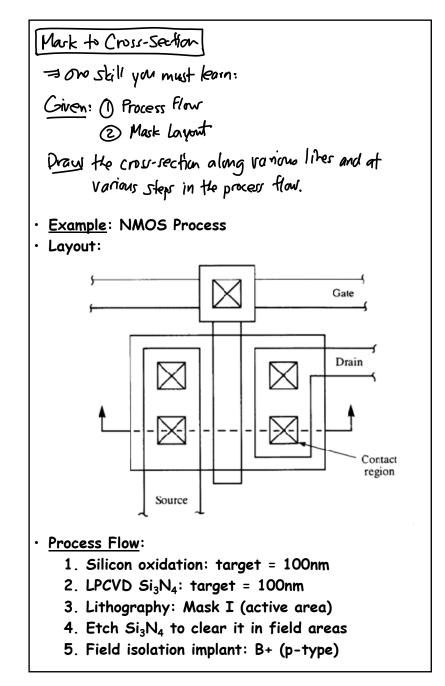

6. Remove PR 7. Grow 1 mm of SiO<sub>2</sub> by thermal oxidation (LOCOS oxidation) 8. Blanket etch all  $Si_3N_4$  in hot phosphoric acid wet etchant 9. Threshold voltage implant: B+ (no mask) 10. Remove 100nm of damaged oxide via a timed wet etch in hydrofluoric acid (HF) 11. Grow 100nm of gate thermal oxide in an ultra-clean furnace 12.LPCVD situ phosphorous-doped gate polysilicon 13.Lithography: Mask II (gate polysilicon) 14. Dry etch polysilicon to clear the field areas 15 Remove PR 16.D/S ion implantation: P or As (n-type) 17. Oxidize a bit (10nm) and anneal at 1050°C to activate dopants and drive-in diffusion 18.LPCVD PSG: target =  $1 \mu m$ 19.Reflow PSG (& a little bit of diffusion) at 950°C 20.Lithography: Mask III (contact hole) 21. Dry/wet etch SiO<sub>2</sub> down to n+ S/D regions 22.Sputter Al: target = 1µm 23. Lithography: Mask IV (metal) 24. Dry etch Al 25. Deposit via LTO or PECVD Si<sub>3</sub>N<sub>4</sub> to serve as passivation 26.Lithography: Mask V (bond pad contacts) 27. Etch passivation layer down to metal 28.(optional) spin double-thick PR over the front

side