# EECS 16A Designing Information Devices and Systems I Fall 2019 Discussion 10B

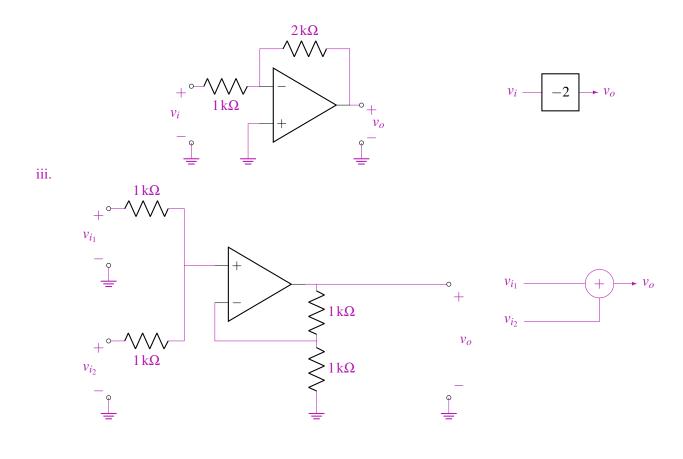

#### For Reference: Example Circuits

#### 1. Op-Amp Rules and Negative Feedback Rule

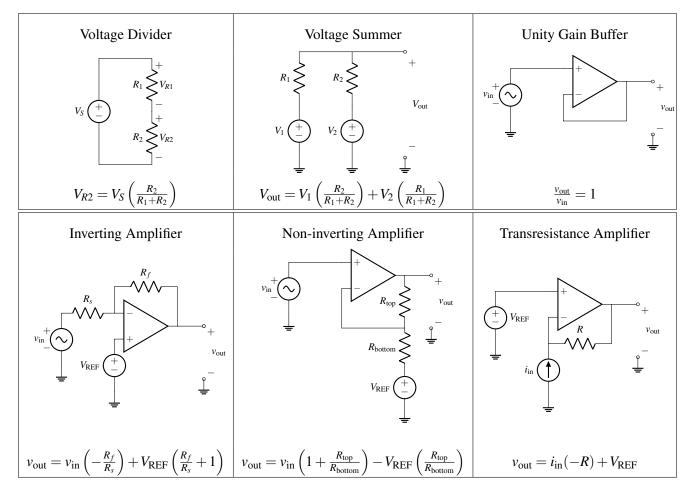

Here is an equivalent circuit of an op-amp (where we are assuming that  $V_{SS} = -V_{DD}$ ) for reference:

(a) What are the currents flowing into the positive and negative terminals of the op-amp (i.e., what are  $I^+$  and  $I^-$ )? What are some of the advantages of your answer with respect to using an op-amp in your circuit designs?

# Answer:

The  $u^+$  and  $u^-$  terminals have no closed circuit connection between them, and therefore no current can flow into or out of them. This is very good because we can connect an op-amp to any other circuit, and the op-amp will not disturb that circuit in any way because it does not load the circuit (it is an open circuit).

(b) Suppose we add a resistor of value  $R_L$  between  $u_{out}$  and ground. What is the value of  $v_{out}$ ? Does your answer depend on  $R_L$ ? In other words, how does  $R_L$  affect  $Av_C$ ? What are the implications of this with respect to using op-amps in circuit design?

# Answer:

Notice that  $u_{out}$  is connected directly to a controlled/dependent voltage source, and therefore  $v_{out}$  will always have to be equal to  $Av_C$  regardless of what  $R_L$  is connected to the op-amp. This is very advantageous because it means that the output of the op-amp can be connected to any other circuit (except a voltage source), and we will always get the desired/expected voltage out of the op-amp.

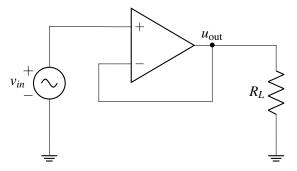

For the rest of the problem, consider the following op-amp circuit in negative feedback:

(c) Assuming that this is an ideal op-amp, what is  $v_{out}$ ?

#### Answer:

Recall for an ideal op-amp in negative feedback, we know from the negative feedback rule that  $u^+ = u^-$ . In this case,  $u^- = u_{out} = u^+$ .

UCB EECS 16A, Fall 2019, Discussion 10B, All Rights Reserved. This may not be publicly shared without explicit permission. 2

(d) Draw the equivalent circuit for this op-amp and calculate  $v_{out}$  in terms of A,  $v_{in}$ , and  $R_L$  for the circuit in negative feedback. Does  $v_{out}$  depend on  $R_L$ ? What is  $v_{out}$  in the limit as  $A \rightarrow \infty$ ?

Answer:

Notice that the op-amp can be modeled as a voltage-controlled voltage source. Thus, we have the following equation:

$$v_{\text{out}} = A(v_{in} - v_{\text{out}})$$

$$v_{\text{out}} + Av_{\text{out}} = Av_{in}$$

$$v_{\text{out}} = v_{in}\frac{A}{1 + A}$$

Thus, as  $A \to \infty$ ,  $v_{out} \to v_{in}$ . This is the same as what we get after applying the op-amp rule. Notice that output voltage does not depend on *R*. Thus, this circuit acts like a voltage source that provides the same voltage read at  $u^+$  without drawing any current from the terminal at  $u^+$ . This is why the circuit is often referred to as a "unity gain buffer," "voltage follower," or just "buffer."

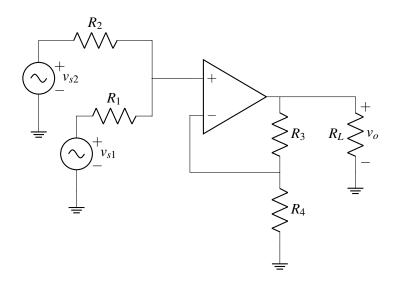

#### 2. Multiple Inputs To One Op-Amp

(a) For the circuit above, find an expression for  $v_o$ . (*Hint: Use superposition.*)

### Answer:

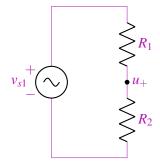

Let's call the potential at the positive input of the op-amp  $u_+$ . Using superposition, we first turn off  $v_{s2}$  and find  $u_+$ . The circuit then looks like:

We recognize the above circuit as a voltage divider. Thus,

$$u_{+,vs1} = \frac{R_2}{R_1 + R_2} v_{s1}$$

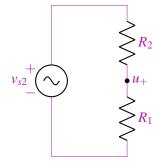

By symmetry, we expect  $v_{s2}$  to have a similar circuit and expression. The circuit for  $v_{s2}$  looks like:

The expression for  $u_+$  with  $v_{s2}$  is then:

$$u_{+,vs2} = \frac{R_1}{R_1 + R_2} v_{s2}$$

From superposition, we know the output must be the sum of these.

$$u_{+} = \frac{R_2}{R_1 + R_2} v_{s1} + \frac{R_1}{R_1 + R_2} v_{s2}$$

With  $u_+$  determined, we can find the output voltage directly from the formula for a non-inverting amplifier. We can also derive it using the process below.

From the negative feedback rule,  $u_+ = u_-$ . Using voltage dividers, we can express  $u_-$  in terms of  $v_o$ :

$$u_{-} = \frac{R_4}{R_3 + R_4} v_o$$

$$v_o = \left(1 + \frac{R_3}{R_4}\right) u_{-} = \left(1 + \frac{R_3}{R_4}\right) u_{+}$$

Now, to find the final output, we can set  $u_+$  to our earlier expression.

$$v_o = \left(1 + \frac{R_3}{R_4}\right) \left(\frac{R_2}{R_1 + R_2} v_{s1} + \frac{R_1}{R_1 + R_2} v_{s2}\right)$$

(b) How could you use this circuit to find the sum of different signals?

#### **Answer:**

The circuit already finds the weighted sum of two inputs. By setting  $R_1 = R_2$  and  $R_3 = R_4$ , we can take the exact sum of two inputs.

$$v_o = \left(1 + \frac{R_3}{R_4}\right) \left(\frac{R_2}{R_1 + R_2} v_{s1} + \frac{R_1}{R_1 + R_2} v_{s2}\right) = (1+1) \left(\frac{1}{2} v_{s1} + \frac{1}{2} v_{s2}\right) = v_{s1} + v_{s2}$$

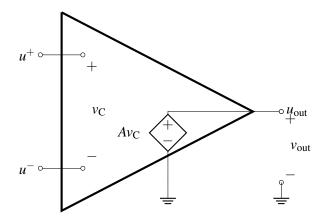

#### 3. Modular Circuits

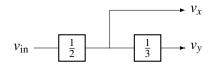

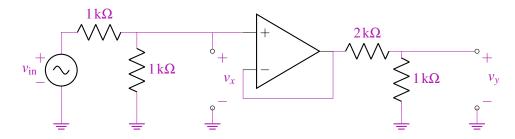

In this problem, we will explore the design of circuits that perform a set of (arbitrary) mathematical operations in order to elucidate some of the important properties and uses of op-amps in negative feedback. In the last discussion, we noticed that voltage dividers are not compose-able, so we will use op-amps instead. Again, recall that we want to implement the block diagram shown below:

UCB EECS 16A, Fall 2019, Discussion 10B, All Rights Reserved. This may not be publicly shared without explicit permission. 4

In other words, we want to implement a circuit with two outputs  $v_x$  and  $v_y$ , where  $v_x = \frac{1}{2}v_{in}$  and  $v_y = \frac{1}{3}v_x$ .

(a) Using an ideal op-amp in negative feedback, modify the design of one of the two voltage divider circuits you built (i.e. the  $\frac{1}{2}$  block or the  $\frac{1}{3}$  block), so that the originally intended relationships between  $v_x$  and  $v_{in}$  as well as  $v_y$  and  $v_x$  are realized by the resulting overall circuit (where each block is replaced by its individual implementation). Is this configuration enough by itself to attach loads at  $v_x$  and  $v_y$ ? **Answer:**

Use a voltage buffer. Note that this configuration's outputs would change with the addition of a load. As a follow-up, think about ways to make the outputs agnostic to the loads attached. If we used the latter half of the circuit as a fractional divider block, we would need to buffer the output.

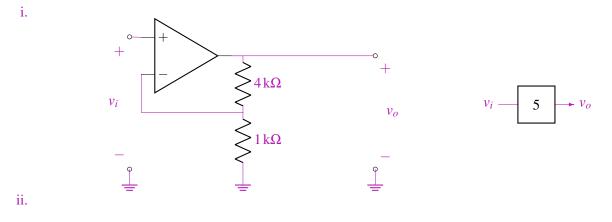

- (b) Now let's assume that we want to expand our toolbox of circuits that implement mathematical operations. In particular, design blocks that implement:

- i.  $v_o = 5 v_i$

ii.

$$v_o = -2v_i$$

iii.

$$v_o = v_{i_1} + v_{i_2}$$

Pay careful attention to the way you design these blocks, so that connecting any one block to any other block does not modify the intended functionality of any of the blocks.

**Answer:**