## RC Circuits / Differential Equations

#### **OUTLINE**

- Review: CMOS logic circuits & voltage signal propagation

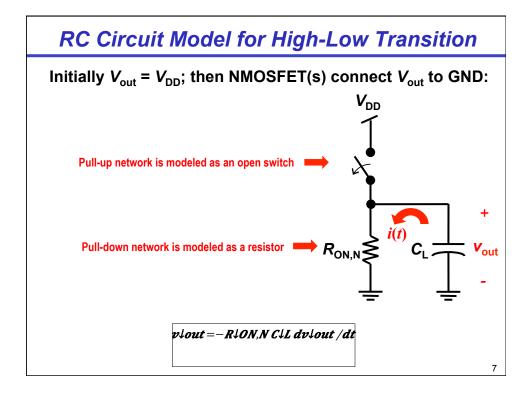

- Model: RC circuit  $\rightarrow$  differential equation for  $V_{\text{out}}(t)$

- Derivation of solution for  $V_{\text{out}}(t) \rightarrow \text{propagation delay formula}$

EE16B, Fall 2015

### Meet the Guest Lecturer

Prof. Tsu-Jae King Liu

- Joined UCB EECS faculty in 1996

- Courses taught: 40, 105, 130, 143, 290D, 375

- · Research in nanoelectronic & nanomechanical devices

### The MOSFET Metal-Oxide-Semiconductor <u>Field-Effect Transistor:</u> GATE LENGTH, $L_{\rm G}$ OXIDE THICKNESS, $T_{ox}$ Intel's 32nm MOSFETs Gate Source <sub>1</sub> Drain **Substrate** · Current flowing between the heavily doped SOURCE & DRAIN regions is controlled by the voltage on the GATE electrode N-channel & P-channel MOSFETs operate in a complementary manner **NMOSFET PMOSFET GATE VOLTAGE CIRCUIT SYMBOLS:** 3

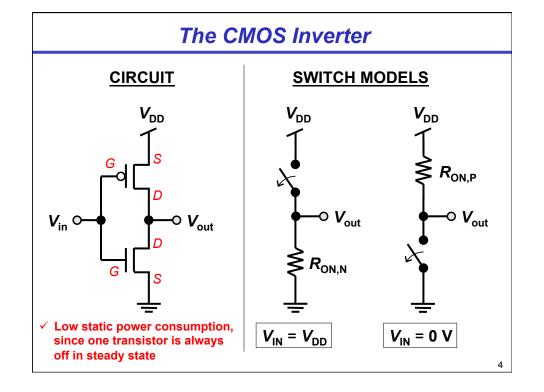

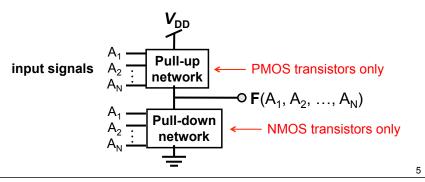

## Pull-Down and Pull-Up Devices

- In CMOS logic gates, NMOS transistors are used to connect the output to GND, whereas PMOS transistors are used to connect the output to V<sub>DD</sub>.

- An NMOS transistor functions as a *pull-down device* when it is turned on (gate voltage = V<sub>DD</sub>)

- A PMOS transistor functions as a *pull-up device* when it is turned on (gate voltage = **GND**)

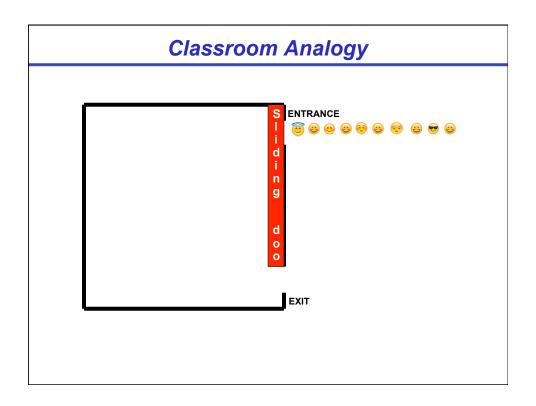

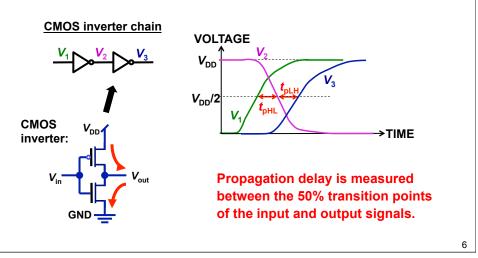

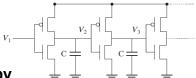

### **Voltage Signal Propagation**

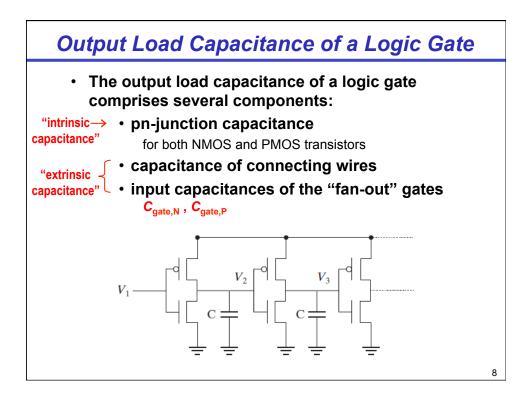

When an input voltage of a logic gate is changed, there

is a propagation delay before the output of the logic

gate changes, due to capacitive loading at the output.

| Derivation of RC Model |   |

|------------------------|---|

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        | 9 |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

|                        |   |

| By separation of variables:                               |

|-----------------------------------------------------------|

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

| Derivation of $V_{\text{out}}(t)$ for High-Low Transition |

| With eigenfunctions:                                      |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

Derivation of  $V_{\text{out}}(t)$  for High-Low Transition

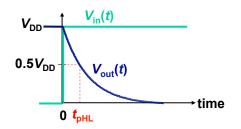

# Derivation of Formula for $t_{pHL}$

$$V_{out}(t) = V_{DD}e^{-t/R_{ON,N}C_L}$$

13

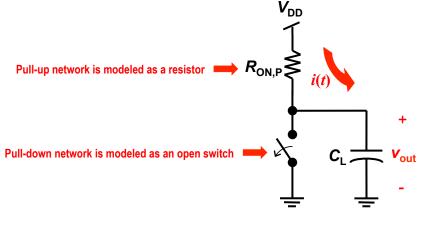

# RC Circuit Model for Low-High Transition

Initially  $V_{\text{out}} = 0$ ; then PMOSFET(s) connect  $V_{\text{out}}$  to  $V_{\text{DD}}$ :

V↓DD – v↓out = – R↓ON,P C↓L dv↓out /dt

| Derivation of V <sub>out</sub> (t) for Low-High Transition |    |

|------------------------------------------------------------|----|

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

| 1                                                          | 15 |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

# Derivation of Formula for $t_{pLH}$

$$V_{out}(t) = V_{DD} \left( 1 - e^{-t/R_{ON,P}C_L} \right)$$

$$0.5V_{DD}$$

$$V_{out}(t)$$

$$V_{out}(t)$$

$$V_{in}(t)$$

$$V_{in}(t)$$

$$V_{in}(t)$$

17

### Minimizing Propagation Delay

### A fast CMOS logic circuit is built by

#### 1. Keeping the output capacitance $C_1$ small

- → Minimize the area of drain pn junctions.

- → Lay out devices to minimize interconnect capacitance.

- → Avoid large fan-out.

# 2. Decreasing the equivalent resistance of the transistors

- → Decrease gate length L<sub>G</sub>

- → Increase transistor width W

- ... but this increases pn junction area and hence C<sub>L</sub>

### 3. Increasing $V_{DD}$

→ trade-off with power consumption...