## EE 240B – Spring 2018

#### Advanced Analog Integrated Circuits Lecture 2: MOS Transistor Models

#### Elad Alon Dept. of EECS

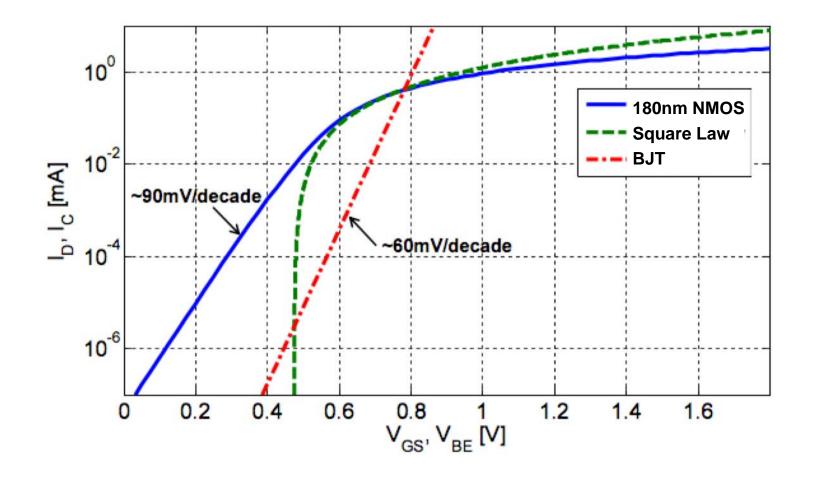

### **Square Law Model?**

$$I_{D,sat} = \frac{1}{2} \cdot \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot \left(V_{GS} - V_{th}\right)^2$$

#### • Assumptions made to come up with this model:

- Charge density determined only by vertical field

- Drift velocity set only by lateral field

- Neglects diffusion currents ("magic" Vth)

- Constant mobility

- And about 10<sup>2</sup> 10<sup>3</sup> more parameters in a real SPICE model...

# Graphically

[B. Murmann]

Lecture 2

# **Better Hand Models?**

- There are better (less inaccurate) "hand" models out there

- Velocity saturation

- Alpha-power law

- EKV

- ...

- But all of them either (1) neglect certain effects or (2) are too unwieldy to be useful for hand analysis

- This is particularly true if you want to say anything about r<sub>o</sub> (which we do typically care about in analog)

# Taking a Step Back

- Reminder: the model you use should be tailored to the question you are trying to answer

- "Hand" models are good for building intuition, and to a lesser extent, checking reasonableness of simulation results

- <u>Simulation</u> models are the ones you will have to use to "sign off" on your design

- So our design methodology should be using the results from the full simulation models too

# **Basic Small Signal Transistor Model** (for Design)

# Biasing...

- In quadratic model,  $V_{od} = (V_{GS} V_{TH})$  told us a lot about important biasing tradeoffs:

- $g_m = 2*I_D/V_{od}$

- $r_o$  "large" for  $V_{DS} > V_{od}$

- "Boundary between saturation and triode"

•

$$\omega_{\rm T} = g_{\rm m}/C_{\rm gg} \propto V_{\rm od}$$

- But real transistors clearly aren't quadratic

- And even worse, there is no way to actually measure V<sub>od</sub>

- Idea: work with a new (measurable) transistor

FoM inspired by V<sub>od</sub>...

EE 240B

Lecture 2

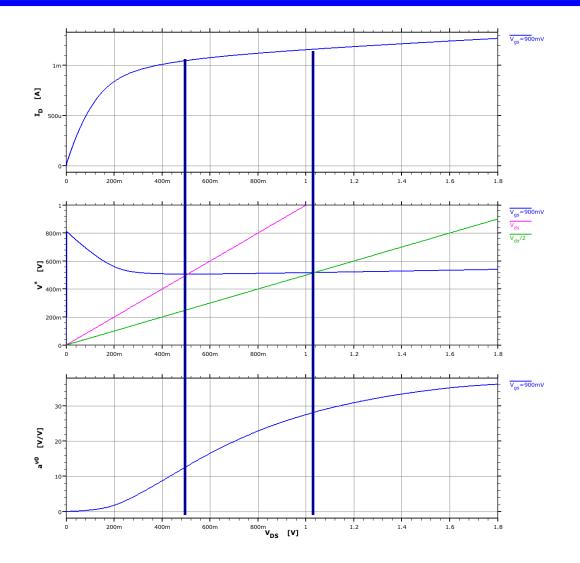

# Transistor FoM #1: V\* (g<sub>m</sub>/I<sub>D</sub>)

• Define:

$$V^* = \frac{2I_D}{g_m} \qquad \Leftrightarrow \qquad \frac{g_m}{I_D} = \frac{2}{V^*}$$

e.g. V<sup>\*</sup> = 200mV

$$\rightarrow$$

g<sub>m</sub>/I<sub>D</sub> = 10 V<sup>-1</sup>

- Inspired by the fact that  $V^* = V_{od}$  for square law

- Devices definitely not square law, but can measure V\*

- It will (by definition) set current efficiency

- And (approximately) give you insight in to other parameters (r<sub>o</sub>,  $\omega_T$ , etc.)

## **Simplest Possible Usage of V\***

## **Simplest Possible Usage of V\***

#### **"Best" Possible V\*?**

# **Tradeoff for Low V\***

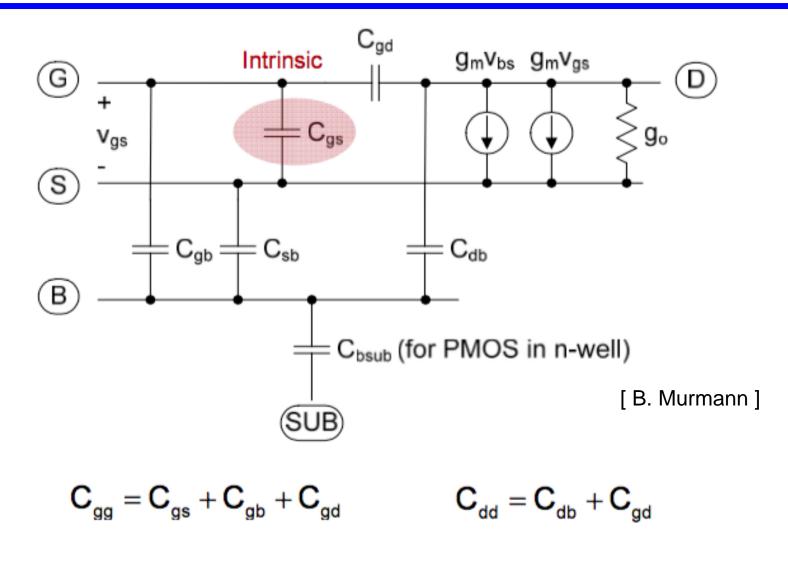

# Transistor FoM #2: ω<sub>T</sub>

- Reminder:  $\omega_T$  defined by  $||i_g(\omega_T)|| = ||i_d(\omega_T)||$

- Measureable both in simulation and in hardware

- In our simplified small-signal model,  $\omega_T = g_m/C_{gg}$

- (C<sub>dd</sub> usually some fixed multiple relative to C<sub>gg</sub>, so  $\omega_T$  is a good FoM to capture this too.)

- Lower V\* results in better current efficiency, but lower  $\omega_{\text{T}}$

- Best balance depends on transistor characteristics, desired gain-bandwidth

- More on that next lecture

# What About L?

• How does transistor L affect V\*?

• How does transistor L affect  $\omega_T$ ?

# Transistor FoM #3: a<sub>v0</sub>

- Most of the time you don't actually care about value of r<sub>o</sub> itself

- Just care about how it impacts circuit-level specifications

- Most commonly, gain (A<sub>V</sub>)

- So, often use intrinsic gain  $a_{v0} = g_m^* r_o$  instead

- Still measurable (from I-V curves) in both simulation and hardware

# Example Usage of $a_{v0}$

## Intrinsic Gain vs. L

Lecture 2

# Intrinsic Gain vs. V<sub>DS</sub>

Lecture 2

### Loose End #1

- Talked about transistors so far as if they all have the same FoMs for given W, L, V<sub>GS</sub>, V<sub>DS</sub>, ...

- If you have 5 billion transistors on a single chip, do you think all of those transistors behave exactly the same?

- If you ship 100 million chips, do you think all of those chips will have the same specifications?

#### **Process Corners**

#### Loose End #2

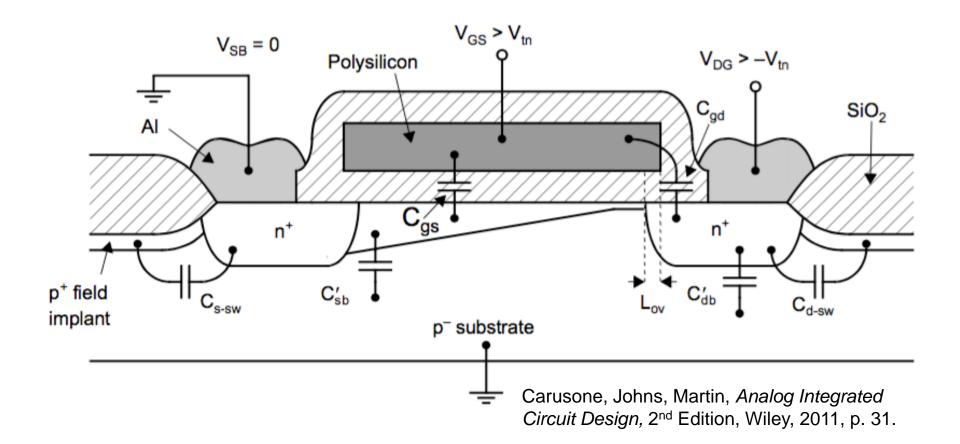

# **Small Signal Capacitances**

|                 | Subthreshold                       | Triode                                | Saturation                             |

|-----------------|------------------------------------|---------------------------------------|----------------------------------------|

| C <sub>GS</sub> | C <sub>ol</sub>                    | C <sub>GC</sub> /2 + C <sub>ol</sub>  | 2/3 C <sub>GC</sub> + C <sub>ol</sub>  |

| C <sub>GD</sub> | C <sub>ol</sub>                    | $C_{GC}/2 + C_{ol}$                   | C <sub>ol</sub>                        |

| C <sub>GB</sub> | C <sub>GC</sub>    C <sub>CB</sub> | 0                                     | 0                                      |

| C <sub>SB</sub> | C <sub>jSB</sub>                   | C <sub>jsB</sub> + C <sub>CB</sub> /2 | C <sub>jsB</sub> + 2/3 C <sub>CB</sub> |

| C <sub>DB</sub> | C <sub>jDB</sub>                   | C <sub>jDB</sub> + C <sub>CB</sub> /2 | C <sub>jDB</sub>                       |

$$C_{GC} = C_{ox}WL$$

$$C_{CB} = \frac{\mathcal{E}_{Si}}{x_d}WL$$

# "Complete" Small Signal Model

## **To Make Matters Worse...**

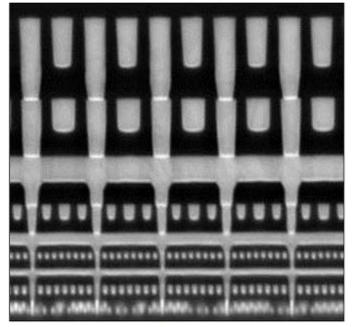

#### Interconnects

#### 22 nm Process

#### 14 nm Process

80 nm minimum pitch

52 nm (0.65x) minimum pitch

Image from Intel/www.legitreviews.com

#### "More Complete" Small Signal Model

#### So What Do We Do?

#### So What Do We Do?

# Final Note on Simplified Small Signal Model