#### EE247 Lecture 16

- D/A Converters (continued)

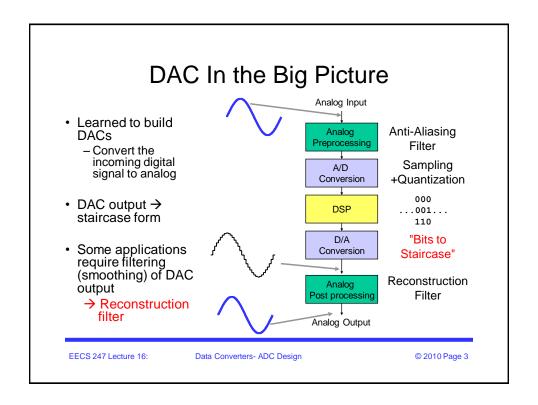

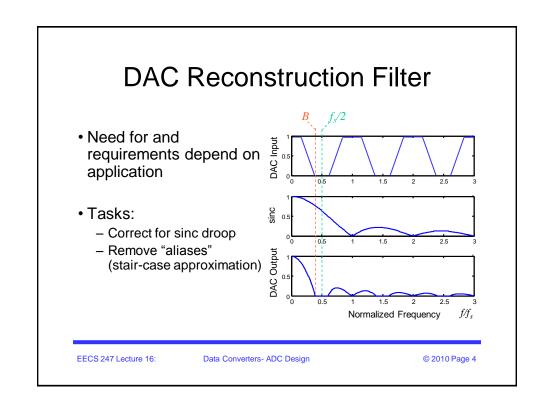

- DAC reconstruction filter

- ADC Converters

- Sampling

- · Sampling switch considerations

- Thermal noise due to switch resistance

- Clock jitter related non-idealities

- Sampling switch bandwidth limitations

- Switch conductance non-linearity induced distortion

- · Sampling switch conductance dependence on input voltage

- · Clock voltage boosters

- Sampling switch charge injection & clock feedthrough

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 1

#### **Summary Last Lecture**

- D/A converters

- Practical aspects of current-switched DACs (continued)

- Segmented current-switched DACs

- DAC dynamic non-idealities

- DAC design considerations

- Self calibration techniques

- Current copiers

- · Dynamic element matching

EECS 247 Lecture 16:

Data Converters- DAC Design

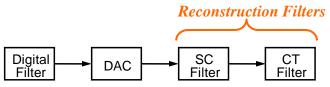

#### **Reconstruction Filter Options**

- · Reconstruction filter options:

- Continuous-time filter only

- -CT + SC filter

- SC filter possible only in combination with oversampling (signal bandwidth B <<  $f_{\rm s}/2)$

- · Digital filter

- Band limits the input signal → prevent aliasing

- Could also provide high-frequency pre-emphasis to compensate inband sinx/x amplitude droop associated with the inherent DAC S/H function

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 5

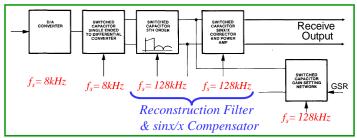

# DAC Reconstruction Filter Example: Voice-Band CODEC Receive Path

Note:

$$f_{sig}^{max} = 3.4kHz$$

$f_s^{DAC} = 8kHz$

$\Rightarrow sin(\pi f_{sig}^{max} x T_s)/(\pi f_{sig}^{max} x T_s)$

$= -2.75 dB droop due to DAC sinx/x shape$

Ref: D. Senderowicz et. al, "A Family of Differential NMOS Analog Circuits for PCM Codec Filter Chip," *IEEE Journal of Solid-State Circuits*, Vol.-SC-17, No. 6, pp.1014-1023, Dec. 1982.

EECS 247 Lecture 16:

Data Converters- ADC Design

# Summary D/A Converter

- D/A architecture

- Unit element complexity proportional to 2<sup>B</sup>- excellent DNL

- Binary weighted- complexity proportional to B- poor DNL

- Segmented- unit element MSB(B<sub>1</sub>)+ binary weighted LSB(B<sub>2</sub>)

- → Complexity proportional ((2<sup>B1</sup>-1) + B<sub>2</sub>) -DNL compromise between the two

- Static performance

- Component matching

- · Dynamic performance

- Time constants, Glitches

- DAC improvement techniques

- Symmetrical switching rather than sequential switching

- Current source self calibration

- Dynamic element matching

- Depending on the application, reconstruction filter may be needed

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 7

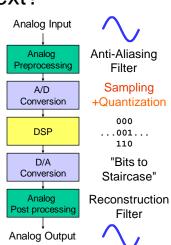

#### What Next?

- ADC Converters:

- Need to build circuits that "sample"

- Need to build circuits for amplitude quantization

EECS 247 Lecture 16:

Data Converters- ADC Design

## **Analog-to-Digital Converters**

- •Two categories:

- Nyquist rate ADCs →  $f_{sig}^{max} \sim 0.5x f_{sampling}$

- Maximum achievable signal bandwidth higher compared to oversampled type

- Resolution limited to <14bits

- Oversampled ADCs →  $f_{sig}^{max}$  << 0.5 $xf_{sampling}$

- Maximum achievable signal bandwidth significantly lower compared to nyquist

- · Maximum achievable resolution high (18 to 20bits!)

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 9

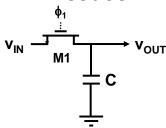

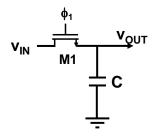

### **MOS Sampling Circuits**

EECS 247 Lecture 16:

Data Converters- ADC Design

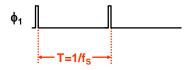

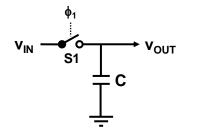

### Ideal Sampling

- In an ideal world, zero resistance sampling switches would close for the briefest instant to sample a continuous voltage v<sub>IN</sub> onto the capacitor C

- →Output Dirac-like pulses with amplitude equal to V<sub>IN</sub> at the time of sampling

- In practice not realizable!

V<sub>IN</sub> S1 C

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 11

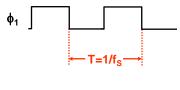

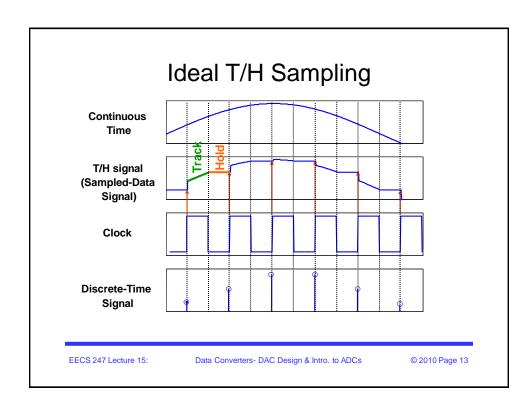

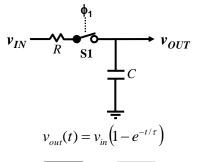

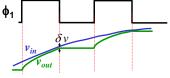

### Ideal Track & Hold Sampling

- $V_{\text{out}}$  tracks input for ½ clock cycle when switch is closed

- Ideally acquires exact value of  $V_{\text{in}}$  at the instant the switch opens

- "Track and Hold" (T/H) (often called Sample & Hold!)

EECS 247 Lecture 16:

Data Converters- ADC Design

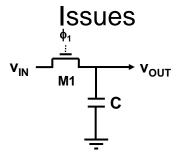

## Practical Sampling Issues

- Switch induced noise due to M1 finite channel resistance

- Clock jitter (edge variation of  $\phi_1$ )

- Finite  $R_{sw} \rightarrow$  limited bandwidth  $\rightarrow$  finite acquisition time

- $R_{sw} = f(V_{in}) \rightarrow \text{distortion}$

- · Switch charge injection & clock feedthrough

EECS 247 Lecture 16:

Data Converters- ADC Design

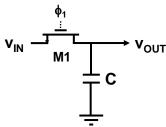

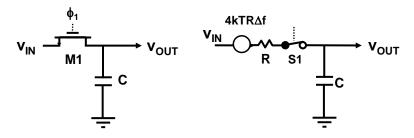

#### Sampling Circuit kT/C Noise

- · Switch resistance & sampling capacitor form a low-pass filter

- Noise associated with the switch resistance results in → Total noise variance= kT/C @ the output (see noise analysis in Lecture 1)

- In high resolution ADCs with such sampling circuit right at the input, kT/C noise at times dominates overall minimum signal handling capability (power dissipation considerations).

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 15

#### Sampling Network kT/C Noise

For ADCs sampling capacitor size is usually chosen based on having thermal noise smaller or equal or at times slightly larger compared to quantization noise: Assumption: → Nyquist rate ADC

For a Nyquist rate ADC: Total quantization noise power  $\approx \frac{\Delta^2}{12}$

Choose C such that thermal noise level is less (or equal) than Q noise

$$\frac{k_B T}{C} \le \frac{\Delta^2}{12}$$

$$\rightarrow \qquad C \ge 12k_B T \left(\frac{2^B - 1}{V_{FS}}\right)^2$$

$$\rightarrow \qquad C \ge 12k_B T \times \frac{2^{2B}}{V_{FS}^2}$$

EECS 247 Lecture 16:

Data Converters- ADC Design

#### Sampling Network kT/C Noise

$$C \ge 12k_B T \frac{2^{2B}}{V_{FS}^2}$$

| Required C <sub>min</sub> as a Function of ADC Resolution |                         |                           |

|-----------------------------------------------------------|-------------------------|---------------------------|

| В                                                         | $C_{min} (V_{FS} = 1V)$ | $C_{min} (V_{FS} = 0.5V)$ |

| 8                                                         | 0.003 pF                | 0.012 pF                  |

| 12                                                        | 0.8 pF                  | 2.4 pF                    |

| 14                                                        | 13 pF                   | 52 pF                     |

| 16                                                        | 206 pF                  | 824 pF                    |

| 20                                                        | 52,800 pF               | 211,200 pF                |

The large area required for  $C \Rightarrow$  limit highest achievable resolution for Nyquist rate ADCs

Oversampling results in reduction of required value for C (will be covered in oversampled converter lectures)

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 17

# Practical Sampling Issues

- Switch induced noise due to M1 finite channel resistance

- ➡• Clock jitter (edge variation of \$\phi\_1\$)

- Finite  $R_{sw}$   $\Rightarrow$  limited bandwidth  $\Rightarrow$  finite acquisition time

- $R_{sw} = f(V_{in}) \rightarrow \text{distortion}$

- · Switch charge injection & clock feedthrough

EECS 247 Lecture 16:

Data Converters- ADC Design

### **Clock Jitter**

- So far: clock signal controls sampling instants which we assumed to be precisely equi-distant in time (period T)

- Real clock generator → some level of variability

- Variability in T causes errors

- "Aperture Uncertainty" or "Aperture Jitter"

- What is the effect of clock jitter on ADC performance?

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 19

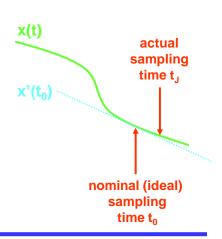

### **Clock Jitter**

• Sampling jitter adds an error voltage proportional to the product of  $(t_J-t_0)$  and the derivative of the input signal at the sampling instant

EECS 247 Lecture 16:

Data Converters- ADC Design

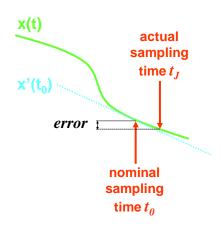

### **Clock Jitter**

• The error voltage is

$$e = x'(t_0)(t_J - t_0)$$

• Does jitter matter when sampling dc signals  $(x'(t_0)=0)$ ?

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 21

# Effect of Clock Jitter on Sampling of a Sinusoidal Signal

#### Sinusoidal input

Amplitude: A  $Frequency: f_x$

Jitter:

$x(t) = A \sin\left(2\pi f_x t\right)$

$x'(t) = 2\pi f_x A \cos(2\pi f_x t)$  $|x'(t)|_{max} \le 2\pi f_x A$

Then:

$|e(t)| \le |x'(t)|_{max} dt$

$|e(t)| \le 2\pi f_x A dt$

#### Worst case

$$A = \frac{A_{FS}}{2} \qquad f_x = \frac{f_s}{2}$$

$$|e(t)| << \frac{\Delta}{2} \cong \frac{A_{FS}}{2^{B+I}}$$

$$dt << \frac{1}{2^B \pi f_s}$$

| # of Bits | $f_s$    | dt <<   |

|-----------|----------|---------|

| 12        | 1 MHz    | 78 ps   |

| 16        | 20 MHz   | 0.24 ps |

| 12        | 1000 MHz | 0.07 ps |

EECS 247 Lecture 16:

Data Converters- ADC Design

## Statistical Jitter Analysis

- The worst case looks pretty stringent ... what about the "average"?

- Let's calculate the mean squared jitter error (variance)

- If we're sampling a sinusoidal signal

$$x(t) = A\sin(2\pi f_x t),$$

then

- $x'(t) = 2\pi f_x A\cos(2\pi f_x t)$

- $E\{[x'(t)]^2\} = 2\pi^2 f_x^2 A^2$

- Assume the jitter has variance  $E\{(t_1-t_0)^2\} = \tau^2$

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 23

## Statistical Jitter Analysis

- If x'(t) and the jitter are independent

E{[x'(t)(t<sub>1</sub>-t<sub>0</sub>)]<sup>2</sup>} = E{[x'(t)]<sup>2</sup>} E{(t<sub>1</sub>-t<sub>0</sub>)<sup>2</sup>}

- Hence, the jitter error power is  $\mathbf{E}\{\mathbf{e}^2\} = 2\pi^2 \mathbf{f_x}^2 \mathbf{A}^2 \tau^2$

- If the jitter is uncorrelated from sample to sample, this "jitter noise" is white

EECS 247 Lecture 16:

Data Converters- ADC Design

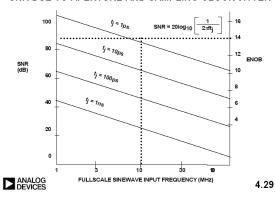

## Statistical Jitter Analysis

#### SNR DUE TO APERTURE AND SAMPLING CLOCK JITTER

$$\begin{split} DR_{\text{jitter}} &= \frac{A^2/2}{2\pi^2 f_x^2 A^2 \tau^2} \\ &= \frac{1}{2\pi^2 f_x^2 \tau^2} \\ &= -20 \log_{10} (2\pi f_x \tau) \end{split}$$

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 25

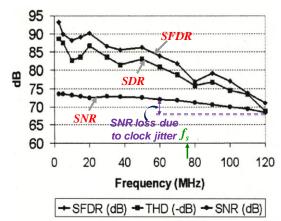

### **Example: ADC Spectral Tests**

Ref: W. Yang et al., "A 3-V 340-mW 14-b 75-Msample/s CMOS ADC with 85-dB SFDR at Nyquist input," *IEEE J. of Solid-State Circuits*, Dec. 2001

EECS 247 Lecture 15:

Data Converters- DAC Design & Intro. to ADCs

# Summary Effect of Clock Jitter on ADC Performance

- In cases where clock signal is provided from off-chip→ have to choose a clock signal source with low enough jitter

- On-chip precautions to keep the clock jitter less than single-digit pico-second:

- Separate supplies as much as possible

- Separate analog and digital clocks

- Short on-chip inverter chains between clock source and destination

- Few, if any, other analog-to-digital conversion non-idealities have the same symptoms as sampling jitter:

- RMS noise proportional to input signal frequency

- RMS noise proportional to input signal amplitude

- →In cases where clock jitter limits the dynamic range, it's easy to tell, but may be difficult to fix...

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 27

## Practical Sampling Issues

- · Switch induced noise due to M1 finite channel resistance

- Clock jitter (edge variation of φ<sub>1</sub>)

- $\Rightarrow$  Finite  $R_{sw} \Rightarrow$  limited bandwidth  $\Rightarrow$  finite acquisition time

- $R_{sw} = f(V_{in}) \rightarrow \text{distortion}$

- · Switch charge injection & clock feedthrough

EECS 247 Lecture 16:

Data Converters- ADC Design

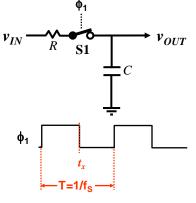

#### Sampling Acquisition Bandwidth

The resistance R of switch S1 turns the sampling network into a lowpass filter with finite time constant:

$$\tau = RC$$

- Assuming  $V_{\it in}$  is constant or changing slowly during the sampling period and C is initially discharged

- Need to allow enough time for the output to settle to less than 1 ADC LSB → determines minimum duration for \$\phi\_1\$ or maximum ADC operating freq.

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 29

#### Sampling: Effect of Finite Switch On-Resistance

$$\begin{aligned} & V_{in}^{tx} - V_{out}^{tx} << \Delta \quad \text{since } V_{out} = V_{in} \left( 1 - e^{-t/\tau} \right) \\ & \rightarrow V_{in} e^{-T_s/2\tau} << \Delta \ or \ \tau << \frac{T_s}{2} \frac{1}{\ln \left( V_{in} / \Delta \right)} \end{aligned}$$

Worst Case:  $V_{in} = V_{FS}$

$$\tau \ll \frac{T_s}{2} \frac{1}{\ln(2^B - 1)} \approx \frac{0.72 \times T_s}{B}$$

$$R \ll \frac{1}{2f_s C} \frac{1}{\ln(2^B - 1)} \approx \frac{0.72}{Bf_s C}$$

#### Example:

$$B = 14$$

,  $C_{min} = 13pF$ ,  $f_s = 100MHz$

$T_s/\tau >> 19.4$ , or  $10\tau << T_{s}/2$   $\rightarrow R << 40 \Omega$

EECS 247 Lecture 16:

Data Converters- ADC Design

### **Practical Sampling** Issues

- · Switch induced noise due to M1 finite channel resistance

- Clock jitter (edge variation of φ<sub>1</sub>)

- Finite  $R_{sw}

ightarrow$  limited bandwidth ightarrow finite acquisition time

Switch charge injection & clock feedthrough

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 31

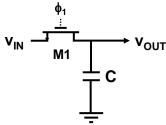

#### Non-Linear Switch On-Resistance

Switch→ MOS operating in triode mode:

$$I_{D(triode)} = \mu C_{ox} \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \right) V_{DS}, \qquad \frac{1}{R_{ON}} \cong \frac{dI_{D(triode)}}{dV_{DS}} \bigg|_{V_{DS} \to 0}$$

$$R_{ON} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{DD} - V_{th} - V_{in})}$$

Let us call

$$R @ V_{in} = 0$$

$R_o$  then  $R_o = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{DD} - V_{th})}$

$$R_{ON} = \frac{R_o}{1 - \frac{V_{in}}{V_{DD} - V_i}}$$

EECS 247 Lecture 16:

Data Converters- ADC Design

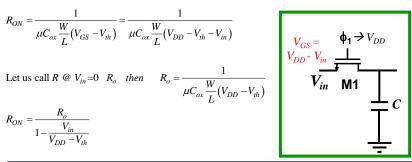

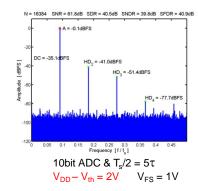

### Sampling Distortion

Simulated 10-Bit ADC & Sampling Switch modeled:

$$v_{out} = v_{in} \left( I - e^{-\frac{T}{2\tau} \left( I - \frac{V_{in}}{V_{DD} - V_{th}} \right)} \right)$$

$$T_{s}/2 = 5\tau$$

$$V_{DD} - V_{th} = 2V$$

$$V_{FS} = IV$$

→Results in

HD2=-41dBFS & HD3=-51.4dBFS

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 33

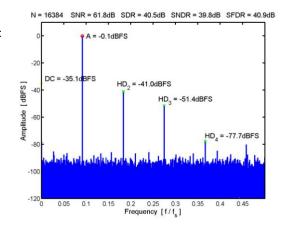

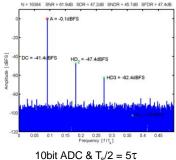

#### Sampling Distortion

Doubling sampling time (or ½ time constant)

Results in:

HD2 improved from -41dBFS to -70dBFS ~30dB

HD3 improved from - 51.4dBFS to -76.3dBFS ~25dB

Allowing enough time for the sampling network settling → Reduces distortion due to switch R non-linear behavior to a tolerable

10bit ADC  $T_{s}/2 = 10 \tau$

$V_{DD} - V_{th} = 2V$   $V_{FS} = IV$

EECS 247 Lecture 16:

Data Converters- ADC Design

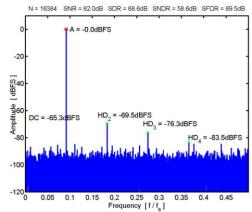

#### Sampling Distortion Effect of Supply Voltage

- 10bit ADC &  $T_s/2 = 5\tau$  $V_{DD} - V_{th} = 4V$   $V_{FS} = 1V$

- · Effect of higher supply voltage on sampling distortion

- $\rightarrow$  HD3 decreased by  $(V_{DD1}/V_{DD2})^2$

- $\rightarrow$  HD2 decreased by  $(V_{DD1}/V_{DD2})$

EECS 247 Lecture 16:

Data Converters- ADC Design

© 2010 Page 35

#### Sampling Distortion

- SFDR → sensitive to sampling distortion - improve linearity by:

- $\bullet$  Larger  $V_{DD}/V_{FS}$

- Higher sampling bandwidth

- Solutions:

- Overdesign→ Larger switches Issue:

- → Increased switch charge injection

- → Increased nonlinear S &D junction cap.

- $\bullet \ {\rm Maximize} \ V_{DD} \! / \! V_{FS}$

- $\rightarrow$ Decreased dynamic range if  $V_{DD}$  const.

- · Complementary switch

- Constant & max.  $V_{GS} \neq f(V_{in})$

$$\begin{array}{ll} 10bit \ ADC & T_s/\tau = \textbf{20} \\ V_{DD} - V_{th} = 2V & V_{FS} = 1V \end{array}$$

EECS 247 Lecture 16:

Data Converters- ADC Design

#### **Practical Sampling** Summary So Far!

kT/C noise

$$C \ge 12k_B T \frac{2^{2B}}{V_{FS}^2}$$

• Finite  $R_{sw} \rightarrow$  limited bandwidth

$$R << \frac{0.72}{B f_s C}$$

•  $g_{sw} = f(V_{in}) \rightarrow \text{distortion}$

$$\begin{split} g_{\mathit{ON}} &= g_o \bigg( 1 - \frac{V_{in}}{V_{\mathit{DD}} - V_{\mathit{th}}} \bigg) \quad \text{for} \quad \ g_o = \mu C_{ox} \frac{W}{L} \big( V_{\mathit{DD}} - V_{\mathit{th}} \big) \end{split}$$

• Allowing long enough settling time  $\Rightarrow$  reduce distortion due to

sw non-linear behavior

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 37

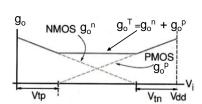

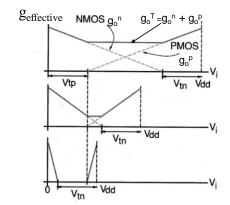

#### Sampling Use of Complementary Switches

- Complementary n & p switch advantages:

- ✓Increase in the overall conductance → lower time constant

- $\checkmark$ Linearize the switch conductance for the range  $|V_{th}^{p}|$ < Vin < Vdd - $|V_{th}^{n}|$

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

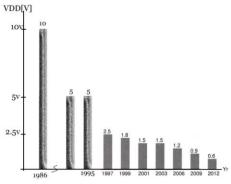

#### Complementary Switch Issues Supply Voltage Evolution

- · Supply voltage has scaled down with technology scaling

- · Threshold voltages do not scale accordingly

Ref: A. Abo et al, "A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter," JSSC May 1999, pp. 599.

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 39

# Complementary Switch Effect of Supply Voltage Scaling

•As supply voltage scales down input voltage range for constant  $g_o$  shrinks  $\rightarrow$  Complementary switch not effective when  $V_{DD}$  becomes comparable to  $2xV_{th}$

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

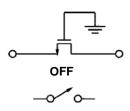

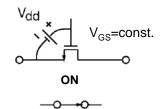

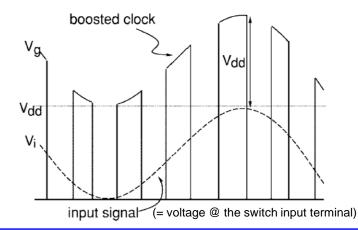

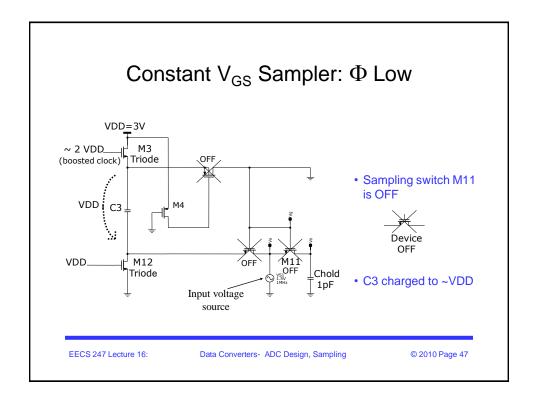

### Boosted & Constant V<sub>GS</sub> Sampling

- Gate voltage  $V_{GS}$  =low

- > Device off

- ➤ Beware of signal feedthrough due to parasitic capacitors

- Increase gate overdrive voltage as much as possible + keep V<sub>GS</sub> constant

- > Switch overdrive voltage independent of signal level

- ➤ Error due to finite R<sub>ON</sub> linear (to 1st order)

- ightharpoonup Lower time constant

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 41

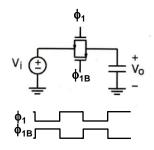

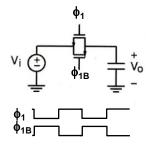

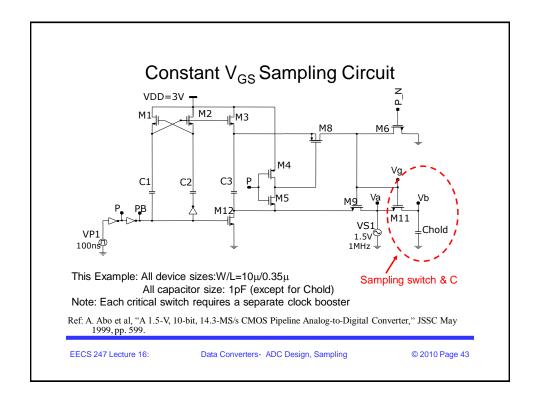

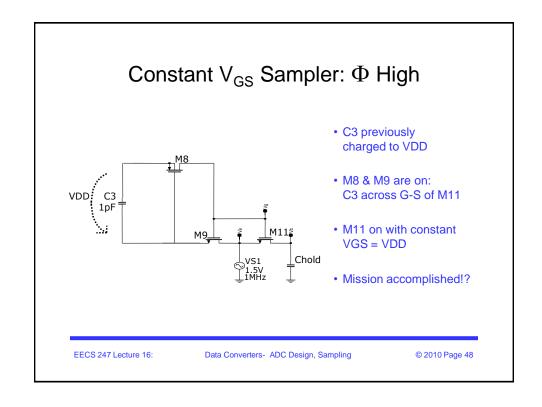

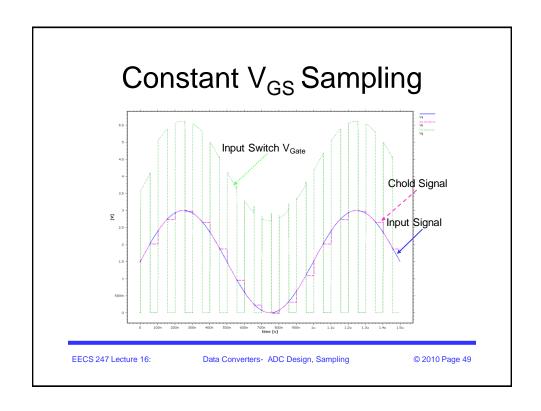

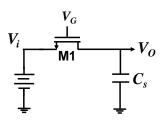

# Constant V<sub>GS</sub> Sampling

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

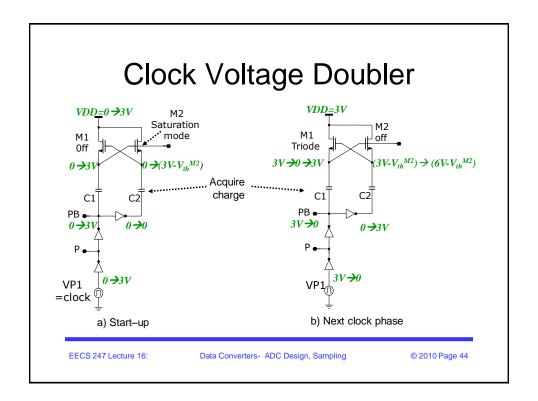

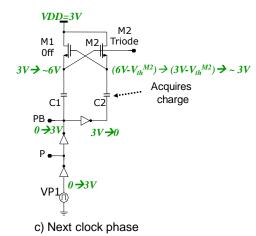

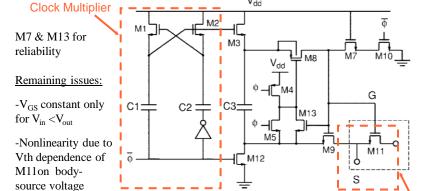

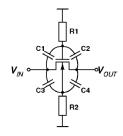

## Clock Voltage Doubler

- Both C1 & C2

→ charged to

VDD after 1.5

clock cycle

- Note that bottom plate of C1 & C2 is either 0 or VDD while top plates are at VDD or 2VDD

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

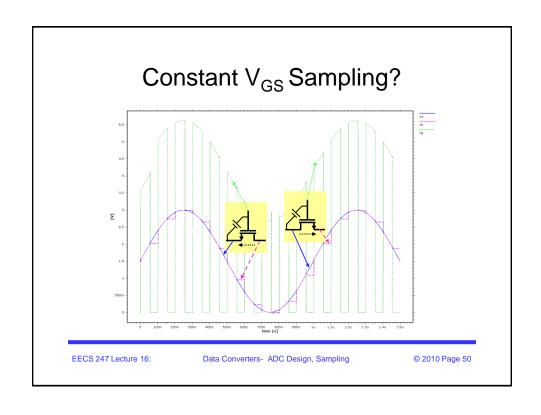

#### Constant V<sub>GS</sub> Sampling?

- During the time period: V<sub>in</sub>< V<sub>out</sub>

- → V<sub>GS</sub>=constant=V<sub>DD</sub>

- Larger V<sub>GS</sub>-V<sub>th</sub> compared to no boost

- V<sub>GS</sub>=cte and not a function of input voltage

→ Significant linearity

- → Significant linearity improvement

- During the time period:  $V_{in} > V_{out}$ :

- $\rightarrow$  V<sub>GS</sub>= V<sub>DD</sub> IR

- $\hbox{-} \ \, \text{Larger} \ \, \text{V}_{\text{GS}} \hbox{-} \text{V}_{\text{th}} \ \, \text{compared to} \\ \text{no boost}$

- V<sub>GS</sub> is a function of IR and hence input voltage

- → Linearity improvement not as pronounced as for V<sub>in</sub>< V<sub>out</sub>

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 51

# Boosted Clock Sampling Complete Circuit

Ref: A. Abo et al, "A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter," JSSC May 1999, pp. 599.

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

#### Boosted Clock Sampling Design Consideration

Choice of value for C3:

• C3 too large → large charging current → large dynamic power dissipation

• C3 too small →

Vgate-Vs=

VDD.C3/(C3+Cx)

→ Loss of VGS due to low

ratio of Cx/C3 Cx includes C<sub>GS</sub> of M11 plus

all other parasitics caps....

Ref: A. Abo et al, "A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter," JSSC

EECS 247 Lecture 16:

May 1999, pp. 599.

Data Converters- ADC Design, Sampling

M9<u>-</u>

© 2010 Page 53

Chold

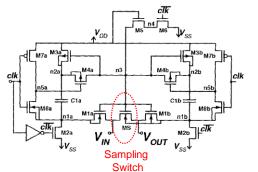

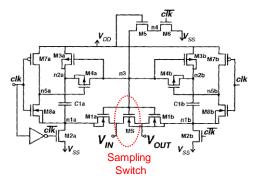

### Advanced Clock Boosting Technique

Ref: M. Waltari et al., "A self-calibrated pipeline ADC with 200MHz IFsampling frontend," ISSCC 2002, Dig. Tech. Papers, pp. 314

Two floating voltages sources generated and connected to Gate and S & D

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

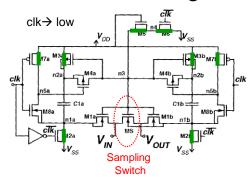

### Advanced Clock Boosting Technique

- clk→ low

- Capacitors C1a & C1b → charged to VDD

- MS → off

- Hold mode

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 55

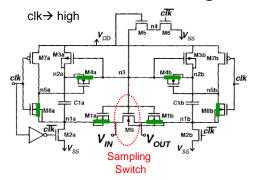

### Advanced Clock Boosting Technique

- clk→ high

- Top plate of C1a & C1b connected to gate of sampling switch

- Bottom plate of C1a connected to V<sub>IN</sub>

- Bottom plate of C1b connected to V<sub>OUT</sub>

- − VGS & VGD of MS both @ VDD & ac signal on G of MS  $\rightarrow$  average of V<sub>IN</sub> & V<sub>OLIT</sub>

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

### Advanced Clock Boosting Technique

Ref: M. Waltari et al., "A self-calibrated pipeline ADC with 200MHz IFsampling frontend," ISSCC 2002, Dig. Tech. Papers, pp. 314

- Gate tracks *average* of input and output, reduces effect of I-R drop at high frequencies

- Bulk also tracks signal  $\Rightarrow$  reduced body effect (technology used allows connecting bulk to S)

- Reported measured SFDR = 76.5dB at f<sub>in</sub>=200MHz

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 57

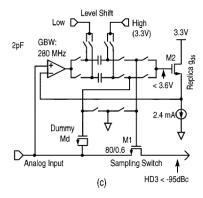

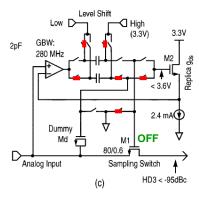

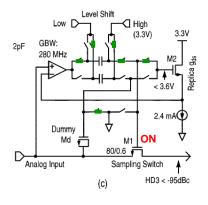

#### **Constant Conductance Switch**

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB SFDR," IEEE J. Solid-State Circuits, pp. 1769-1780, Dec. 2000

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

### **Constant Conductance Switch**

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB SFDR," *IEEE J. Solid-State Circuits*, pp. 1769-1780, Dec. 2000

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 59

#### **Constant Conductance Switch**

- M2→ Constant current

- → constant g<sub>ds</sub>

- M1→ replica of M2 & same VGS

- as M2

- → M1 also

- constant  $g_{\rm ds}$

- · Note: Authors report requirement of 280MHz GBW for the opamp for 12bit 50Ms/s ADC

- Also, opamp common-mode compliance for full input range required

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB SFDR," *IEEE J. Solid-State Circuits*, pp. 1769-1780, Dec. 2000

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

#### Switch Off-Mode Feedthrough Cancellation

High-pass feedthrough paths past an open switch

Feedthrough cancellation with a dummy switch

Ref: M. Waltari et al., "A self-calibrated pipeline ADC with 200MHz IF-sampling frontend," ISSCC 2002, Dig. Techn. Papers, pp. 314

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 61

## **Practical Sampling**

- Switch induced noise due to M1 finite channel resistance

- · Clock jitter

- Finite  $R_{sw} \rightarrow$  limited bandwidth  $\rightarrow$  finite acquisition time

- $R_{sw} = f(V_{in}) \rightarrow \text{distortion}$

Switch charge injection & clock feedthrough

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

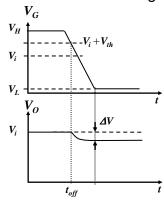

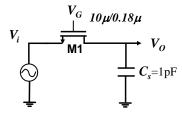

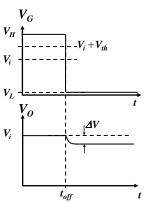

# Sampling Switch Charge Injection & Clock Feedthrough Switching from Track to Hold

- First assume  $V_i$  is a DC voltage

- When switch turns off  $\rightarrow$  offset voltage induced on  $C_s$

- Why?

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 63

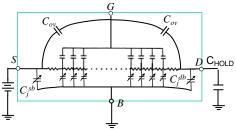

# Sampling Switch Charge Injection

MOS xtor operating in triode region Cross section view

S G D

Distributed channel resistance & gate & junction capacitances

- Channel → distributed RC network formed between G,S, and D

- Channel to substrate junction capacitance → distributed & voltage dependant

- Drain/Source junction capacitors to substrate → voltage dependant

- Over-lap capacitance  $C_{ov} = L_D x W x C_{ox}$  associated with G-S & G-D overlap

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

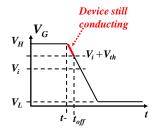

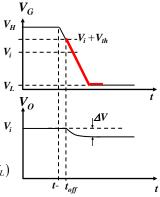

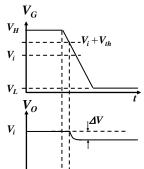

# Switch Charge Injection Slow Clock

- Slow clock → clock fall time >> device speed

- ightarrow During the period (t- to  $t_{o\!f\!f}$ ) current in channel discharges channel charge into low impedance signal source

- Only source of error  $\rightarrow$  Clock feedthrough from  $C_{ov}$  to  $C_s$

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 65

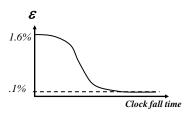

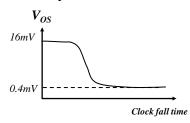

# Switch Clock Feedthrough Slow Clock

where  $\varepsilon = -\frac{C_{ov}}{C_s}$ ;  $V_{os} = -\frac{C_{ov}}{C_s} (V_{th} - V_L)$

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

# Switch Charge Injection & Clock Feedthrough Slow Clock- Example

$$\begin{split} &C_{ov}^{'}=0.1fF/\mu \quad C_{ox}=9fF/\mu^2 \quad V_{th}=0.4V \quad V_L=0 \quad \\ &\varepsilon=-\frac{C_{ov}}{C_s}=-\frac{10\mu x 0.1fF/\mu}{1pF}=-.1\% \\ &Allowing \ \varepsilon=1/2LSB \rightarrow ADC \ resolution <\sim 9bit \end{split}$$

$$V_{os} = -\frac{C_{ov}}{C_s} (V_{th} - V_L) = -0.4 m V$$

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 67

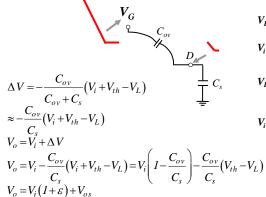

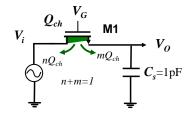

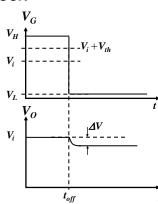

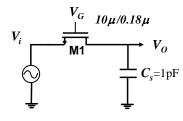

# Switch Charge Injection & Clock Feedthrough Fast Clock

Sudden gate voltage drop → no gate voltage to establish current in channel

→ channel charge has no choice but to escape out towards S & D

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

#### Switch Charge Injection & Clock Feedthrough Fast Clock

Clock Fall-Time << Device Speed:

$$\Delta V_{o} = -\frac{C_{ov}}{C_{ov} + C_{s}} (V_{H} - V_{L}) - \frac{1}{2} \times \frac{Q_{ch}}{C_{s}}$$

$$\approx -\frac{C_{ov}}{C_{ov} + C_{s}} (V_{H} - V_{L}) - \frac{1}{2} \times \frac{WC_{ox}L((V_{H} - V_{i} - V_{th}))}{C_{s}}$$

$$V_{o} = V_{i}(I + \varepsilon) + V_{os}$$

$$where \varepsilon = \frac{1}{2} \times \frac{WC_{ox}L}{C_{s}}$$

$$V_{os} = -\frac{C_{ov}}{C_{s}} (V_{H} - V_{L}) - \frac{1}{2} \times \frac{WC_{ox}L(V_{H} - V_{th})}{C_{s}}$$

- For simplicity it is assumed channel charge divided equally between S & D

- Source of error  $\rightarrow$  channel charge transfer + clock feedthrough via  $C_{ov}$  to  $C_s$

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 69

# Switch Charge Injection & Clock Feedthrough Fast Clock- Example

$$\begin{split} &C_{ov} = 0.1 \frac{fF}{\mu}, \ C_{ox} = 9 \frac{fF}{\mu^2}, V_{th} = 0.4 V, V_{DD} = 1.8 V, \ V_L = 0 \\ &\varepsilon = 1/2 \frac{WLC_{ox}}{C_s} = \frac{10 \mu x 0.18 \mu x 9 fF / \mu^2}{1pF} = 1.6 \% \rightarrow \sim 5 - bit \end{split}$$

$$V_{os} = -\frac{C_{ov}}{C_s} (V_H - V_L) - \frac{1}{2} \times \frac{WC_{ox}L(V_H - V_{th})}{C_s} = -1.8 mV - 14.6 mV = -16.4 mV$$

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

#### Switch Charge Injection & Clock Feedthrough **Example-Summary**

Error function of:

- → Clock fall time

- → Input voltage level

- → Source impedance

- → Sampling capacitance size

- → Switch size

8 Clock fall/rise should be controlled not to be faster (sharper) than necessary

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

© 2010 Page 71

#### Switch Charge Injection Error Reduction

- · How do we reduce the error?

- → Reduce switch size to reduce channel charge?

$$\Delta V_{o} = -\frac{1}{2} \frac{Q_{ch}}{C_{s}} \downarrow$$

$$\tau = R_{ON}C_{s} = \frac{C_{s}}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})} \uparrow \qquad (note: \frac{T_{s}}{2} = k\tau)$$

Consider the figure of merit (FOM):

$$FOM = \frac{1}{\tau \times \Delta V_o} \approx \frac{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})}{C_s} \times 2 \times \frac{C_s}{W C_{ox} L ((V_H - V_i - V_{th}))}$$

- $\rightarrow FOM \propto \mu/L^2$

- ❖ Reducing switch size increases τ → increased distortion→ not a viable solution

- ❖ Small  $\tau$  and small  $\Delta V$  → use minimum channel length (mandated by technology)

- For a given technology τ x ΔV ~ constant

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling

# Sampling Switch Charge Injection & Clock Feedthrough Summary

- Extra charge injected onto sampling capacitor @ switch device turn-off

- -Channel charge injection

- -Clock feedthrough to C<sub>s</sub> via C<sub>ov</sub>

- Issues due to charge injection & clock feedthrough:

- -DC offset induced on hold C

- –Input dependant error voltage → distortion

- Solutions:

- -Slowing down clock edges as much as possible

- -Complementary switch?

- -Addition of dummy switches?

- -Bottom-plate sampling?

EECS 247 Lecture 16:

Data Converters- ADC Design, Sampling